Од СП

vj to

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием | 1990 |

|

SU1709537A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| Адаптивный цифровой групповой приемник сигналов управления и взаимодействия с дельта - модуляцией | 1990 |

|

SU1800658A1 |

| АНАЛОГО-ЦИФРОВОЕ МНОГОПРОЦЕССОРНОЕ УСТРОЙСТВО ВЫЧИСЛЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2006 |

|

RU2333531C1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Преобразователь импульсно-кодомодулированных сигналов в дельта-модулированные сигналы | 1985 |

|

SU1264347A1 |

| Адаптивный телевизионный дельта-кодер | 1989 |

|

SU1690199A1 |

| Устройство для ввода аналоговой информации | 1989 |

|

SU1672434A1 |

Изобретение относится к автоматике, телемеханике и может использоваться в адаптивных телеметрических системах. Устройство осуществляет преобразование в дискретные моменты времени входного аналогового сигнала в код, запоминание существенных значений выборок преобразованного сигнала и выдачу запомненных существенных выборах по запросу на выходы 18, что уменьшает информационную избыточность преобразуемого сигнала и повышает информативность устройства. Устройство содержит компаратор 1, элементы НЕ 2, 10, элементы И 3, 4, 9, 13, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 5, триггер 6, счетчики 7, 11, цифроаналоговый преобразователь 8, блок 12 оперативной памяти, информационные и тактовые входы 14, 15 и 16, 17, информационные и управляющий выходы 18 и 19. 2 ил.

9мг.

Изобретение относится к автоматик Телемеханике и может использоваться |а адаптивных телеметрических систе- kax.

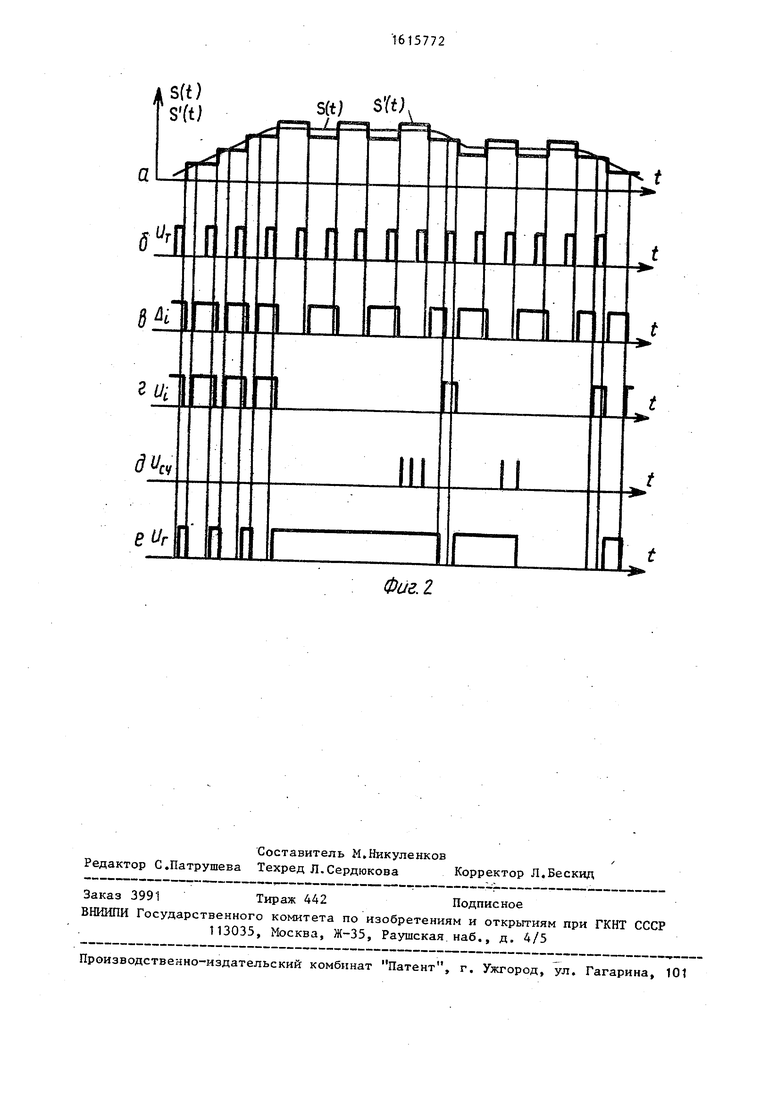

Цель изобретения - повышение инфор ативности устройства. ; На фиг,1 показана функциональная схема устройства; на фиг.2 - времен- ше диаграммы, пояснякяцие его работу

Устройство содержит (фиг.1) компа- атор 1, первый элемент НЕ 2, второй и первый элементы И 3 и 4, элемент ИСКЛЮЧАЙТЕ 5, триггер 6, пер- иый реверсивный счетчик 7, цифро- аналоговый преобразователь 8, третий :шемент И 9, второй элемент НЕ 10, иторой реверсивный счетчик 11, блок 2 -оперативной памяти, четвертый :элемент И 13, второй и первый инфор национные входы 14 и 15, первый и кторой тактовые входы 16 и 17, информационные и управляющий выходы 18 19. , ...

I Преобразование входного сигнала §(t) (фиг.2а) в двоичный код осуще- ётвляется методом следящего уравнове- цшвания, заключакщегося в поочередном Сравнении преобразуемого сигнала на i-M такте временной дискретизации ft суммой образцовых дискретных вели Чин, определяемой формулой

)&«кв1:кг2

0

1|де - величина шага квантования; I К- - коэффициент для двоичной I системы счисления, равный ; О или 1 в зависимости от

результатов сравнения на i-M такте временной дискретизации;

п - разрядность двоичного кода ,| преобразования; S (tj) - восстановленный аналоговый сигнал, соответствующий с заданной погрешностью входному на i-м такте временной дискретизации, В процессе преобразования сигнала S(t) формируется последовательность Дельта-сигналов uj (фиг.4в), которые формируются по правилу

при S(t) S (t); S(t):S (t).. Сигнал s (t) формируется цифроанало- говым преобразователем 8 (фиг.2а) из двоичного кода счетчика 7 разрядностью п и отражает исходньй сигнал

с

5 0

5

о

g

0

5

с заданной погрешностью. Величина этой погрешности определяется числом разрядов двоичного кода, используемого для восстановления сигнала S (t), и может регулироваться в необходимых пределах количеством разрядов двоичного кода, подаваемого с выхода счетчика 7 в цифроаналоговый преобразователь 8.

Для определения адаптивных выборок дельта-сигналы подвергаются логической обработке, в результате которой формируется сигнал UJ (фиг.2г) и. ГО приЛ; 7

1 при &., А;,,,

Темп обработки дельта-сигналов определяется входной тактовой частотой импульсов U-T (фиг.26), которая назначается с учетом динамических и частотных свойств преобразуемого сигнала.

Двоичные коды сформированных адаптивных выборок и коды времени, соответствующие моментам их формирования, записываются в блок 12 памяти. Временная привязка адаптивных выборок при передаче их в асинхронном режиме позволяет восстанавливать ис- ходньй сигнал S(t) без искажений его формы.

Информационная емкость блока 12 завис1дт от. количества запоминаемых адаптивных выборок в течение отрезка времени, определяемого внешним устройством, погрешности преобразования, опредепяемой количеством разрядов счетчика 7, и точности временной привязки, определяемой количеством разрядов кода времени на входе 14.

Для вь1дачи кодов преобразованного сигнала S(t) из блока 12 на выходы 18 на вход 17 поступают импульсы считывания (фи.г.2д)5 которые формируются внешним устройством при наличии сигнала готовности на выходе 19 Up (фиг.2е). В свою очередь, сигнал готовности Up формируется только при наличии в блоке 12 двоичного кода хотя бы одной адаптивной выборки. При этом в моменты формирования и записи адаптивных выборок он не формируется, так как считывание информации из блока 12 в эти моменты времени приведет к потере формируемой адаптивной выборки.

Устройство работает следующим образом.

5

. Сигнал S(t) с входа 15 поступает на первый вход компаратора 1, на второй вход которого подается восстановленный сигнал St(t), отображакнций входной сигнал S(t) с требуемой точ- ностью. Компаратор 1 сравнивает сигналы S(t), S (t) и в зависимости от результатов сравнения на, его выходе фop шpyютcя дельта-сигналы; , если S(t)(t), , если S(t) S (t) , Предположим, что сигнал S(t) S (t), тогда сигнал с выхода компаратора 1 открывает элемент И 4 и обеспечивает поступление с входа 16 тактовых импульсов на инкрементирующий вход счетчика 7, увел ичивая его содержимое. Если S(t) S (t), то на вькоде компаратора 1 формируется сигнал , который, инвертируясь элемедаом НЕ 2, открьша- ет элемент И 3, и тактовые импульсы поступают на декрементирующий вход счетчика 7, уменьшая его содержимое.

Таким образом, двоичный код в счет счетчике 7 в каждьй момент времени пропорционален входному сигналу S(t). Для формирования сигнала s (t) двоич- Н23Й код из счетчика 7 поступает в цифроаналог овый преобразователь 8, а также на информационные входы блока 12 оперативной памяти.

. Одновременно с преобразованием входного сигнала S(t) в двоичный код осуществляется логическая обработка дельта-сигналов А;. На информационный вход триггера 6 поступает последовательность дельта-сш налой, отображающих текущие изменения входного сигнала. По спаду очередного тактового импульса в триггере 6 запоминается предьщущее значение дельта-сигнала Д 1., и формируется сигнал Д; . Эти снх налы поступают на входы элемента 5 ИеКЛННАЮЩЕЕ ИЛИ-НЕ 5, на выходе кото- .рого формируется сигнал . При сов-г падении двух подряд следующих сигналов Д|, что соответствует изменению сигнала S(t) (4|, - го возрастанию, й-., - его убыванию), на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 5 появляется .единичньй логический уровень.При чередовании дельта-сигналов () на выходе элемента ИСКЛЮ- ЧАЮОЩЕ ШШ-т- 5 формируется нулевой логический уровень, свидетельствующий о том, что входной сигнал в данный момент эремени не изменяется и двоичный код регулярной выборки, находя

5

157726

щийся в данный момент времени в счет- |чике 7,является избыточным. Сигнал , поступая на вход блока 12, под- I держивает его в режиме считывания информации, и запись данного кода регулярной выборки в блок 12 не происходит. Сигнал 1 соответствует адаптивной выборке и, поступая на вход 0 блока 12, переводит его в режим записи информации. Фронтом тактового ш пульса, поступающего на вход 16, ДВОИЧНЫЙ код входного сигнала с выходов счетчика 7 и двоичный код вре- {5 мени с входа 14 записываются в ячейки блока 12 памяти по адресу, определяемому ДВОИЧНЫ кодом, поступающим с выходов счетчика 11.

После записи информации спадом 20 тактового импульса производится инк- рементирование адреса ячеек блока 12 памяти. Единичный сигнал поступает -на вход элемента И 9, и спад тактового импульса через открытьй 25 элемент И 9 поступает на инкременти- РУ1(щий вход счетчика 11. В результате двоичное число в счетчике 11 увеличивается на 1, подготавливая очередные ячейки блока 12 памяти к запи- 30 си двоичного кода последующей адаптивной выборки,,

Одновременно с логической обработкой дельта-сигналов и записью информации в блок 12 формируется сигнал готовности устройства U к ввдаче кодов входного сигнала из блока 12

на вькоды 181 Для этого на втором выходе счетчика 11 формируется единичньй сигнал; если в блоке 12 находится

40 код хотя бы одной адаптивной выборки. подлежа1Дс1Й вьщаче.-., В противHOMv ;y случае, когда на адресные входы блока 12 с первых выходов счетчика 11 поступает адрес нулевой ячейки, что ответствует отсутствию в блоке 12 кодов адаптивных выборок, на втором счетчике 11 формируется нулевой сигнал. Этот сигнал через элемент И 13 - поступает на выход 19. На друх-ой вход Q элемента И 13 через элемент НЕ tO

поступает сигнал , который запрещает прохождение сигнала с второго выхода счетчика 11 .в моменты формирования и записи адаптивных выборок. Сформированный сигнал готовности с выхода элемента И 13 поступает на выход 19, Таким образом, сигнал готовности формируется только в том случае, да в блоке 12 находится код хотя бы.

5

о|о;ной адаптивной выборки и когда от- сКстствует процесс формирования и за п|йси очередной адаптивной выборки. I Процесс накопления адаптивных вы- бЬрок с соответствуннцими им кодами времени в блоке 12 происходит до тех пор, пока на вход 17 не поступят импульсы считывания информации. Импуль сы считывания с входа 17 проходят на декрементирукяций вход счетчика 11 и уменьшают двоичное число в счетчике 11, обеспечивая обратное переключени адресов ячеек блока 12 памяти, в которых хранятся коды .предыдущих адап- тивных выборок. При этом коды адаптивных выборок из блока 12 поступают на выходы 18.

Процесс считывания происходит до тех пор, пока вся информация из блок 2 не будет вьвдана либо пока не начнется формирование очередной адаптивной выборки.

Таким образом, на выходах 18 по iкомандам оу внешнего устройства фор- iJDjpyioT двоичные коды значений входно о сигнала 8(1;), только в случае его возрастания или убьшания, что позво- |йяет уменьшить информационную избы- Чочность преобразуемого сигналаs а счет сохранения всех его сущеет- енных значений в блоке памяти повы- Ьить информативность устройства,

формула изобретения

I Устройство для адаптивного преоб- |разования аналоговых сигналов в код, Содержащее компаратор, первый вход которого является первым информагшон- |ным входом устройства, выход компара- fropa соединен непосредственно с ин-п Йюрмационным входом триггера, первым входом первого элемента И и через первый элемент НЕ с первым входо| второго элемента И выходы первого и второго элементов И соединены соот

5 O

5

45

ветственно с суммирующим и вычцтаю- щим входами первого счет.чика, выходы которого соединены с одноименными входами цифроаналогового преобразователя, выход которого соединен с вторым входом компаратора, третий и четвертьй элементы И, выход четвертого элемента И является управляющим выходом устройства, тактовый вход триггера объединен с вторыми входами первого и второго элементов И и является первым тактовым входом устройства, отличающееся тем, что, с целью повышения информативности устройства, в него введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, второй элемент НЕ, блок оперативной памяти и второй счетчик, вычитающий вход которого является вторым тактовым входом устройства, выход триггера соединен с пер--: вым входом элемента ИСКЛЮЧАКЩЕЕ ШИНЕ, второй вход которого подключен к выходу компаратора, выход элемента ИСГШЮЧАЩЕЕ ИЛИ-НЕ соединен непосред ственно с первым управляющим входом оперативной памяти, первым входом третьего элемента И и через второй эле,мент НЕ с первым входом четвертого элемента И, второй вход третьего элемента И объединен с, вторым управляю щим входом блока оперативной памяти и подключен к первому тактовому входу устройства, выход третьего элемента И соединен с суммирукщим входом второго счетчика, первые и второй выходы которого соединены соответственно с одноименными адресньпю входами блока оперативной памяти и вторым входом четвертого элемента И. первые и гвто- рые информационные входы блока оперативной ламяти соответственно являются вторьпуш информационными входами устройства и подключены к одноименным выходам первого счетчика, вькоды блока оперативной памяти являются информационными выходами устройства,

ASf Ч /

s(t; srt; 1

Фиг. г

| Устройство для передачи телеметрической информации со сжатием | 1983 |

|

SU1123045A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Анализатор активности непрерывных сигналов | 1984 |

|

SU1206958A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1990-12-23—Публикация

1989-04-18—Подача