00 (л 00 СА)

Изобретение относится к автоматике и вычислительной технике и может использоваться для преобразования огибающей радиосигналов в дельта-кодовые и импульсно-кодомодулированные (ИКМ) по- следовательности при спектральном и корреляционном анализе.

Цель изобретения - расширение области применения за счет преобразования огибающей входного сигнала в дельта-мо- дулированную и импульсно-кодомодулиро- ванную последовательности.

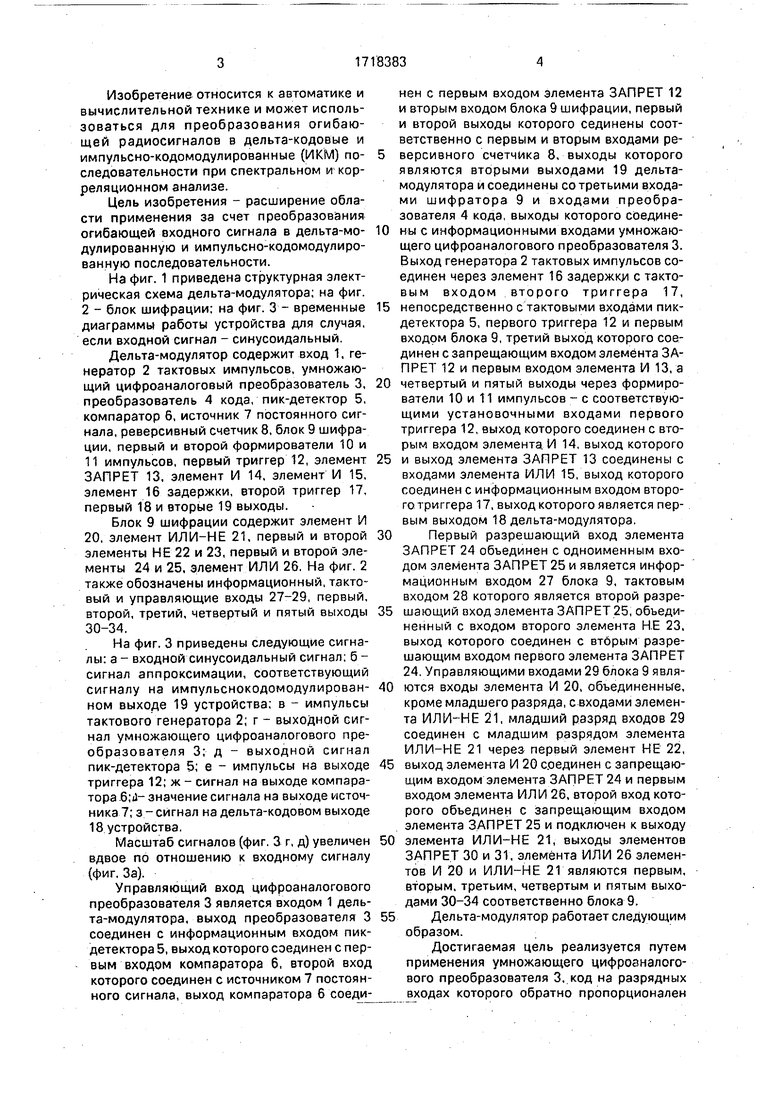

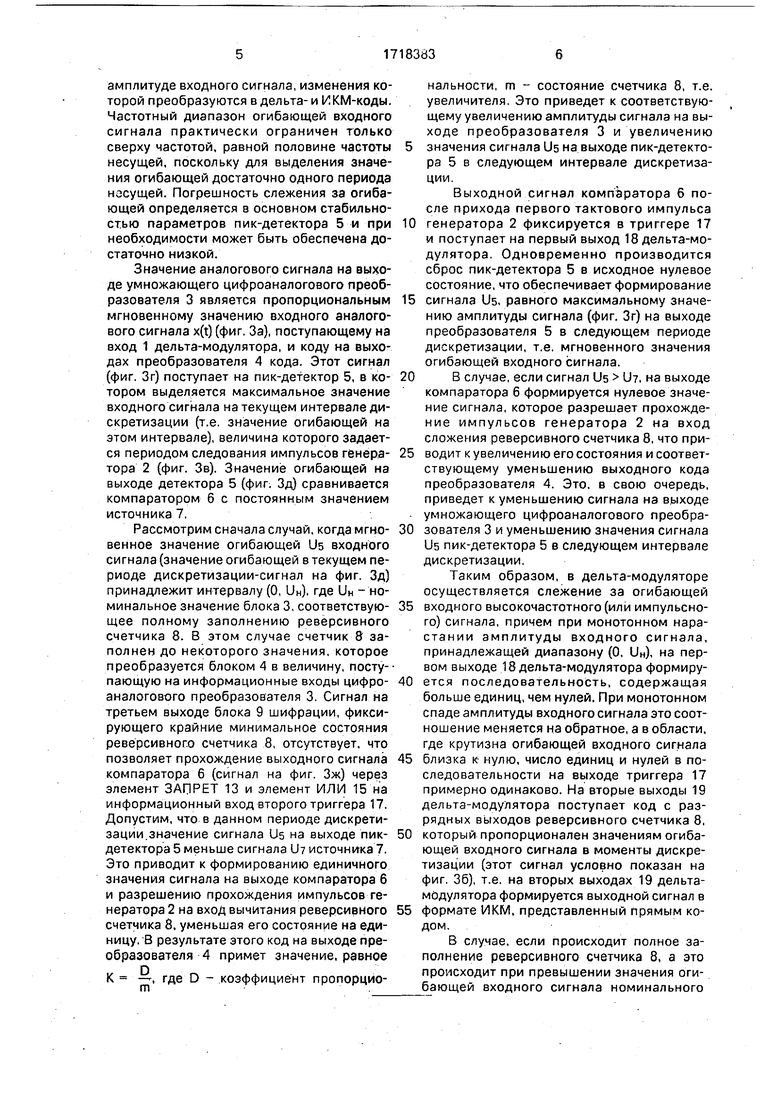

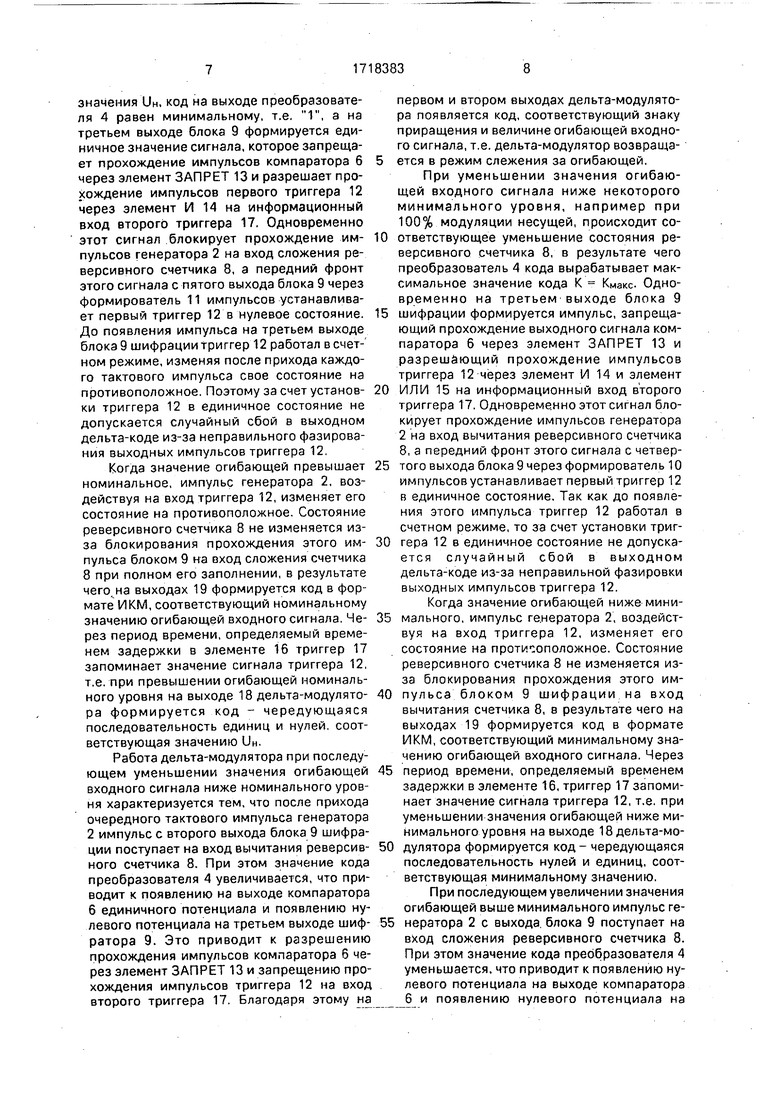

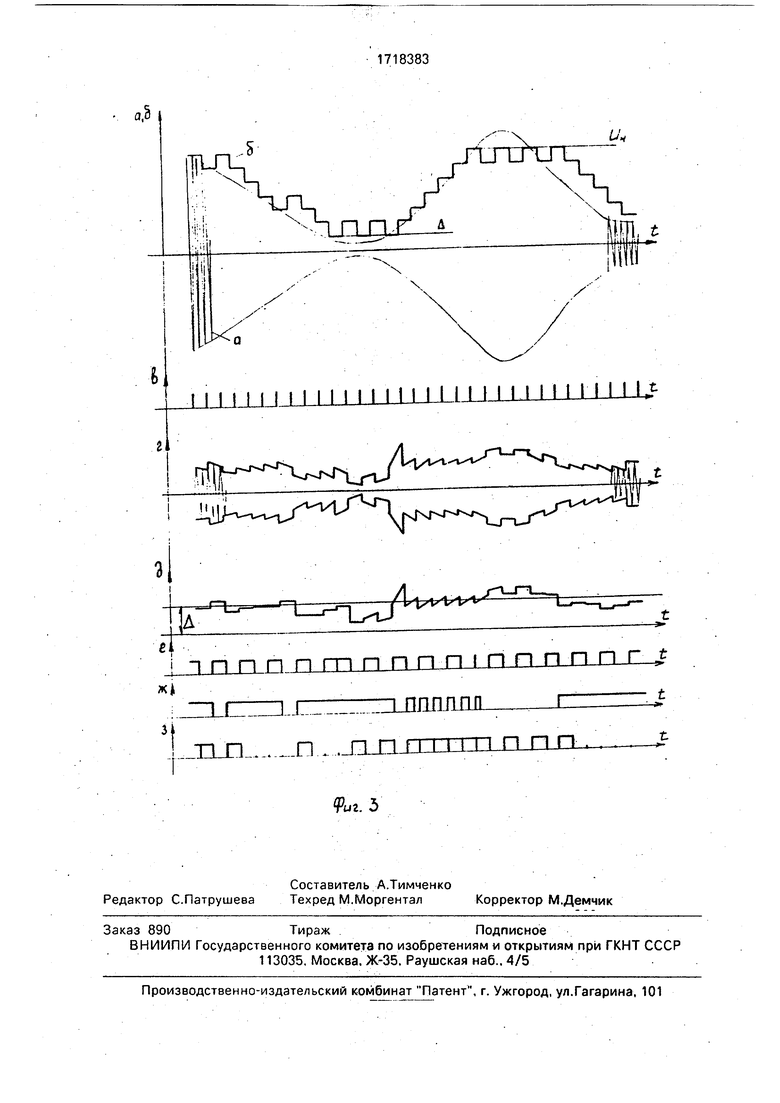

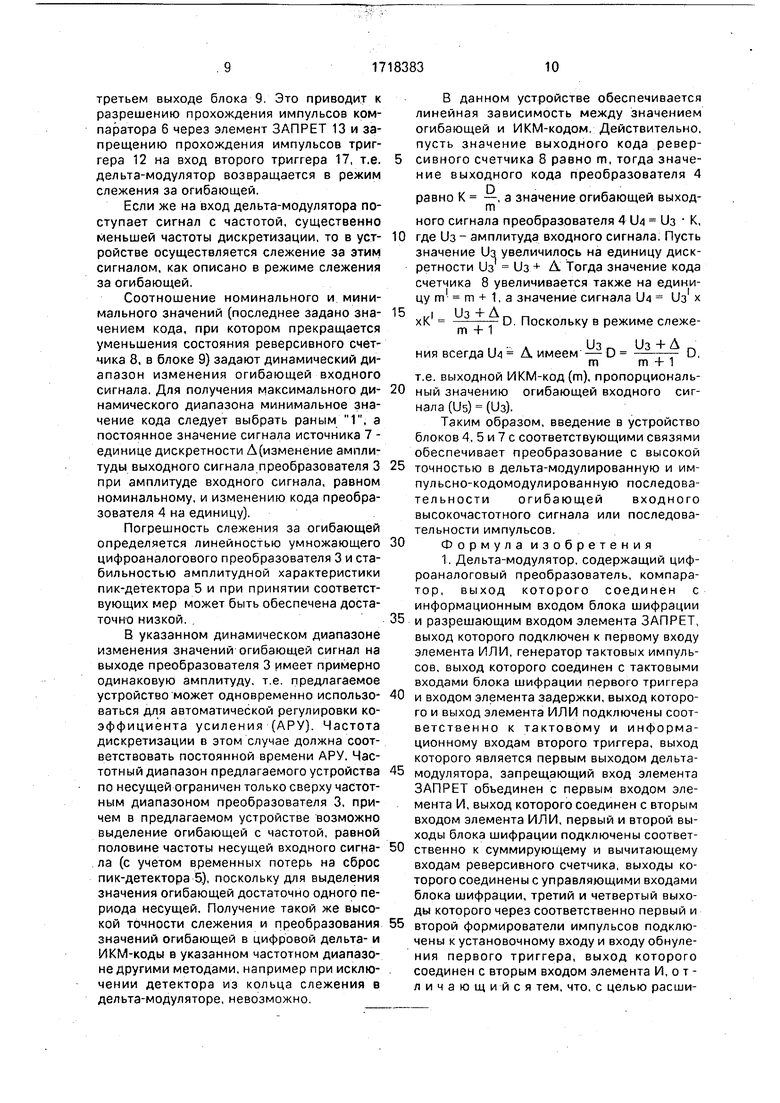

На фиг. 1 приведена структурная электрическая схема дельта-модулятора; на фиг. 2 - блок шифрации: на фиг. 3 - временные диаграммы работы устройства для случая, если входной сигнал - синусоидальный.

Дельта-модулятор содержит вход 1, генератор 2 тактовых импульсов, умножающий цифроаналоговый преобразователь 3, преобразователь А кода, пик-детектор 5, компаратор 6, источник 7 постоянного сигнала, реверсивный счетчик 8, блок 9 шифрации, первый и второй формирователи 10 и 11 импульсов, первый триггер 12, элемент ЗАПРЕТ 13, элемент И 14, элемент И 15, элемент 16 задержки, второй триггер 17, первый 18 и вторые 19 выходы.

Блок 9 шифрации содержит элемент И 20, элемент ИЛИ-НЕ 21, первый и второй элементы НЕ 22 и 23, первый и второй элементы 24 и 25, элемент ИЛИ 26. На фиг. 2 также обозначены информационный, тактовый и управляющие входы 27-29, первый, второй, третий, четвертый и пятый выходы 30-34.

На фиг. 3 приведены следующие сигналы: а - входной синусоидальный сигнал; б - сигнал аппроксимации, соответствующий сигналу на импульснокодомодулирован- ном выходе 19 устройства; в - импульсы тактового генератора 2; г - выходной сигнал умножающего цифроаналогового преобразователя 3; д - выходной сигнал пик-детектора 5; е - импульсы на выходе триггера 12; ж - сигнал на выходе компаратора .6;il- значение сигнала на выходе источника 7; з-сигнал на дельта-кодовом выходе 18 устройства.

Масштаб сигналов (фиг. 3 г, д) увеличен вдвое по отношению к входному сигналу (фиг. За).

Управляющий вход цифроаналогового преобразователя 3 является входом 1 дельта-модулятора, выход преобразователя 3 соединен с информационным входом пик- детектора 5, выход которого соединен с первым входом компаратора 6, второй вход которого соединен с источником 7 постоянного сигнала, выход компаратора 6 соединен с первым входом элемента ЗАПРЕТ 12 и вторым входом блока 9 шифрации, первый и второй выходы которого сединены соответственно с первым и вторым входами реверсивного счетчика 8, выходы которого являются вторыми выходами 19 дельта- модулятора и соединены со третьими входами шифратора 9 и входами преобразователя 4 кода, выходы которого соединены с информационными входами умножающего цифроаналогового преобразователя 3. Выход генератора 2 тактовых импульсов соединен через элемент 16 задержки с тактовым входом второго триггера 17, непосредственно с тактовыми входами пик- детектора 5, первого триггера 12 и первым входом блока 9, третий выход которого соединен с запрещающим входом элемента ЗАПРЕТ 12 и первым входом элемента И 13, а четвертый и пятый выходы через формирователи 10 и 11 импульсов - с соответствующими установочными входами первого триггера 12, выход которого соединен с вторым входом элемента И 14, выход которого и выход элемента ЗАПРЕТ 13 соединены с входами элемента ИЛИ 15, выход которого соединен с информационным входом второ- готриггера 17, выход которого является первым выходом 18 дельта-модулятора.

Первый разрешающий вход элемента ЗАПРЕТ 24 объединен с одноименным входом элемента ЗАПРЕТ 25 и является информационным входом 27 блока 9, тактовым входом 28 которого является второй разрешающий вход элемента ЗАПРЕТ 25, объединенный с входом второго элемента НЕ 23, выход которого соединен с вторым разрешающим входом первого элемента ЗАПРЕТ 24. Управляющими входами 29 блока 9 являются входы элемента И 20, объединенные, кроме младшего разряда, с входами элемента ИЛИ-НЕ 21, младший разряд входов 29 соединен с младшим разрядом элемента ИЛИ-НЕ 21 через первый элемент НЕ 22, выход элемента И 20 соединен с запрещающим входом элемента ЗАПРЕТ 24 и первым входом элемента ИЛИ 26, второй вход которого объединен с запрещающим входом элемента ЗАПРЕТ 25 и подключен к выходу элемента ИЛИ-НЕ 21, выходы элементов ЗАПРЕТ 30 и 31, элемента ИЛИ 26 элементов И 20 и ИЛИ-НЕ 21 являются первым, вторым, третьим, четвертым и пятым выходами 30-34 соответственно блока 9.

Дельта-модулятор работает следующим образом.

Достигаемая цель реализуется путем применения умножающего цифроаналогового преобразователя 3. код на разрядных входах которого обратно пропорционален

амплитуде входного сигнала, изменения которой преобразуются в дельта- и 1/ КМ-коды. Частотный диапазон огибающей входного сигнала практически ограничен только сверху частотой, равной половине частоты несущей, поскольку для выделения значения огибающей достаточно одного периода носущей. Погрешность слежения за огибающей определяется в основном стабильностью параметров пик-детектора 5 и при необходимости может быть обеспечена достаточно низкой.

Значение аналогового сигнала на выходе умножающего цифроаналогового преобразователя 3 является пропорциональным мгновенному значению входного аналогового сигнала x(t) (фиг. За), поступающему на вход 1 дельта-модулятора, и коду на выходах преобразователя 4 кода. Этот сигнал (фиг. Зг) поступает на пик-детектор 5, в ко- тором выделяется максимальное значение входного сигнала на текущем интервале дискретизации (т.е. значение огибающей на этом интервале), величина которого задается периодом следования импульсов генера- тора 2 (фиг. Зв). Значение огибающей на выходе детектора 5 (фиг. Зд) сравнивается компаратором б с постоянным значением источника 7,

Рассмотрим сначала случай, когда мгно- венное значение огибающей Us входного сигнала (значение огибающей в текущем периоде дискретизации-сигнал на фиг. Зд) принадлежит интервалу (О, UH). где UH - номинальное значение блока 3, соответствую- щее полному заполнению реверсивного счетчика 8. В этом случае счетчик 8 заполнен до некоторого значения, которое преобразуется блоком 4 в величину, постулающую на информационные входы цифро- аналогового преобразователя 3. Сигнал на третьем выходе блока 9 шифрации, фиксирующего крайние минимальное состояния реверсивного счетчика 8, отсутствует, что позволяет прохождение выходного сигнала компаратора 6 (сигнал на фиг. Зж) через элемент ЗАПРЕТ 13 и элемент ИЛИ 15 на информационный вход второго триггера 17. Допустим, что в данном периоде дискретизации.значение сигнала Us на выходе пик- детектора 5 меньше сигнала U источника 7. Это приводит к формированию единичного значения сигнала на выходе компаратора 6 и разрешению прохождения импульсов генератора 2 на вход вычитания реверсивного счетчика 8, уменьшая его состояние на единицу. В результате этого код на выходе преобразователя 4 примет значение, равное

К -г, где D - коэффициент пропорцио- m.

нальности, m - состояние счетчика 8, т.е. увеличителя. Это приведет к соответствующему увеличению амплитуды сигнала на выходе преобразователя 3 и увеличению значения сигнала Us на выходе пик-детектора 5 в следующем интервале дискретизации.

Выходной сигнал компаратора 6 после прихода первого тактового импульса генератора 2 фиксируется в триггере 17 и поступает на первый выход 18 дельта-модулятора. Одновременно производится сброс пик-детектора 5 в исходное нулевое состояние, что обеспечивает формирование сигнала Us, равного максимальному значению амплитуды сигнала (фиг. Зг) на выходе преобразователя 5 в следующем периоде дискретизации, т.е. мгновенного значения огибающей входного сигнала.

В случае, если сигнал Us U, на выходе компаратора б формируется нулевое значение сигнала, которое разрешает прохождение импульсов генератора 2 на вход сложения реверсивного счетчика 8, что приводит к увеличению его состояния и соответствующему уменьшению выходного кода преобразователя 4. Это. в свою очередь, приведет к уменьшению сигнала на выходе умножающего цифроаналогового преобразователя 3 и уменьшению значения сигнала Us пик-детектора 5 в следующем интервале дискретизации.

Таким образом, в дельта-модуляторе осуществляется слежение за огибающей входного высокочастотного (или импульсного) сигнала, причем при монотонном нарастании амплитуды входного сигнала, принадлежащей диапазону (О, UH), на первом выходе 18 дельта-модулятора формируется последовательность, содержащая больше единиц, чем нулей. При монотонном спаде амплитуды входного сигнала это соотношение меняется на обратное, а в области, где крутизна огибающей входного сигнала близка к- нулю, число единиц и нулей в последовательности на выходе триггера 17 примерно одинаково. На вторые выходы 19 дельта-модулятора поступает код с разрядных выходов реверсивного счетчика 8, который пропорционален значениям огибающей входного сигнала в моменты дискретизации (этот сигнал условно показан на фиг. 36), т.е. на вторых выходах 19 дельта- модулятора формируется выходной сигнал в формате ИКМ, представленный прямым кодом.

В случае, если происходит полное заполнение реверсивного счетчика 8, а это происходит при превышении значения огибающей входного сигнала номинального

значения Ун. код на выходе преобразователя 4 равен минимальному, т.е. 1, а на третьем выходе блока 9 формируется единичное значение сигнала, которое запрещает прохождение импульсов компаратора 6 через элемент ЗАПРЕТ 13 и разрешает прохождение импульсов первого триггера 12 через элемент И 14 на информационный вход второго триггера 17. Одновременно этот сигнал блокирует прохождение им- пульсов генератора 2 на вход сложения реверсивного счетчика 8, а передний фронт этого сигнала с пятого выхода блока 9 через формирователь 11 импульсов устанавливает первый триггер 12 в нулевое состояние. До появления импульса на третьем выходе блокэЭ шифрациитриггер 12 работал всчет- ном режиме, изменяя после прихода каждого тактового импульса свое состояние на противоположное. Поэтому за счет установ- ки триггера 12 в единичное состояние не допускается случайный сбой в выходном дельта-коде из-за неправильного фазирования выходных импульсов триггера 12.

Когда значение огибающей превышает номинальное, импульс генератора 2, воздействуя на вход триггера 12, изменяет его состояние на противоположное. Состояние реверсивного счетчика 8 не изменяется из- за блокирования прохождения этого им- пульса блоком 9 на вход сложения счетчика 8 при полном его заполнении, в результате чего, на выходах 19 формируется код в формате И КМ, соответствующий номинальному значению огибающей входного сигнала. Че- рез период времени, определяемый временем задержки в элементе 16 триггер 17 запоминает значение сигнала триггера 12, т.е. при превышении огибающей номинального уровня на выходе 18 дельта-модул я то- ра формируется код - чередующаяся последовательность единиц и нулей, соответствующая значению UH.

Работа дельта-модулятора при последующем уменьшении значения огибающей входного сигнала ниже номинального уровня характеризуется тем, что после прихода очередного тактового импульса генератора 2 импульс с второго выхода блока 9 шифрации поступает на вход вычитания реверсив- ного счетчика 8. При этом значение кода преобразователя 4 увеличивается, что приводит к появлению на выходе компаратора 6 единичного потенциала и появлению нулевого потенциала на третьем выходе шиф- ратора 9. Это приводит к разрешению прохождения импульсов компаратора б через элемент ЗАПРЕТ 13 и запрещению прохождения импульсов триггера 12 на вход второго триггера 17. Благодаря этому на

первом и втором выходах дельта-модулятора появляется код, соответствующий знаку приращения и величине огибающей входного сигнала, т.е. дельта-модулятор возвращается в режим слежения за огибающей.

При уменьшении значения огибающей входного сигнала ниже некоторого минимального уровня, например при 100% модуляции несущей, происходит соответствующее уменьшение состояния реверсивного счетчика 8, в результате чего преобразователь 4 кода вырабатывает максимальное значение кода К Кмакс. Одновременно на третьем выходе блока 9 шифрации формируется импульс, запрещающий прохождение выходного сигнала компаратора 6 через элемент ЗАПРЕТ 13 и разрешающий прохождение импульсов триггера 12 через элемент И 14 и элемент ИЛИ 15 на информационный вход второго триггера 17. Одновременно этот сигнал блокирует прохождение импульсов генератора 2 на вход вычитания реверсивного счетчика 8, а передний фронт этого сигнала с четвертого выхода блока 9 через формирователь 10 импульсов устанавливает первыйтриггер 12 в единичное состояние. Так как до появления этого импульса триггер 12 работал в счетном режиме, то за счет установки триггера 12 в единичное состояние не допускается случайный сбой в выходном дельта-коде из-за неправильной фазировки выходных импульсов триггера 12.

Когда значение огибающей ниже минимального, импульс генератора 2, воздействуя на вход триггера 12, изменяет его состояние на противоположное. Состояние реверсивного счетчика 8 не изменяется из- за блокирования прохождения этого импульса блоком 9 шифрации на вход вычитания счетчика 8, в результате чего на выходах 19 формируется код в формате И КМ, соответствующий минимальному значению огибающей входного сигнала. Через период времени, определяемый временем задержки в элементе 16, триггер 17 запоминает значение сигнала триггера 12, т.е. при уменьшении значения огибающей ниже минимального уровня на выходе 18 дельта-модулятора формируется код- чередующаяся последовательность нулей и единиц, соответствующая минимальному значению.

При последующем увеличении значения огибающей выше минимального импульс генератора 2 с выхода, блока 9 поступает на вход сложения реверсивного счетчика 8. При этом значение кода преобразователя 4 уменьшается, что приводит к появлению нулевого потенциала на выходе компаратора 6 и появлению нулевого потенциала на

третьем выходе блока 9. Это приводит к разрешению прохождения импульсов компаратора 6 через элемент ЗАПРЕТ 13 и запрещению прохождения импульсов триггера 12 на вход второго триггера 17, т.е. дельта-модулятор возвращается в режим слежения за огибающей.

Если же на вход дельта-модулятора поступает сигнал с частотой, существенно меньшей частоты дискретизации, то в устройстве осуществляется слежение за этим сигналом, как описано в режиме слежения за огибающей.

Соотношение номинального и минимального значений (последнее задано значением кода, при котором прекращается уменьшения состояния реверсивного счетчика 8. в блоке 9) задают динамический диапазон изменения огибающей входного сигнала. Для получения максимального динамического диапазона минимальное значение кода следует выбрать раным 1, а постоянное значение сигнала источника 7 - единице дискретности Л(изменение амплитуды выходного сигнала преобразователя 3 при амплитуде входного сигнала, равном номинальному, и изменению кода преобразователя 4 на единицу).

Погрешность слежения за огибающей определяется линейностью умножающего цифроаналогового преобразователя 3 и стабильностью амплитудной характеристики пик-детектора 5 и при принятии соответствующих мер может быть обеспечена достаточно низкой..

В указанном динамическом диапазоне изменения значений огибающей сигнал на выходе преобразователя 3 имеет примерно одинаковую амплитуду, т.е. предлагаемое устройство может одновременно использоваться для автоматической регулировки коэффициента усиления (АРУ). Частота дискретизации в этом случае должна соответствовать постоянной времени АРУ. Частотный диапазон предлагаемого устройства по несущей ограничен только сверху частотным диапазоном преобразователя 3, причем в предлагаемом устройстве возможно выделение огибающей с частотой, равной половине частоты несущей входного сигнала (с учетом временных потерь на сброс пик-детектора 5), поскольку для выделения значения огибающей достаточно одного периода несущей. Получение такой же высокой точности слежения и преобразования значений огибающей в цифровой дельта- и ИКМ-коды в указанном частотном диапазоне другими методами, например при исключении детектора из кольца слежения в дельта-модуляторе, невозможно.

В данном устройстве обеспечивается линейная зависимость между значением огибающей и ИКМ-кодом, Действительно, пусть значение выходного кода ревер- сивного счетчика 8 равно т, тогда значение выходного кода преобразователя 4

равно К -, а значение огибающей выход- m

ного сигнала преобразователя 4IJ4 1)з К, где Уз - амплитуда входного сигнала; Пусть значение 11з увеличилось на единицу дискретности Уз Us + Д. Тогда значение кода счетчика 8 увеличивается также на единицу т1 т + 1, а значение сигнала U4 Уз х

„i Уз +А „

хК D. Поскольку в режиме слеже,, - АУз г. Us + А г,

ния всегда 1М Д имеем-О -- D,

тт + 1

т.е. выходной ИКМ-код(т), пропорциональный значению огибающей входного сигнала (Us) (Уз).

Таким образом, введение в устройство блоков 4, 5 и 7 с соответствующими связями обеспечивает преобразование с высокой

точностью в дельта-модулированную и им- пульсно-кодомодулированную последовательности огибающей входного высокочастотного сигнала или последовательности импульсов.

Формулаизобр е т е н и я

1. Дельта-модулятор, содержащий циф- роаналоговый преобразователь, компаратор, выход которого соединен с информационным входом блока шифрации

и разрешающим входом элемента ЗАПРЕТ, выход которого подключен к первому входу элемента ИЛИ, генератор тактовых импульсов, выход которого соединен с тактовыми входами блока шифрации первого триггера

и входом элемента задержки, выход которого и выход элемента ИЛИ подключены соот- ветстаенно к тактовому и информационному входам второго триггера, выход которого является первым выходом дельта

модулятора, запрещающий вход элемента

ЗАПРЕТ объединен с первым входом элемента И, выход которого соединен с вторым входом элемента ИЛИ, первый и второй выходы блока шифрации подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика, выходы которого соединены с управляющими входами блока шифрации, третий и четвертый выходы которого через соответственно первый и

второй формирователи импульсов подключены к установочному входу и входу обнуления первого триггера, выход которого соединен с вторым входом элемента И, о т - личающийся тем, что, с целью расширения области применения за счет преобразования огибающей входного сигнала в дельта-модулированную и импульсно-крдо- модулированную последовательность, в дельта-модулятор введены преобразователь кода, источник постоянного сигнала и пик-детектор а цифроаналоговый преобразователь выполнен умножающим, тактовый вход пик-детектора соединен с выходом генератора тактовых импульсов; входы преобразователя кодов подключены к выходам реверсивного счетчика, являющимся вторыми выходами дельта-модулятора, выходы преобразователя кодов соединены с информационными входами умножающего цифроаналогового преобразователя, управляющий вход которого является входом дельта-модулятора, выход умножающего цифроаналогового преобразователя подключен к информационному входу пик-детектора, выход которого и выход источника постоянного сигнала соединены соответственно с первым и вторым входами компаратора, пятый выход блока шифрации подключен к первому входу элемента И.

2. Дельта-модулятор по п. 1, о т л и ч а ю- щ и и с я тем, что блок шифрации содержит элемент И, первый и второй элементы ЗАПРЕТ, элемент ИЛИ, элемент ИЛИ-НЕ и первый и второй элементы НЕ, первые разрешающие входы элементов ЗАПРЕТ объединены и являются информационным

входом блока, вход второго элемента НЕ объединен со вторым разрешающим входом второго элемента ЗАПРЕТ и является тактовым входом блока, выход второго элемента НЕ соединен с вторым разрешающим входом первого элемента ЗАПРЕТ.первый вход элемента И объединен с входом первого элемента НЕ и является младшим разрядом управляющих входов блока, выход первого элемента НЕ соединен с первым входом

элемента ИЛИ-НЕ, вторые входы элементов И и ИЛИ-НЕ соответственно объединены и являются старшими разрядами управляющих входов блока, выходы первого и второго элементов ЗАПРЕТ являются

соответственно первым и вторым выходами блока, выход элемента И подключен к первому входу элемента ИЛИ, запрещающему входу первого элемента ЗАПРЕТ и является третьим выходом блока, выход элемента

ИЛИ-НЕ соединен с вторым входом элемента ИЛИ, запрещающим входом второго элемента ЗАПРЕТИ является четвертым выходом блока, выход элемента ИЛИ является пятым выходом блока.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1989 |

|

SU1649666A1 |

| Дельта-модулятор | 1990 |

|

SU1709531A2 |

| Дельта-модулятор | 1987 |

|

SU1448411A1 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Дельта-модулятор | 1985 |

|

SU1257849A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Дельта-модулятор | 1987 |

|

SU1425838A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1425841A1 |

| Цифровой фильтр | 1990 |

|

SU1758836A1 |

| Дельта-модулятор | 1986 |

|

SU1388992A1 |

Изобретение относится к автоматике и вычислительной технике. Его использование при спектральном и корреляционном анализе позволяет расширить область применения за счет преобразования огибающей входного сигнала в дельта-модулиро- ванную и импульсно-кодомодулированную последовательности. Дельта-модулятор содержит генератор 2 тактовых импульсов, цифроаналоговый преобразователь (ЦАП) 3, компаратор 6, реверсивный счетчик 8, блок 9 шифрации. формирователи 10, 11 импульсов, триггеры 12, 17, элемент 13 запрета, элемент И 14, элемент ИЛИ 15 и элемент 16 задержки. Благодаря введению преобразователя 4 кодов, пик-детектора 5, источника 7 постоянного сигнала и выполнению ЦАП 3 умножающим в дельта-модуляторе обеспечивается преобразование огибающей входного сигнала. 1 З.п. ф-яы, 3 ил. Ё

Фи2.2

UJJ ц « i i I I I 11 llliJJJLJ-illlJLLLm

3jn D-n-J3JinjnjarLO I П П П Л П-Г-J

JZLE

..JJUIUIUIIL

„ГШП . ...JIUllU-i-Ц i i П П П.

| Дельта-модулятор | 1987 |

|

SU1448411A1 |

| Дельта-модулятор | 1985 |

|

SU1257849A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-03-07—Публикация

1990-03-29—Подача