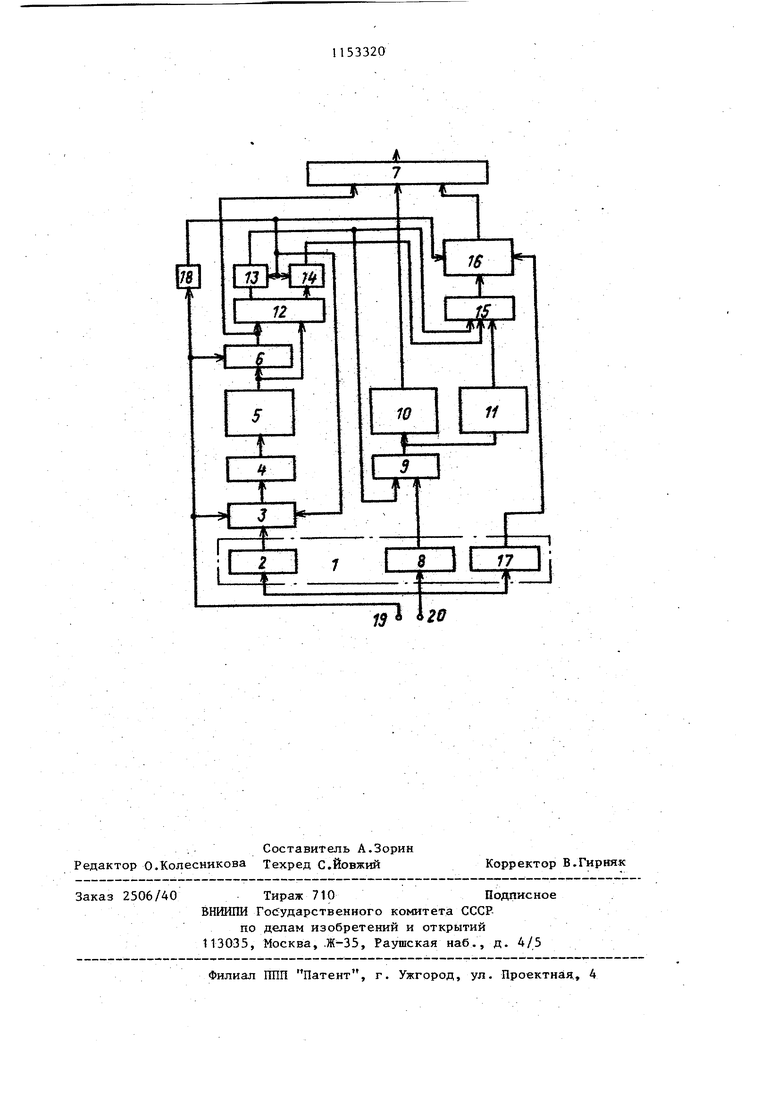

: Изобретение относится к области вычислительной техники и предназна чено для воспроизведения в ЦВМ зна чений функций одной переменной, на пример sin X, Рп V , 1 УХ и др. Известно устройство для воспроизведения .функций на основе постоя ного запоминающего устройства, в котором хранятся таблицы значений функций для определенных значений аргумента. Такое устройство содерж регистр входного слова, дешифратор накопитель и регистр выходного сло В качестве входного слова использу ется значение аргумента, а выходного - значение/функции от этого аргумента Cl3. Недостатком такого устройства являются его ограниченные возможно ти, поскольку трудно построить нак питель боль1вой емкости. При ограни ченной емкости накопителя устройст обладает невысокой точностью воспро изведения функции из-за необходимос увеличения дискретности .аргумента. Наиболее близким по технической сущности к данному является устройство воспроизведения функции, содер жащее последовательно включенные регистр старших разрядов входного слова, первый дешифратор, первый на копитель, регистр выходного слова и сумматор, последовательно включенные регистр мпадших разрядов входного слова, второй дешифратор и второй накопитель, выходы которого подключены к другим входам сумматора, а также регистр средник разрядов входного слова, выходы которого подключены к другим входам первого дешифратора, а выходы регистра старших разрядов входного слова - к другим входам второго дешифратора 23. Такое устройство требует значительно меньшей емкости накопителя по сравнению с известными. Однако при ограниченном объеме накопителя точность воспроизведения функций в таком устройстве в ряде случаев оказьшается недостаточной. Погрешность больше на тех участках, где вторая производная велика. При огра ниченной емкости накопителя Е ряде случаев на таких участках точность воспроизведения функции может оказаться недостаточно высокой. 20 Цель изобретения - повьшение точности. Цель достигается путем введения линейной интерполяции по дополнительным младшим разрядам аргумента с использованием коэффициентов интерПОЛЯ1Д1И, выбираемых из таблиц и принимаемьпс постоянными на интервале величина которого выбирается обратно пропорциональной второй производной функции. Поставленная цель достигается тем, что в устройство для воспроизведения функций табличным методом, содержащее регистр входного слова, два дешифратора, два блока памяти, регистр выходного слова и первый сумматор, причем информационный вход устройства соединен с входом регистра входного слова, выход первого дешифратора соединен с адресным входом первого блока памяти, выход которого соединен с информационным входом регистра выходного слова, выход которого подключен к первому входу первого сумматора, второй вход которого подключен к выходу второго блока памяти, адресный вход которого соединен через второй дешифратор с выходом младщих разрядов регистра входного слова, дополнительно введены счетчик, адреса, второй и третий сумматоры, третий блок памяти, блок умножения, peгиctpы старших и младших разрядов приращений и элемент НЕ, вход которого соединен с тактовым входом устройства, входом разрешения записи счетчика адреса и тактовым входом регистра выходного слова, выход которого соединен с первым входом сумматора., выходы старших и младших разрядов которого соединены соответственно с информационнь 1и входами регистра старших и регистра младших разрядов приращений, тактовые входы которых соединены с выходом элемента НЕ, счетным входом счетчика адреса и тактовым входом блока умножения, первый и второй информационные входы которого соединены соответственно с выходом дополнительных разрядов регистра входного слова и выходом третьего сумматора, входы с первого по третий которого соединены с выходами соответственно регистра старших разрядов приращений, регистра младших разрядов приращений и третьего блока памяти, вход которого соединен с выходом второго дешифратора, второй вход которого соединен с выходом регистра старших разрядов приращений, выходы первого блока памяти и блока умножения соединены с вторым входом второго сумматора и третьим входом первого сумматора. Введение в устройство счетчика адреса и второго сумматора позволяет вычислять приращения функции на шаге Й как разность соседних опорных значений )iV«n,). а введение регистра старших разрядов приращения функции и подключение его выходов к другим входам второго дешифратора обеспечивает воспроизведение функции по формуле: W(.z(v,x,): где дЧ« - значение старших разрядов, приращения лУ. Таким образом, шаг Не, на котором п правки 2 сохраняются неизменными, оп ределяется скоростью изменения стар- ших разрядов приращения функции лЧ т.е. второй производной функции. Это приводит к уменьшению 4л на участках, где вторая производная велика. Введение в устройство регистра дополнительных млйдших разрядов входного слова, третьего блока памяти, третьего регистра выходного слова, третьего су№1атора и блока умножения, а также регистра младших разрядов приращения функции и соответствующих связей позволяет воспроизводить функцию по формуле 4(x).Y(X,).Z(u4j,X,).JV(x)(AXj,X) где hf, - шаг изменения мпадщих разрядов Xf, аргумента j Aon значение дополнительных младших разрядов аргумента (младише Х, , в пределах шага „ ); . f(лУ. I X ) - дополнительный коэффициент линейной интерполяции между точками, определяемыми значениями K.),H( VHrV)-f()i;;--f№ HJ-4 i))WVMml Опорное значение N(Xn,) и поправа Z(dY. , Хр, ) вычисляются по формуам/Н Т .i-H4..-f-bHvMJ-ik th flx T-Hc r l HWO-2(х,.Н, (.vKtei b4 t)f()( rflVHe-W l- C c rV Ji;;4 H rV2€fxi T)f{W4} «и -Н +Х 1-2 1Х-f-H-Н +Х } Д I I w w) { К 1 1 / ( Погрешность воспроизведения функвди в этом случае складывается из погрешности линейной интерполяции и погрешности из-за неизменности величин Z и на шаге Hj ) 2m+2n 4- J(X) . где Ч - максимальное значение функции Y(X). Эта погрешность может быть существенно меньше, чем в прототипе. На чертеже представлена блок-схема устройства. Устройство содержит регистр входного слова 1, группу старпшх разрядов 2, счетчик адреса 3, дешифратор 4, блок памяти 5, регистр выходного слова 6, 7, младшие разряды 8, депшфратор 9, блоки памя ти to, 11 суьсматор 12, регистры старших 13 и младших tA приращений, сумматор 15, блок умножений 16, дополнительные разряды 17 и элемент НЕ 18, тактовьй 19 и информационный 20 входы устройства. S Устройство для воспроизведения функций работает следую1Щ1м образом. При поступлении аргумента по вхо ду 20 m тарших разрядов его записы вают в регистр старших разрядов входного слова 2, а h младших раз рядов - в регистр младших разрядов входного слова 8. Одновременно по входу 19 поступает синхронизирующий сигнал, обеспечивающий прием информации в счетчик адреса 3 и регистр выходного слова 6. Возбуждается одна из выходных шин первого дешифратора 4, и соответствующее опорное значение Y(X) фиксируется в регист ре вькодного слова 6. Когда синхронизирующий сигнал исчезает, на выходе элемента НЕ Т8 появляется сигнал. В результате в счетчике адреса 3 старшие адреса увеличиваются на единицу и из блока памяти 5 считывается следующее опорное значение Х(Х +Н ), которое поступает во второй сумматор 12, где из него вычита ется значение у (Х ) регистра 6 . Во втором сумматоре 12 получается приращение функции 4Ув старших раз рядов которого фиксируются в р-егист ре старших разрядов приращения функции 13 и вместе с п младшими разрядами аргумента из регистра младших разрядов входного слова 8 поступают на вход второго дёишфрато ра 9, возбуждая одну из его выходных шин. Из второго блока памяти 10 считывается соответствующее значение поправки Z(jSYp , , которое в первом сумматоре 7 складывается с опорным значением функции из перво 06 го регистра выходного слова 6. Кроме того, полное значение приращения функции Y, считьюаемое с р-егистров старших 13 и младших 14 разрядов приращения функции, поступает в третий сумматор 15, где складывается с дополнительньм коэффициентом линейной интерполяции , поступающим из третьего блока памяти 11. Получанная сумма в блоке умножения 16 умножается (в соответствующем масштабе) на значение, поступающее из регистра дополнительных младших разрядов входного слова 17, где фиксируются К самым мпадших разрядов аргумента, результат умножения в первом сумматоре 7 складывается с опорным значением Y ( Х„ ) и поправкой Z формируя искомое значение функции. Рассмотрим воспроизведение функции (Х) 1/4 yf при 0,0625 Х 6. 1, При емкости каждого из трех блоков памяти по 2 слов и при разрядности аргумента 23 разряда. При этом получается т 10, С 6, п 4. В этом случае 12 самых тяжелых интервалов Hj , начиная с минимального значения Х 0,0625, содержат только по одному интервалу И... , и у них погрешность из-за неизменности величин 2 и Y равна нулю. Тринадцатый интервал Н содержит два интервала Н„ и т.д. Методическая погрешность составляет 2 -10 , Такая высокая точность при сопоставимых объемах накопителя в прототипе недостижима.

1$ 20

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1982 |

|

SU1024894A1 |

| Устройство для вычисления стандартных функций | 1980 |

|

SU942032A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1008735A1 |

| Функциональный преобразователь | 1981 |

|

SU1005069A1 |

| Цифровой функциональный преобразователь | 1982 |

|

SU1024893A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU742947A1 |

| Устройство для воспроизведения функции @ @ | 1982 |

|

SU1061137A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Функциональный преобразователь | 1984 |

|

SU1171774A1 |

| Постоянное запоминающее устройство для воспроизведения функций | 1982 |

|

SU1049977A1 |

УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ ФУНКВДЙ ТАБЛИЧНЫМ МЕТОДОМ, содержащее регистр входного слова, два дешифратора, два блока памяти, регистр вь1ходного слова и первый сумматор, причем информационный вход устройства соединен с входом регистра входного слова, выход первого дешифратора соединен с адресным входом первого блока памяти, выход которого соединен с информационным входом регистра выходного слова, выход которого подключен к первому входу первого сумматора, второй вход которого подключен к выходу второго блока памяти, адресный вход которого соединен через второй дешифратор с выходом младших разрядов регистра входного слова, отличающееся тем, что, с целью повьппения точности, в него введены счетчик адреса, второй и третий сумматоры, третий блок памяти, блок умножения, регистры старпмх и младших разрядов приращений и элемент НЕ, вход которого соединен с тактовым входом устройства, входом разрешения записи счетчика адреса и тактовым входом регистра выходного слова, выход которого соединен с первым входом сумматора, выходы старших и младших разрядов которого соединены соответственно с информационными входами регистра старших и регистра мпадших разрядов приращений, тактовые входы которых соединены с выходом элемента НЕ, счетным входом счетчи(Л ка адреса и тактовым входом блока умножения, первый и второй информационные входы.которого соединены соответственно с выходом дополнительных разрядов регистра входного слова и выходом третьего сумматора, входы с первого по третий которого соединены с выходами соответственно ел регистра старших разрядов приращений, оэ регистра мпадших разрядов приращений со и третьего блока памяти, вход котоN3 рого соединен с выходом второго дешифратора, второй вход которого соединен с выходом регистра старамх разрядов приращений, выходы первого блока памяти и блока умножения соединены с втор№4 входом второго сумматора и третьим входом первого сумматора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Крайзмер Л.П | |||

| Устройства хранения дискретной информации | |||

| М., Энергия, 1969, с | |||

| Котел | 1921 |

|

SU246A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Балашов Е.П | |||

| К вопросу применения сокращенных таблиц функций для построения высокопроизводительных однофазных процессоров | |||

| УС и М., 1975, № 3, с | |||

| Приспособление для записи звуковых явлений на светочувствительной поверхности | 1919 |

|

SU101A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-04-30—Публикация

1983-11-05—Подача