1

Изобретение относится к вычислительной технике , в частности к устройствам для вычисления стандартных функций.

Известно устройство, содержащее накопитель, сумматор, блок местного управления и регистр сдвига, последовательно соединенный с регистром входного слова. В накопителе каждому числу, записанному в старших разря- Q дах регистра входного слова, соответствует базисное выходное слово и ряд приращений. Результат получается путем суммирования базисного слова и одного из приращений, соответствую- is щего коду младших разрядов регистра входного слова 1.

Недостаток этого устройства - нерегулярность структуры и большой 20 объем оборудования.

Наиболее близким по своей технической сущности к предлагаемому является устройство для вычисления

адресов табличных функций, содержа- щее регистр адреса команд, выходы которого соединены с первой группой входов сумматора и через регистр адреса с входами блока памяти, выходы которого через выходной регистр соединены с второй группой входов сумматора и с первой группой входов регистра аргумента, выходы которого соединены с третьей группой входов сумматора, выходы которого соединены с первой группой входов устройства, улразлякиций вход которого соединен со счетным входом регистра адреса, а вторая группа входов регистра аргумента соединена с второй группой входов устройства, .причем выходы регистра аргумента соединены с входами Элементов И первой группы, выходы которых соединены с четвертой группой входов сумматора. В этом ycтpoй tве в блоке памяти хранятся табличные значения функций, расположенных в ячейках в виде таблиц с постояннопеременным шагом по адресам, .и узловые значения аргумента t2.

Недостатком известного устройства является низкое быстродействие, объясняемое тем, что получение табличного значения происходит в два этапа На первом этапе реализуется итерационный процесс поиска некоторого поддиапазона, в котором лежит значение аргумента, путем последовательного с(эавнения значения аргумента с узловыми значениями. Второй этап сводится к получению табличного значения воспроизводимой функции путем выборки этого значения из памяти. Кроме того, в ряде случаев не удается получить существенного сокращения необходимого объема памяти по сравненйю с постоянным шагом расположения по адресам табличных значений функции.

Недостатком известного устройства является также нерегулярность расположения информации в блоке памяти. При этом известный способ получения табличных значений функций не позволяет воспроизводить немонотонные функции, что сужает класс воспроизводимых функций, а известное устройство характеризуется сложностью подготовки исходной информацрвй, необходимой для воспроизведения стандартных функций во всем диапазоне изменения аргумента.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем что в устройство для вычисления стандaptныx функций, содержащее регистр аргумента, первый блок памяти, сумматор и выходной регистр, при этом вход устройства соединен с входом регистра аргумента, введены дешифратор, элемент запрета, сумматор адреса, второй блок памяти, мультиплексор и элемент ИЛИ, причем выходы дву младших разрядов регистра аргумента соединены с входами дешифратора, а выходы старших разрядов - с входами сумматора адреса и второго блока памяти, выходы суммы сумматора адреса подключены к входам первого блока памяти, а выход переноса - к первом входу элемента ИЛИ и инверсному входу элемента запрета, прямой вход которого подсоединен к выходу первого разряда регистра аргумента, первая и вторая группы информационных входов сумматора соединены с выходаМИ соответственно первого и второго блоков памяти, первый управляющий вход - с первым выходом дешифратора, а второй управляющий вход - с выходом элемента ИЛИ, второй вход элемента ИЛИ подключен к второму выходу дешифратора, третий выход которого подключен к входу переноса сумматора адреса, 1-й вход первой группы и

o I +1 - и вход второй группы.мультиплексора соединены с -м сумматора, где 1 is п, п - число выходов первого или второго блока памяти, выход переноса сумматора

5 соединен со старшим входом второй группы входов мультиплексора, выходы мультиплексора подключены к входам выходного регистра, а управляющий вход мультиплексора - к выходу элемента запрета, при этом выходы выходного регистра соединены с выходами ycтpoйctвa.

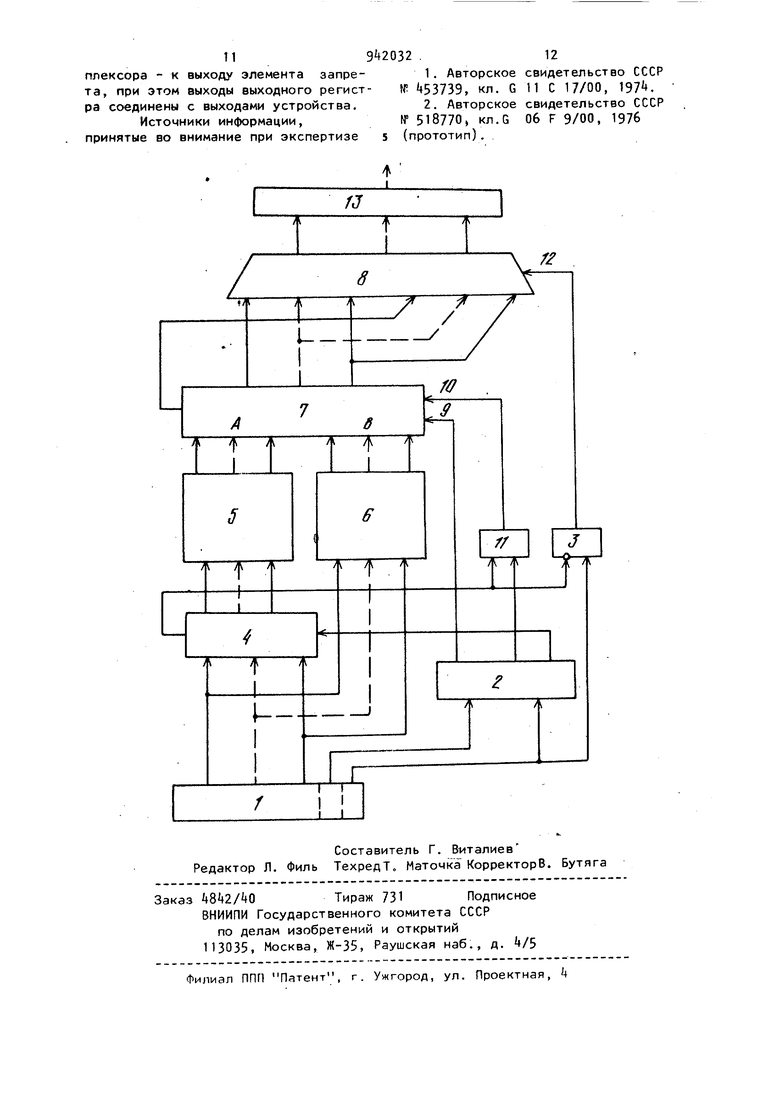

На чертеже приведена функциональная схема устройства для вычисления стандартных функций.

Устройство содержит регистр 1 аргумента, выход первого младшего разряда которого соединен с первым входом дешифратора 2 и с прямым входом элемента 3 запрета. Второй вход Дешифратора 2 соединен с выходом второго разряда регистра 1, остальные п - 2 рязряда которого соединены через сумматор k адреса с входами первого блока 5 памяти и непосредственно - с входами второго блока 6 памяти. Разрядные выходы блоков 5 и 6 соединены соответственно с первой и второй группами входом сумматора 7. Ниже первая группа входов сумматора 7 обозначена шиной А, а втораяшиной В. Каждый i-и разрядный выход сумматора 7 соединен с J-м входом первой группы входов мультиплексора 8 для .передачи информации без сдвига и с i + 1 - м входом второй группы входов мультиплексора 8 для передачи информации со сдвигом на один разряд вправо, причем к старшему

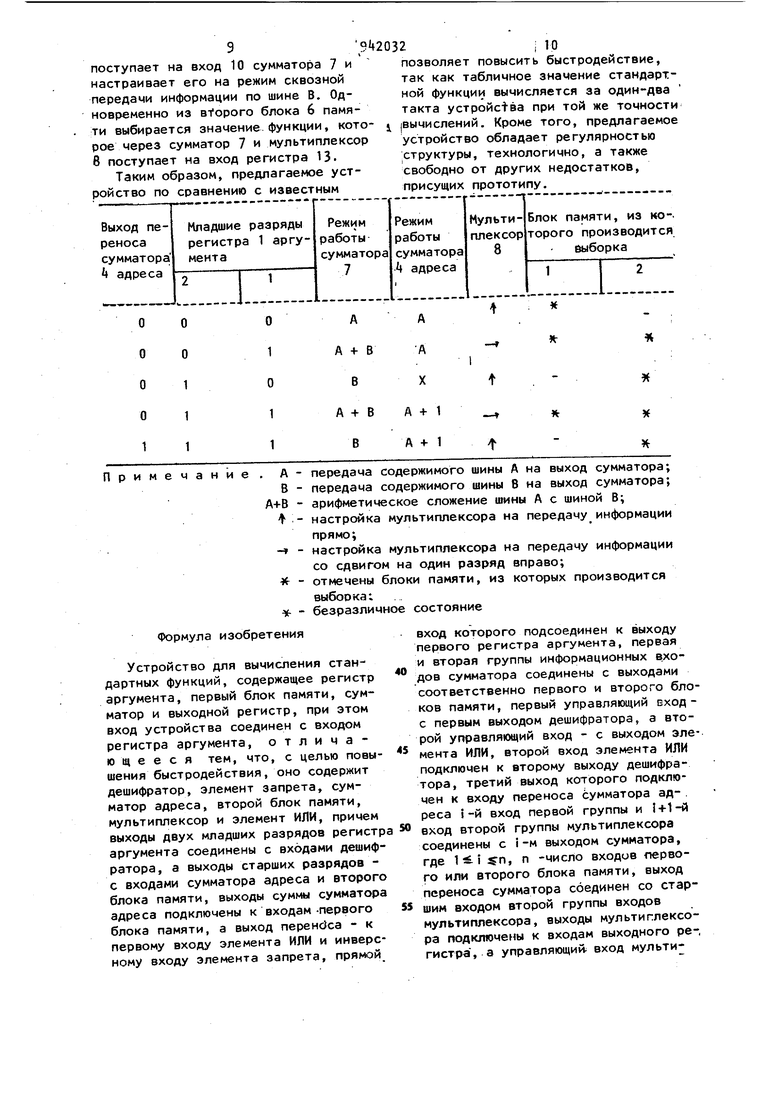

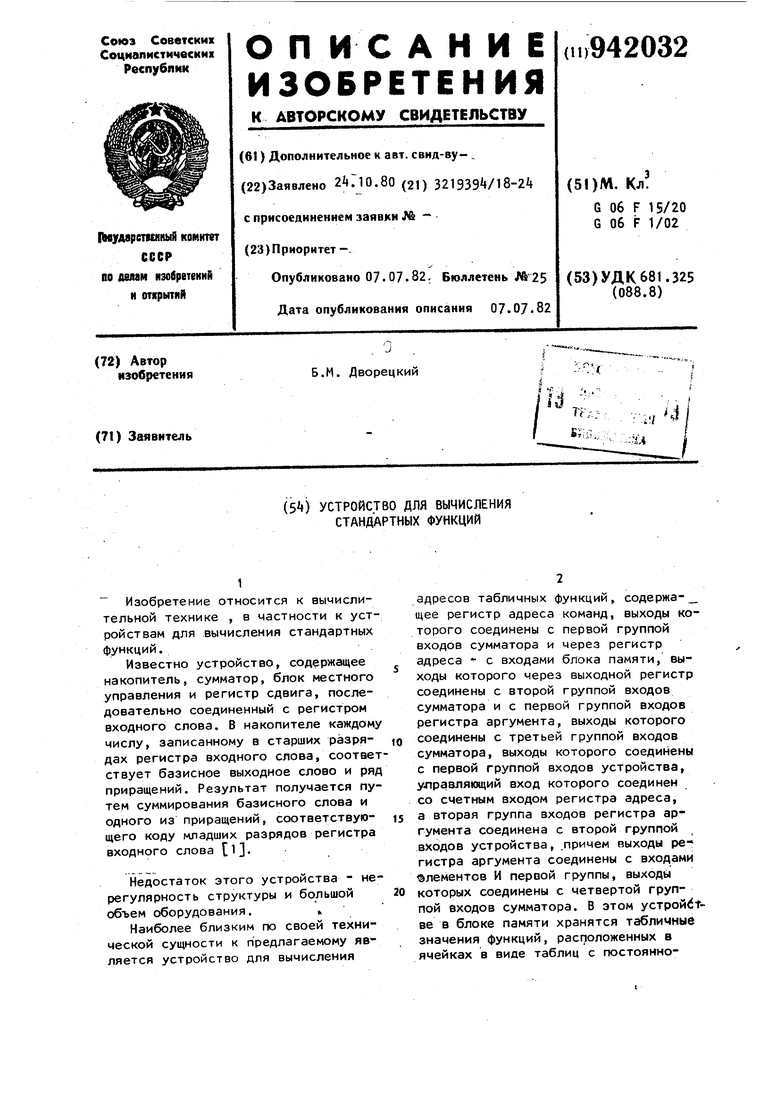

входу второй группы входов мультиплексора 8 подключен выход переноса сумматора 7. Сумматор 7 имеет два управляющих входа: первый 9 и второй 10, служащих соответственнодля настройки сумматора 7 на сквозную пе- . редачу информации с шины А или шины В на выход сумматора. При отсутствии сигналов на входах 9 и 10 сумматора 7 последний выполняет обычную функцию арифметического сложения. Вход 9 сумматора 7 соединен с первым выходом дешифратора 2, а вход 10 - с выходом элемента ИЛИ 11, первый вхо которого соединен с вторым выходом дешифратора 2, а второй вход - с инверсным входом элемента запрета и с выходом переноса сумматора 4 ад реса, вход переноса которого сс единен с третьим выходом дешифратора 2 Выход элемента 3 запрета соединен с. управляющим входом 12 мультиплексора 8, выходы которого соединены с в сддами выходного регистра 13. Подготовка исходной информации, записываемой в блоки 5 и 6, осуществляется следующим образом. Обозна чим множество всех значений дискрет ного аргумента через X jXji , j 0,1,2,.... Здесь п - количество двоичных разрядов без учета знаков, которыми представлен аргумент х. Удалим из множества X множество значений аргу мента X, имеющих нечетные индексы, и обозначим его через Х х, г 1,3.5,...,,...,2 Очевидно, что оставшееся множество значений Х Х/Х состоит из точек аргумента, имеющих четные индексы ,2,t,...,2j,...,2 - 2. Для всех значений аргумента х, принадлежащих множеству Х., вычисляются значения функции f(xp), р 0,2,,...2,...,2 - 2. Это множество обозначим через Y f(xp), р 0,2,4,...2,...,2 Множество Y разобьем на два подмножества(x),,i,8,..., Y f(xe) ,,6,.2....2 Здесь 0 к«-т- , очевидно, что Yj Y2 VY,. Значения функции f(x)€ Y, S 0,4,8,...4,..., размещаются в порядке возрастания адресов друг за другом в первом бло 5 памяти, а значения функции М Y|, ,6,10,... V-«-2,.., размещаются аналогичный образом во втором блоке 6 памяти. При этом мас сив Y во втором блоке 6 памяти начинается с того же адреса, начиная с которого расположен массив Yj в первом блоке 5 памяти. Так например, в первом болке памяти 5 по нулевому адресу размещается f(xo), а во втором блоке 6 памяти по этому же адресу размещается f(x2), по первому адресу в первом блоке размещается значение функции fCx), а во второмf(x) и т.д. Принцип работы устройства для вычисления стандартных функций заключается в следующем. Если дискретный аргумент х некоторой функции f(x) принимает значения в точках Xg , S 0,,8,... ,,..., то соответствующее значение функции f(xg) выбирается из первого блока 5 памяти. Если аргумент х принимает значения в точках Xg, 2,6,10,... ,,..., то соответствующее значение функции f (xg) выбирается из второго блока 6 памяти. Если аргумент х принимает значения в точках Х,,3,5,...2j.+1,..., то соответствующее значение функции f(xj,,) вычисляется по формуле f(x) jCf(xy,.) + f(x)J (1) При этом значения функций f(xy,) и f(. выбираются одновременно из первого и второго блоков памяти. Если аргумент принимает значения в точках Ху,€Х, значения индекса у которых г 3,7,11,15,..., то Ъначение функции f{x) выбирается из второго блока 6 памяти, а значения функции f(xJ„)-из первого блока 5 памяти. Причем значение f(xL.) из первого блока памяти 5 выбирается по адресу на единицу больше того адреса, по которому выбирается значение f(xj,) из второго блока 6 памяти. Таким образом, производится линейная аппроксимация значений функции в точках х е Х, г 1,3,5, ...,2j,+1,.. V по значениям функции в точках Xj, € Х,и ). При этом точность воспроизведения функции не хуже, чем при использовании известного кусочнопостоянной аппроксимации. Режим выработки табличного значения функции из одного или двух блоков памяти одновременно, а также настройка режимов работы сумматора 7, сумматора адреса и мультиплек7сора 8 определяются комбинацией дву младших разрядов аргумента согласно таблице истинности. Устройство работает следующим об разом. Аргумент X в прямом коде заносится в регистр 1. В зависимости от комбинации двух младших разрядов регистра 1 на выходах дешифратора 2 появляются соответствующие управляющие сигналы, которые обеспечивают логику работы устройства согла но таблице истинности. Если значение двух младших разрядов регистра 1 равно 00, т.е. ,,8, .. . .., , то на первом выходе дешифратора 2 появляется сигнал, по ступающий на первый управляющий вход 9 сумматора 7, настраивая последний на сквозную передачу информации с шины А. Одновременно содерж мое остальных разрядов регистра 1 пройдя через сумматор , поступает на адресные входы первого блока 5 пймяти, из которого выбирается соответствующее значение функции f {X5)G Y., ,i,8, .. .it, ... ,, которое через сумматор 7 поступает на входы мультиплексора 8, который настроен на передачу информации без сдвига .через первую группу входов. С выхода мультиплексора б выбранное значение функции поступае на входы выходного регистра 13, с в ходов которого передается в арифметическое устройство для дальнейшей обработки. Если значение двух младших разря дов регистра 1 равно 0,1, т.е. Х|,е Х , г 1,,13..., то в этом случае единичный сигнал с выхода младшего разряда регистра 1 через открытый элемент 3 запрета поступае на управляющий вход мультиплексора 8, настраивая последний на передачу информации со сдвигом на один разряд вправо, т.е. через вторую группу входов. Одновременно из первого и второго блоков памяти выбирается пара значений функций f(xj, .) и f(), которая поступает на первую и вторую группы входов сумматор 7, где происходит арифметическое сложение. Результат сложения переда ется через мультиплексор 8 со сдвигом на один разряд- вправо, что соответствует делению на два, и заносится в выходной регистр 13. Таким 2 реализуется преобразоваобразомние 1. Если значение двух младших разрядов регистра 1 равно 10, т.е. XgeXo, ,6,10,...,2H-t, .. .,, то на втором выходе дешифратора 2 появляется сигнал, который поступает на первый вход элементаИЛИ. С выходе последнего единичный сигнал поступает на вход 10 сумматора 7, настраивая его на передачу информации с шины В. Одновременно из второго блока 6 памяти выбирается соответствующее значение функции f(xe )е Y|-, b2,6,10,...2+i, ...2-2, которое через сумматор 7 и мультиплексор 8 поступает на входы регистра 13Если в двух младших разрядах регистра 1 содержится код 11, . , ,7,11,...,, то на третьем выходе дешифратора 2 появляется сигнал, который поступает на вход переноса сумматора k адреса. В результате на адресных входах первого блока 5 памяти появляется значение адреса на единицу больше значения адреса в старших разрядах регистра 1, которое поступает на адресные входы второго блока 6 памяти. Из первого 5 и второго 6 блоков памяти выбирается пара значений функции f(xy,) и f(xj,). Одновременно единичный сигнал с выхода младшего разряда регистра 1 через открытый элемент 3 запрета поступает на управляющий вход 12 мальтиплексора 8, настраивая последний на передачу информации со сдвигом на один разряд вправо. Выбранные значения функций из блоков 5 и 6 памяти поступают на первую и вторую группы входов сумматора 7. Результат арифметического сложения передается со сдвигом на один разряд вправо через мультиплексор 8 в регистр 13, что соответствует делению суммы на два. В случае, когда аргумент х принимает максимальное значение, на третьем выходе дешифратора 2 вырабатывается единичный сигнал, который поступает на вход переноса сумматора i адреса. Сигнал с выхода переноса сумматора поступает на второй вход элемента ИЛИ и инверсный вход элемента 3 запрета, блокируя Прохождение единичного сигнала с выхода младшего разряда регистра 1. Единичт ный сигнал с выхода элемента ИЛИ 9/9 поступает на вход 10 сумматора 7 и настраивает его на режим сквозной передачи информации по шине В. Одновременно из Bfoporo блока 6 памяти выбирается значение функции, кото рое через сумматор 7 и мультиплексор 6 поступает на вход регистра 13. Таким образом, предлагаемое устройство по сравнению с известным 2i 10 позволяет повысить быстродействие, так как табличное значение стандартной функции вычисляется за один-два такта ycтpoйctвa при той же точности Вычислений. Кроме того, предлагаемое устройство обладает регулярностью структуры, технологично, а также свободно от других недостатков, присущих прототипу.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций табличным методом | 1983 |

|

SU1153320A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Устройство для формирования адресов табличных функций | 1974 |

|

SU518770A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Устройство для реализации логических функций | 1989 |

|

SU1619247A1 |

| Цифровой функциональный преобразователь | 1982 |

|

SU1024894A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Интерполятор | 1983 |

|

SU1129622A1 |

Формула изобретения Устройство для вычисления стандартных функций, содержащее регистр аргумента, первый блок памяти, сумматор и выходной регистр, при этом вход устройства соединен с входом регистра аргумента, отличающееся тем, что, с целью повышения быстродействия, оно содержит дешифратор, элемент запрета, сумматор адреса, второй блок памяти, мультиплексор и элемент ИЛИ, причем выходы двух младших разрядов регистр аргумента соединены с входами дешифратора, а выходы старших разрядов с входами сумматора адреса и второго блока памяти, выходы суммы сумматора адреса подключены к входам-первого блока памяти, а выход перенйса - к первому входу элемента ИЛИ и инверсному входу элемента запрета, прямой вход которого подсоединен к выходу первого регистра аргумента, первая и вторая группы информационных входов сумматора соединены с выходами соответственно первого и второго блоков памяти, первый управляющий входс первым выходом дешифратора, а второй управляющий вход - с выходом элемента ИЛИ, второй вход элемента ИЛИ подключен к второму выходу дешифратора, третий выход которого подключен к входу переноса сумматора адреса i-и вход первой группы и 1+1-и вход второй группы мультиплексора соединены с i-м выходом сумматора, где lii 5п, п -число входов первого или второго блока памяти, выход переноса сумматора соединен со старшим входом второй группы входов мультиплексора, выходы мультиплексора подключены к входам выходного ре-, гистра, а управляющий вход мульти119 2032 .12

плексора - к выходу элемента запре- 1 . Авторское свидетельство СССР та, при этом выходы выходного регист- № «53739, кл. СПС 17/00, 197+. ра соединены с выходами устройства. 2. Авторское свидетельство СССР

Источники информации,№ 518770, кл.С Об F 9/00, 1976

принятые во внимание при экспертизе s (прототип).

Авторы

Даты

1982-07-07—Публикация

1980-10-24—Подача