- iП

Изобретение относится к вычислительной технике и может быть использовано для вывода графической информация из ЭВМ.

Цель изобретения - повышения быстродействия за счет сокращения времени стирания изображения на экране.

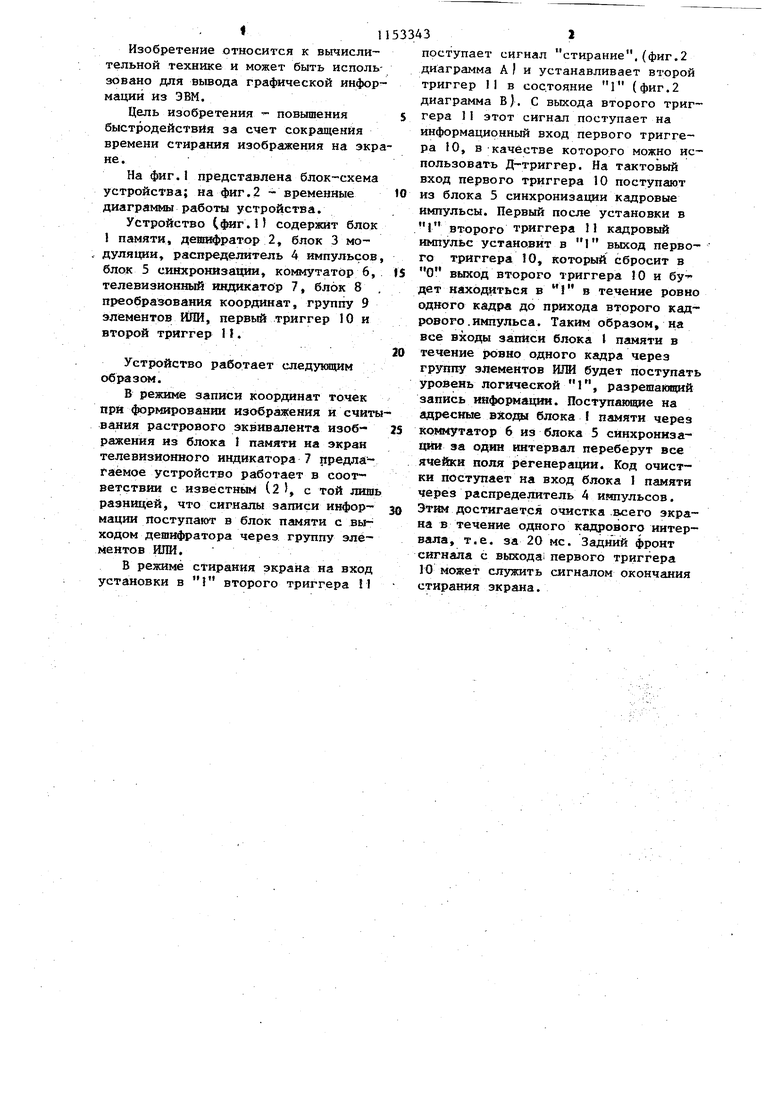

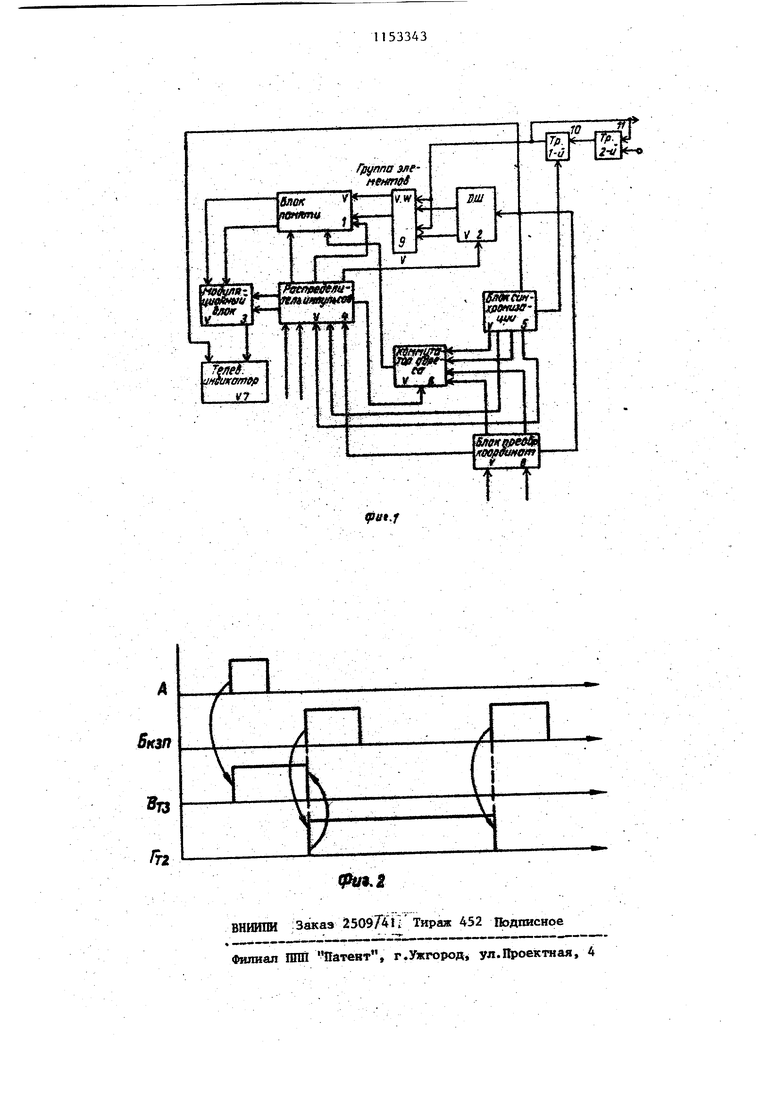

На фиг.1 представлена блок-схема устройства; на фиг.2 - временные диаграммы работы устройства.

Устройство Сфиг.1) содержит блок памяти, дешифратор 2, блок 3 модуляции, распределитель 4 импульсов, блок 5 синхронизации, коммутатор 6, телевизионный иадщкатор 7, блок 8 , преобразования координат, группу 9 элементов ИЛИ, первый триггер 10 и второй триггер П.

Устройство работает следующим образом.

В режиме записи координат точек при формировании изображения и считывания растрового эквивалента изображения из блока 1 памяти на экран телевизионного индикатора 7 предлагаемое устройство работает в соответствии с известным (2 J, с той лишь разницей, что сигналы записи информации поступают в блок памяти с выходом дешифратора через группу элементов ШШ.

В режиме стирания экрана на вход установки в второго триггера 1

33432

поступает сигнал стирание,(фиг.2 диаграмма А I и устанавливает второй триггер Н в сос.тояние 1 (фиг.2 диаграмма В). С выхода второго триггера 11 этот сигнал поступает на информационный вход первого триггера 10, в качестве которого можно использовать Д-триггер. На тактовый вход первого триггера 10 поступают

0 из блока 5 синхронизации кадровые импульсы. Первый после установки в I второго триггера 11 кадровый импульс установит в 1 выход первого триггера 10, который сбросит в

5 О выход второго триггера 10 и бу- дет находиться в в течение ровно одного кадра до прихода второго кадрового, импульса. Таким образом, на все входы записи блока I памяти в

0 течение ровно одного кадра через

группу элементов ШМ будет поступать уровень логической 1, разрешакщий запись информации. Поступанщие на адресные блока { памяти через

5 коммутатор 6 из блока 5 синхронизации за один интервал переберут все ячейки поля регенерации. Код очистки поступает на вход блока 1 памяти через распределитель 4 импульсов.

0 Этим достигается очистка-в :его экрана в течение одного кадрового интервала, т.е. за 20 мс. Задний фронт сигнала с выхода первого триггера 10 может служить сигналом окончания стирания экрана.

-о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения графической информации | 1987 |

|

SU1474724A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1403091A1 |

| Устройство для вывода графической информации | 1986 |

|

SU1399809A1 |

| Устройство для отображения графической информации на телевизионном индикаторе | 1986 |

|

SU1374272A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для вывода графической информации | 1979 |

|

SU930355A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для вывода графической информации | 1986 |

|

SU1403092A1 |

| Устройство для вывода графической информации | 1984 |

|

SU1238143A1 |

yCTP(rfiCTBO ДЛЯ ВЫВОДА ГРАШЧЕСКОЙ ИНФОРМАЦИИ, содержащее блок памяти, блок синхронизации, блок модулящии, распределитель импульсов, коммутатор, блок преобразования координат, деш1фратор, телевизионный индикатор, первый .вход которого соединен с первым выходом блока синхронизации, второй, третий, четвертый н пятаА выходы которого соединены соответственно с первым и вторым входами коммутатора и втбрым и тpeть им входами распределителя импульсов, первый выход которого соединен с пятым входом коммутатора, третий и четвертый входы которого соедш1ены соответственно со вторым и третьим выходами блока преобразования координат, четвертый выход которого соединен с первым входом распределителя импульсов, второй выход которого соединен со вторым входом дешифратора, первый вход которого соединеи с первым выходом блока преобразования координат, первый и второй входы которого являются первым и вторым входами устройства, второй вход телевизнойного индикатора соединен с выходом блока модуляции, входы груптш которого соединены с выходами блока памяти, первый и второй входы которого соединены соответственно с третьим и четвертым выходами распределителя импульсов, пятый и иестой выходы которого соединены соответственно с первьм и BTopt 4 входами блока модуляции , выход коммутатора соединен с третьим входом блока па:мятн, четвертый и пятый входы распределителя импульсов являются соответственно третьим и четвертым входами устройства, отличающееся тем, что, с целью повышения быстродействия устройства за счет сокращения времени стирания изображения на экране, в него введены первый и второй трнггеры н элементы ШШ, выходы которых i соединены с входами группы блока пасл мяти, выходы дешифратора соединены ; :Р со ВТО1ШМИ входами элементов ИЛИ, &э «k первые входы которых соединены с выходом первого триггера и первым вхо дом второготриггера, выход котороРО го соединен с первым входом первого триггера, второй вход которого сое- i динен с шестым выходом блока сиихро- низации, второй вход второго триггера яв1ляется пятым входом устройства, выход 1юрвого триггера является выходом устройства.

| Устройство для отображения информации | 1975 |

|

SU543960A1 |

| Устройство для вывода графической информации | 1979 |

|

SU930355A1 |

Авторы

Даты

1985-04-30—Публикация

1984-02-10—Подача