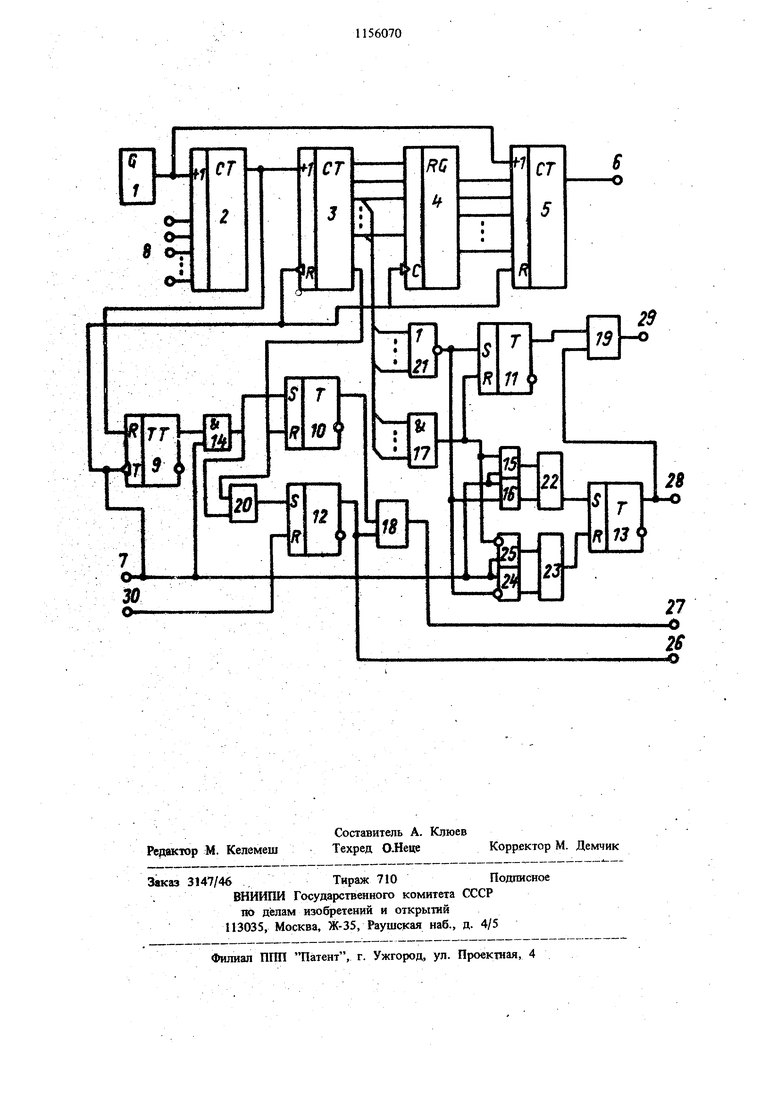

Изобретение относится к вычислительной технике и может 11спользоваться в вычислител ных устройствах и системах автоматического управления для преобразования данных в частотно-импульсном коде. Известно устройство для умножения частоты на код, содержащее два счетчика и управл емый делитель 1 . Недостаток известного устройства заключает ся в отсутствии контроля входной частоты. Известно также устройство для умножения частоты на код, содержащее генератор тактовых импульсов, два управляемых делителя, счетчик, регистр, причем выход генератора так товых импульсов соединен с информационными входами первого и второго управляемых делителей, входы управления которых соединены, соответственно с входом задатая коэффициента умножения устройства и выходом регистра, информационные входы которых соединены с соответствующими выходами разрядов счетчика, счетный вход которого сое динен с выходом первого управляемого делителя, тактовый вход регистра соединен с входом сброса счетчика и является входом .задания частоты устройства, выход которого соединен с выходом второго делителя частоты 2. Однако отсутствие контроля за выходом частоты входного сигнала за допустимые пред лы в данном устройстве может привести к по явлению недиагностируемь х ошибок в функци онировании. Цель изобретения - повышение точности путем обеспечения контроля нахождения частоты входного сигнала в допустимых пределах. Поставленная цель достигается тем, что устройство для умножения частоты на код, содержащее генератор тактовых импульсов, два управляемых делителя, счетчик и регистр причем выход генератора тактовых импульсов соединен с информационными входами первого и второго управляемых делителей, входы управления которых соединены соответственно с входом задания коэффициента умножения устройства и выходом регистра, информацион ные входы которого соединены с соответству щими выходами разрядов счетчика, счетный вход которого соединен с выходом первого управляемого делителя, тактовый вход регист ра соединен с входом сброса счетчика и является входом задания частоты устройства, выход которого соединен с выходом второго детггеля частоты, содержит пять триггеров, . шесть элементов И, два элемента запрета, чет ре элемента ИЛИ, причем вход задания часто устройства соединен со счетным входом первого, второго и третьего элементов И, информаиионными входами первого и второго элементов запрета, входом сброса второго управляемого делителя, вход сброса и прямой выход первого триггера соединены соответственно с выходом первого управляемого делителя и вторым входом первого элемента И, выход которого соединен с входом установки второго триггера и первым входом первого элемента ИЛИ, второй вход которого соединен с входом сброса второго триггера и выходом прекоса счетчика, выходы старших разрядов которого соединены с соответствуюишми входами четв)того элемента И и второго элемента ИЛИ, инверсный выход которого соединен с установочным входом третьего триггера, вторым входом третьего элемента И и управляющим входом первого элемента запрета, выход первого элемента ИЛИ соединен с установочным входом четвертого триггера, вход сброса которого соединен с входом сброса устройства, выход ошибки которого соединен с прямым выходом четвертого триггера и первым входом пятого элемента И, выход и второй вход которого соединены соответственно с выходом вида ошибки устройства и прямым выходом второго триггера, выход четвертого элемента И соединен с входом сброса третьего триггера, вторым входом второго элемента И и управляющим входом второго элемента запрета, выходы второго и третьего элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого соединен с входом установки пятого триггера, выходы первого и второго элементов запрета соединены с соответствующими входами четвертого элемента ИЛИ, выход которого соединен с входом сброса пятого триггера, выход которого соединен с первым входом шестого элемента И и является выходом сигнала предупреждения устройства, выход третьего триггера соединен с вторым входом шестого элемента И, выход которого является выходом вида сигнала предупреждения устройства. На чертеже показана структурная схема устройства для умножения частоты на код. Устройство для умножения частоты на код содержит генератор 1 тактовых импульсов, первый управляемый делитель 2, счетчик 3, регистр 4, второй управляемый делитель 5, .выход 6 устройства, вход 7 задания частоты устройства, вход 8 задания коэффициента умножения устройства, триггеры 9-13, элементы И }4-Г9, элементы ИЛИ 20-23, элементы . запрета 24 и 25, выходы 26-29 ошибки, вида ошибки, сигнала предупреждения и вида сигнала предупреждения, вход 30 сброса устройства. Устройство для умножения частоты на код работает следующим образом. Перед ьачалом работы сигналом, подаваемы на вход 30, устройство устанавливается в исходное состояние. При этом триггер 12 находится в иулевом состоянии, и на его прямом выходе нулевой сигнал, поступающий на выход 26, что свидетельствует об отсутствии ощибки. Входной частотный сигнал подается на вход 7 и первым импульсом обеспечивает сброс счетчика 3 и управляемого делителя 5. Код N , на который необходимо умноукип частотный сигнаг, подается на вход 8. Управляемый делитель 2 обеспечивает деление выходного сигнала генератора 1 f н N и импульсы С выхода управляемого делителя 2 поступают иа счетчик 3, который за время между импульсами входной частоты равное 1/f, зафиксирует код М --V . Следу ющим импульсом входной частоты по переднему фронту код М переписывается в регист 4, а по заднему фронту счетчик 3 и управля емый делитель 5 сбрасываются в нулевое сос тояние. Делитель 5 обеспечивает деление частоты f.f на М, т.е. формирует на выходе 6 сигнал с частотой f - N -f. По заднему фронту первого импульса входной частоты триггер 9 переключается в единичное состояние, а импульсом с выхода управляемого делителя 2 триггер 9 устанавливается в нулевое состояние. Если частота входных импульсов превышает допустимый предел, за время между импульсами входной частоты не успеет сформироваться ни одного импульса на выход управляемого делителя 2 и ко време{Ш появления второго импульса на входе 7 триггер 9 будет в единичном состоянии. При этом импульс входной частоты пройдет через элементы И 14 и ИЛИ 20, устанавливая триггер 12 в единичное состояние, что соответствует выходу сигнала за допустимые пределы, о чем свидетельствует появление единичного логического сигнала на выходе 26. Одновременно триггер 10 устанавливается этим же импульсом в единичное состояние, что свидетельствует о том, что f больше максимально допустимой, что индицируется единичным логическим сигналом на выходе 27. Если f меньше минимально допустимой величины, за время между импульсами опорной частоты произойдет переполнение счетчика 3, сигналом с выхода переноса которого триггер 12 также будет установлен в единичное состояние, а триггер 10 в нулевое состояние, что вызовет появление единичного и нулевого сигналов на выходах 26 и 27 соответственно, показывающих наличие и вид сбоя в работе устройства. Состояние, свидетельствующее о наличии ощибки сохраняется до задания оператором или внешним устройством сигнала сброса на входе 30. Если частота импульсов приближается к минимально или максимально допустимым значениям, все старщие разряды счетчика 3 будут соответственно в единичном или нулевом состоянии, что приводит к появлению единичных сигналов на выходах элементов соответственно И 17 или ИЛИ 21, устанавливающих триггер 11 в нулевое или единичное состояние соответственно. При этом следующим импульсом входной частоты триггер 13 установится в единичное состояние, что вызовет появление единичного сигнала на выходе 28, который показывает, что f приближается к граничным значениям. При этом вид этого граничного значения фиксируется сигналом на выходе 29. Если f в дальнейшем изменится, отдаляясь от граничных значений следующими импульсами, поступающими на вход 7 и проходящими через элемент ИЛИ 23, триггер 13 устанавливается в нулевое состояние и сигнал подхода к допустимой rpaimue исчезает. Положительный эффект изобретения относительно прототипа состоит в том, что в предложенном устройстве обеспечивается как контроль за п{исближением частоты опорных импульсов к допустимым пределам, так и контроль за выходом частоты за допустимые пределы, что позволяет ис кчючить нерегистрируемые ошибки и своевременно принять меры по контролю за источником опорных импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения частоты на код | 1983 |

|

SU1206780A1 |

| Генератор нестационарного случайного импульсного процесса | 1987 |

|

SU1587501A1 |

| Устройство для синхронизации вычислительной системы | 1988 |

|

SU1552165A1 |

| Программно-управляемый модуль | 1986 |

|

SU1405028A1 |

| Устройство программного управления | 1984 |

|

SU1246055A1 |

| Устройство контроля и диагностики состояний технического объекта | 1987 |

|

SU1504653A1 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

| Умножитель частоты | 1990 |

|

SU1775840A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1991 |

|

RU2024924C1 |

| Генератор случайного процесса | 1982 |

|

SU1087991A1 |

УСТЮЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТЫ НА КОД, содержащее генератор тактовых импульсов, два управляемых делителя, счетчик и регистр, причем выход генера-, тора тактовых импульсов соединен с информационными входами первого и второго управляемых делителей, входы управления которых соединены соответственно с входом задания коэффициента умножения устройства и выходом регистра, информационные входы которого соединены с соответствующими выходами разрядов счетчика, счетный вход которого соединен с выходом первого управления делнтепя, тактовый вход регистра соединен с входом сброса счетчика и является входом задания частоты устройства, выход которого соединен с выходом второго делнтеля часто1Ы, отличающееся тем, что, с целью повышения точности путем обеспечения контроля нахождення частоты входного сигнала в допустимых пределах, оно содержит пять фиггеров, шесть элементов И, два элемента запрета, четыре элемента ИЛИ, причем вход задания частоты устройства соединен со счетным входом первогс триггера, первыми входами первого, второго и третьего элементов И, информационными входам первого и второго элементов запрета, входом второго управляемого делнтеля, вход сброса и прямой выход первого триггера соединены соответственно с выходом первого угтравля емого делителя и вторым входом первого элемента И, выход которого соединен с входом установки второго триггера и первым входом первого элемента ИЛИ, второй вход которого соединен с входом сброса второго триггера и выходом переноса счетчика, выходы старших разрядов которого соединены С соответствующими входами четвертого элемента И и второго элемента ИЛИ, инверсный выход которого соединен с установочным входом третьего триггера, вторым входом третьего элемента И и управляюидам входом первого элемента запрета, выход первого элемента ИЛИ соединен с установочным входом четвертого триггера, вход сброса котою рого соединен с входом сброса устройства, выход ошибки которого соединен с пpямы выходом четвертого триггера и первым входом пятого элемента И, выход и второй вход которого соединены соответственно с выходом вида ошибки устройства и прямым выходом второго триггера, выход четвертого элемента И соединен с входом сброса третьего триггера, вто- ел рым входом второго элемента И и управляю- о шим входом второго элемента запрета, выходы второго и третьего элементов И соединены соч ответственно с первым И вторым входами третьего элемента ИЛИ, выход которого соединен с входом установки пятого триггера, выходы первого и второго элементов запрета соединены с соответствующими входами четвертого элемента ИЛИ, выход которого соединен с входом сброса пятого триггера, выход которого соединен с первым входом шестого элемента И и является выходом сигнала предупреждения устройства, выход третьего триггера соединен с вторым входом шестого элемента И, выход которого является выходом вида сигнала щ едупрежденш1 устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой следящий умножитель частоты | 1977 |

|

SU634277A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство умножения частоты на код | 1976 |

|

SU580555A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-15—Публикация

1983-10-28—Подача