Изобретение относится к технической кибернетике и предназначено для распознания аварийных состояний объектов контроля.

Цель изобретения - повышение быст- родействия и надежности устройства.

Суть изобретения заключается в следующем.

При контроле работающего объекта, если ни один из измеряемых параметров не вьпиел за пределы пороговых значений, известное устройство классифицирует состояние объекта контроля как нормальное. Вместе с тем существует целый ряд опасных состояний, которые характеризуются сравнительно медленным изменением параметров. В этих случаях достижение порогйвых уровней произойдет через длительное время, что снижает быстродействие и достоверность системы контроля. Снижение пороговых значений приводит к ошибкам

распознавания. Согласно изобретению наряду с контролем параметров по допускаемым пороговым значениям осуществляется контроль изменения параметров во времени. Эти изменения сравниваются с эталонными значениями, а результаты сравнения используются для оценки текущего состояния работающего объекта и для прогнозирования возможной аварии задолго до того момента, когда какой-либо медленно меняющийся параметр выйдет за свои допустимые пределы и авария станет неизбежной.

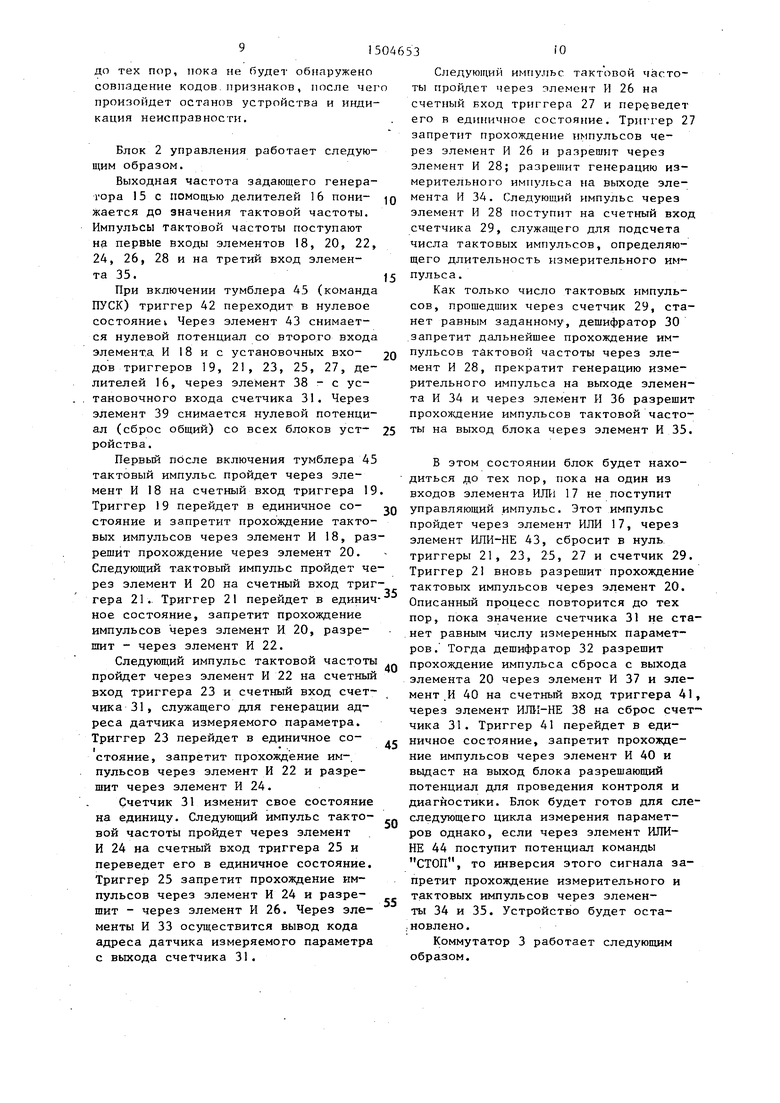

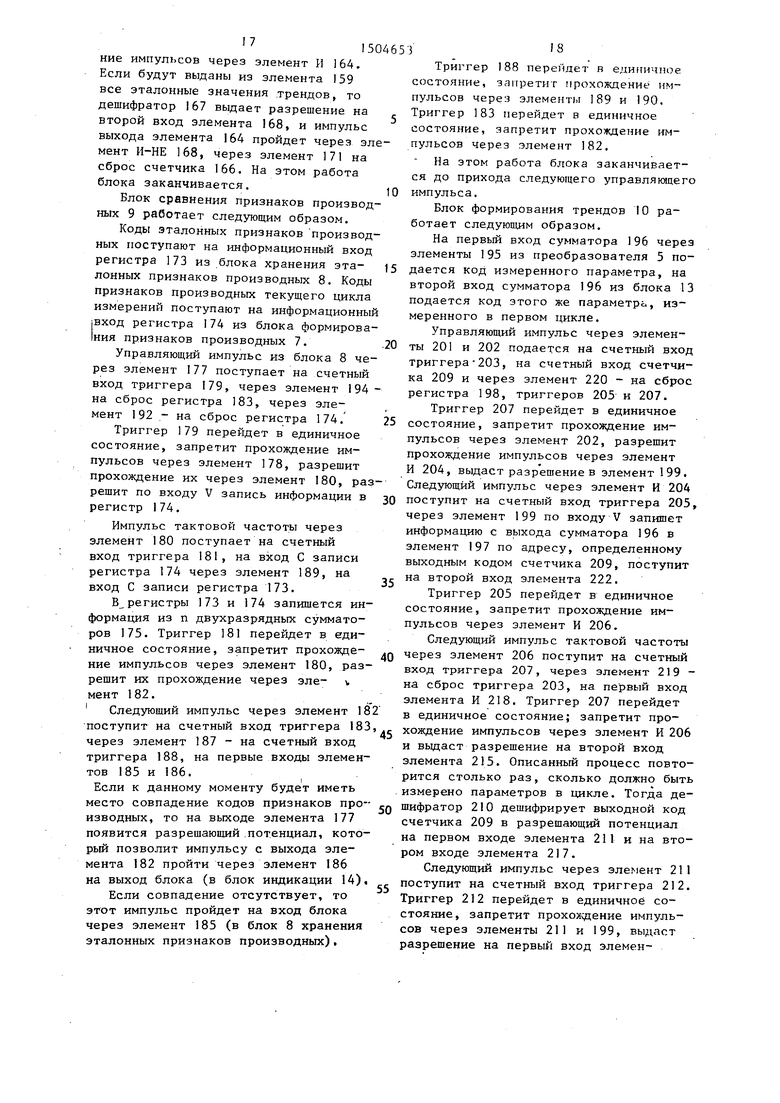

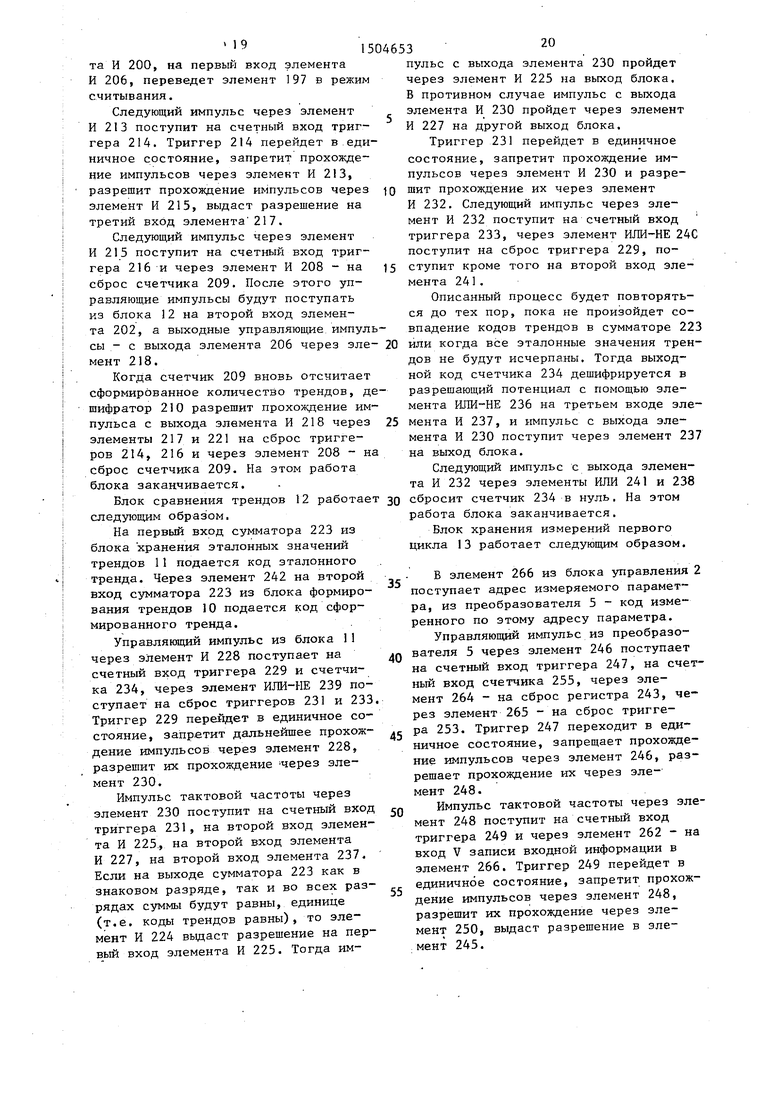

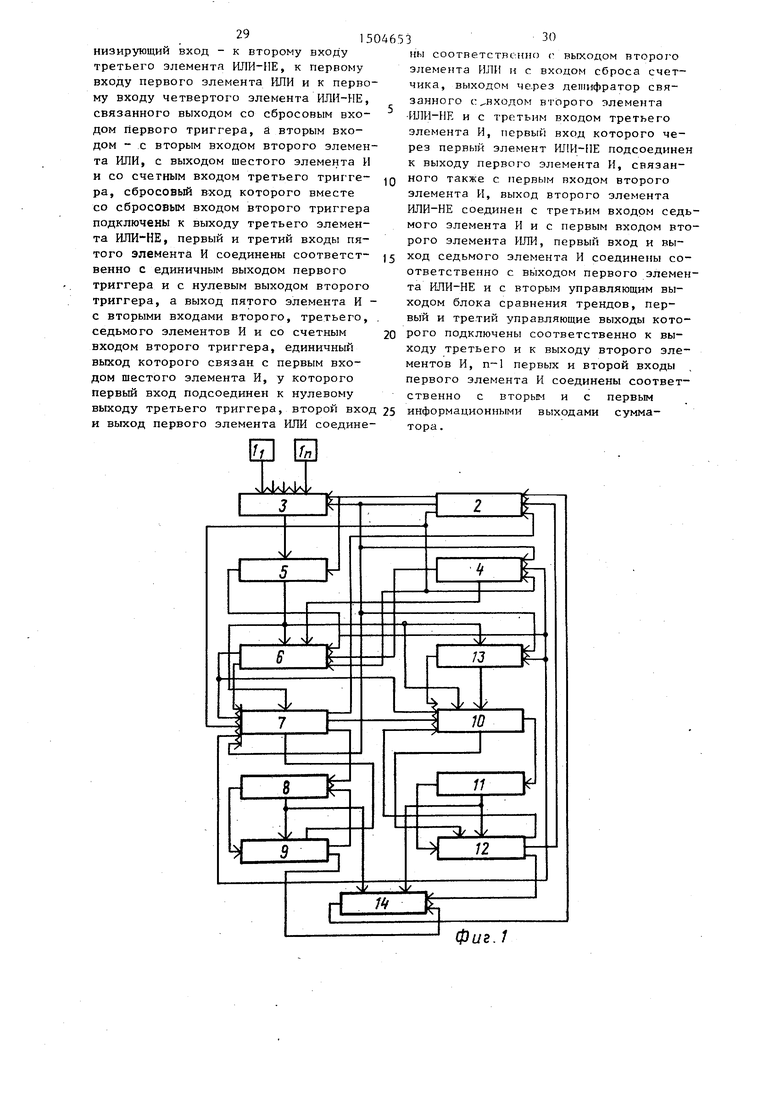

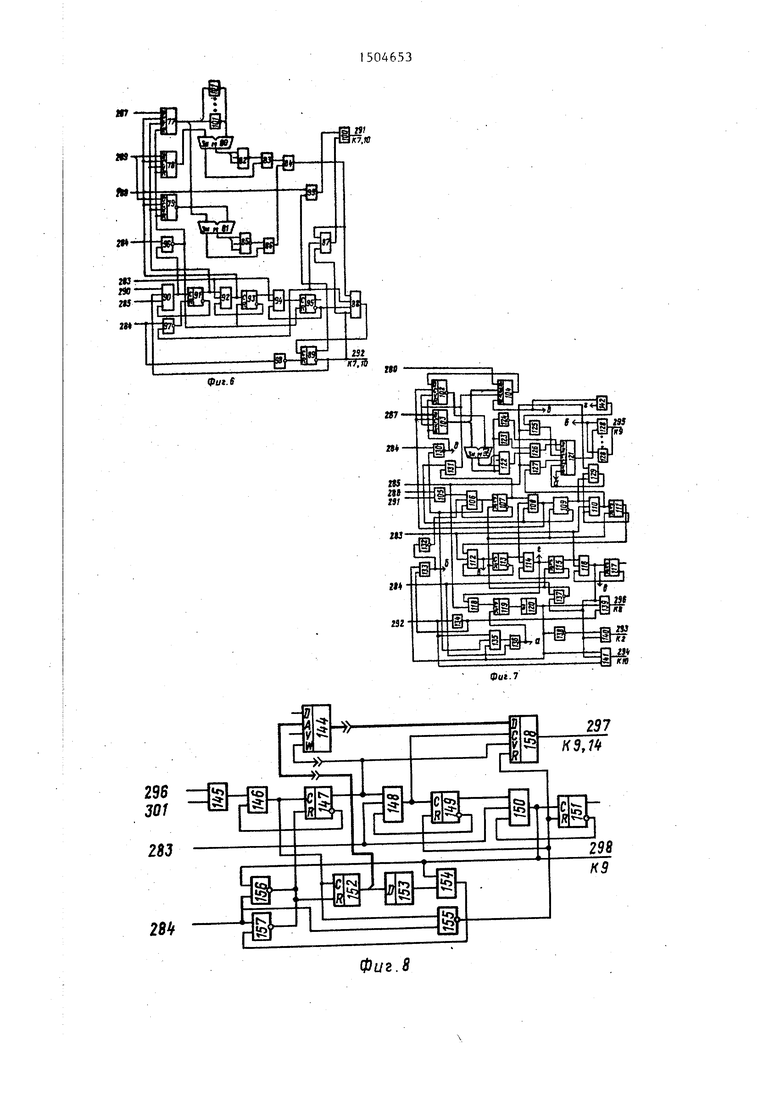

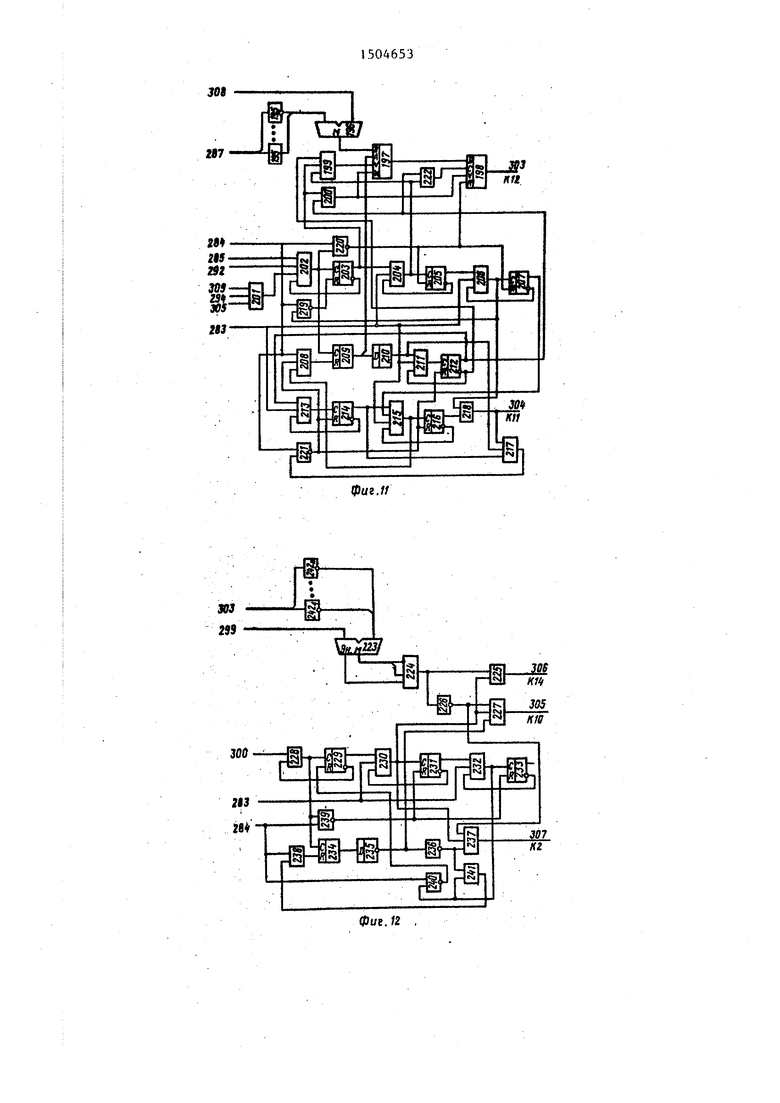

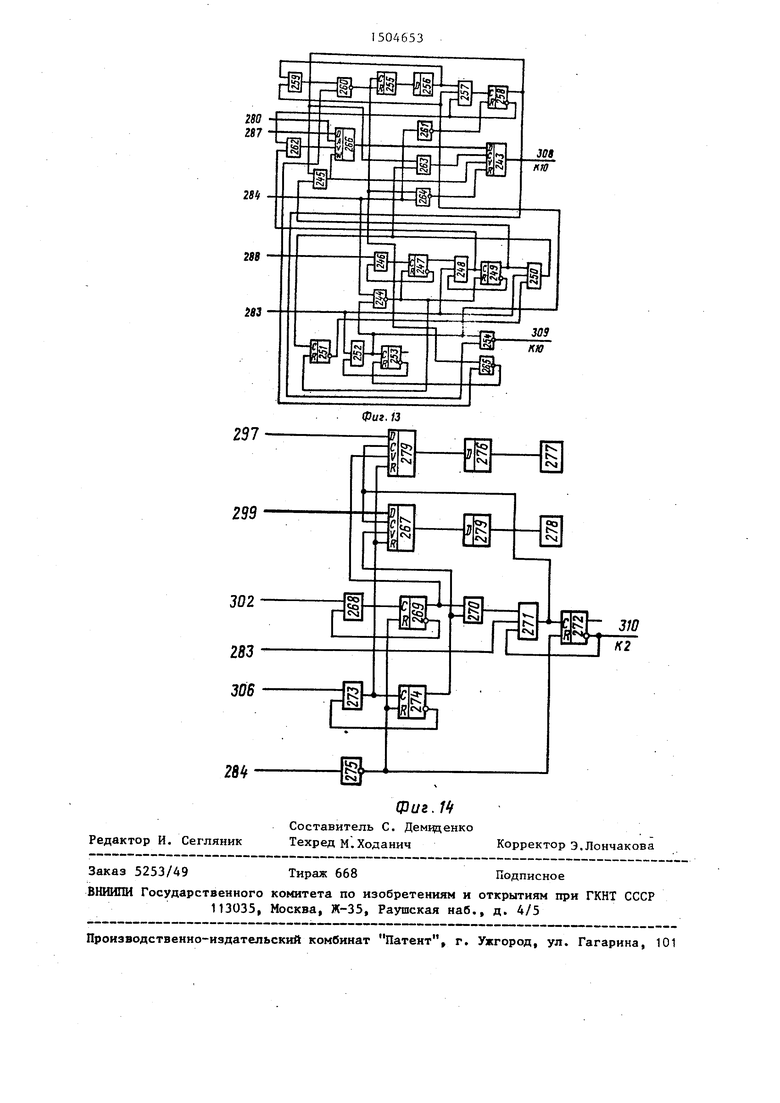

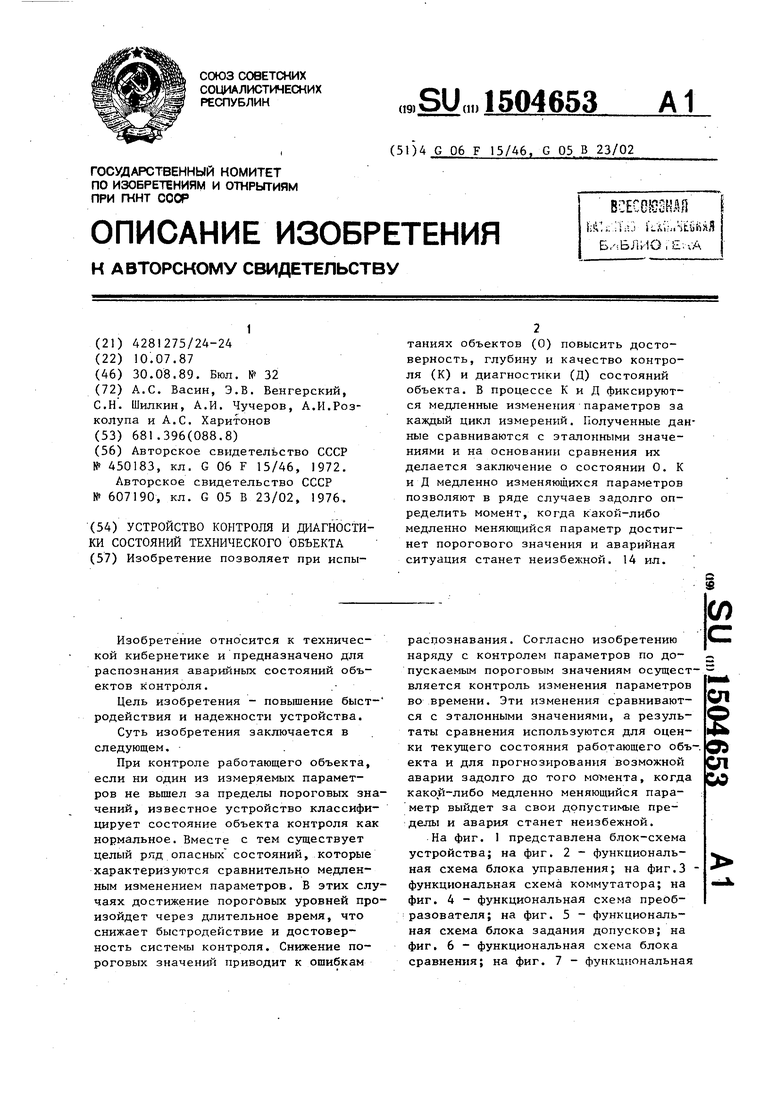

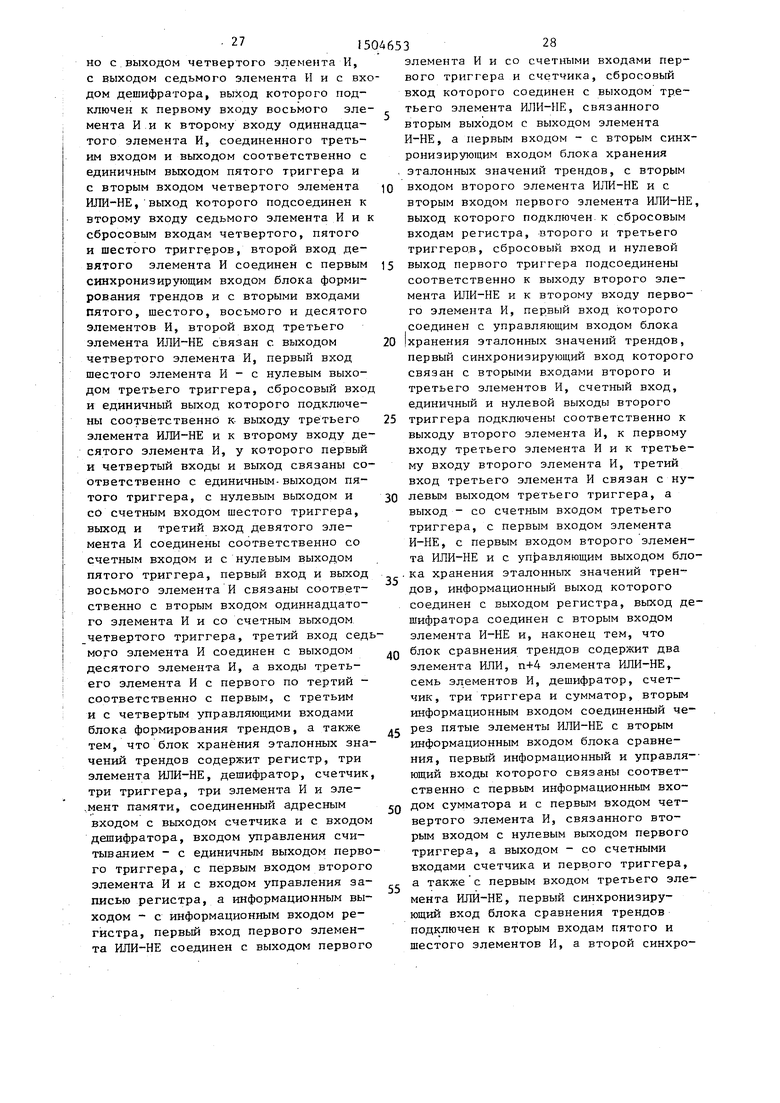

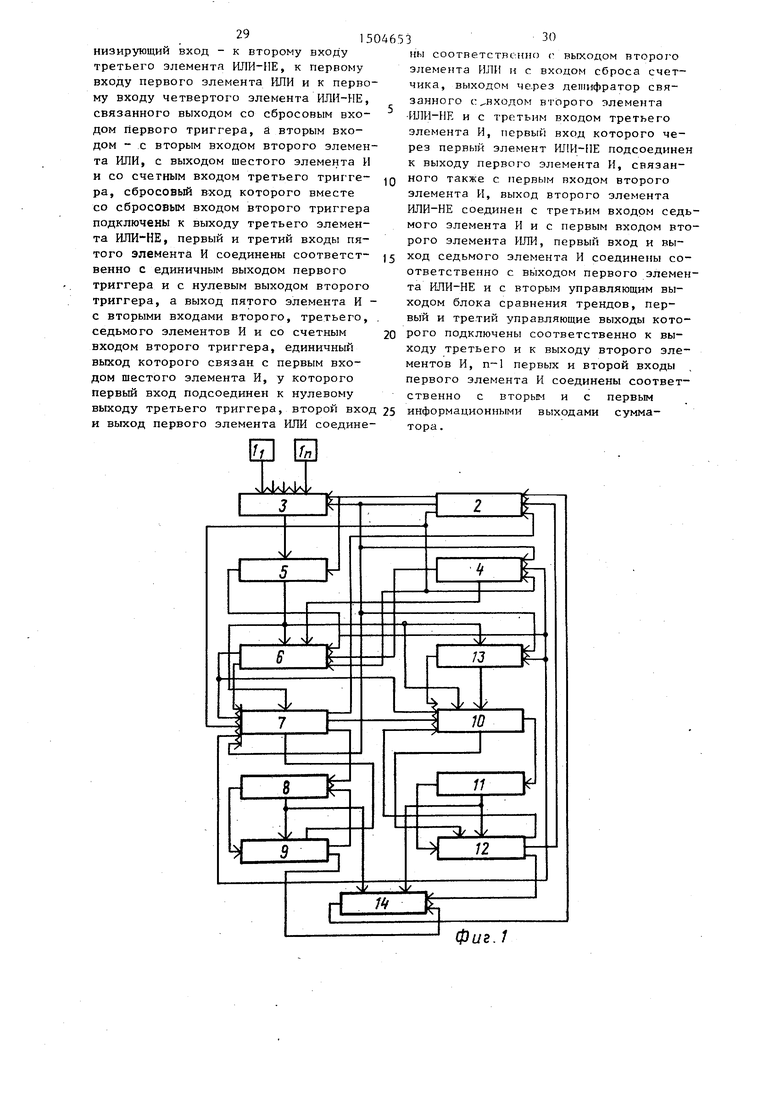

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - функциональная схема блока управления; на фиг.З - функциональная схема коммутатора; на фиг. 4 - функциональная схема преобразователя; на фиг. 5 - функциональная схема блока задания допусков; на фиг, 6 - функциональная схема блока сравнения; на фиг. 7 - функциональная

(Л

С

ел

Од

СП

ее

схема блока формирования признака производной; на фиг. 8 - функциональная схема блока хранения эталонных признаков производных; на фиг. 9 - фнукциональная схема блока хранения эталонных значений трендов; на фиг.10- функциональная схема блока сравнения признаков производных; на фиг. 11

триггер 57, четвертый элемент И 58, третий тригг ер 59, 1зТорой элемент ИЛИ 60, и второй элемент ИЛИ-ЦЕ 61. Блок 4 задания допусков, (фиг. 5) содержит первый регистр 62, сменный элемент 63 запоминания, второй .64 и третий 65 регистры, первый элемент И 66, первый триггер 67, второй зла

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики состояний объекта | 1989 |

|

SU1679468A1 |

| Устройство для моделирования вычислительной системы | 1990 |

|

SU1786492A1 |

| Устройство для обслуживания запросов | 1990 |

|

SU1805467A1 |

| Устройство контроля состояния объектов | 1985 |

|

SU1366993A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| УСТРОЙСТВО ПОИСКА НИЖНЕЙ ОЦЕНКИ РАЗМЕЩЕНИЯ В ПОЛНОСВЯЗНЫХ МАТРИЧНЫХ СИСТЕМАХ ПРИ ДВУНАПРАВЛЕННОЙ ПЕРЕДАЧЕ ИНФОРМАЦИИ | 2008 |

|

RU2421805C2 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

| Адаптивное устройство для защиты памяти | 1983 |

|

SU1103291A1 |

Изобретение позволяет при испытаниях объектов (О) повысить достоверность, глубину и качество контроля (К) и диагностики (Д) состояний объекта. В процессе К и Д фиксируются медленные изменения параметров за каждый цикл измерений. Полученные данные сравниваются с эталонными значениями и на основании сравнения их делается заключение о состоянии О. К и Д медленно изменяющихся параметров позволяют в ряде случаев задолго определить момент, когда какой-либо медленно меняющийся параметр достигнет порогового значения и аварийная ситуация станет неизбежной. 14 ил.

функциональная схема блока формирова- ю мент И 68, второй триггер 69, третий

ния трендов; на фиг. 12 - функциональная схема блока сравнения трендов; на фиг. 13 - функциональная схема блока хранения изменений первого цикла; на фиг. 14 - функциональная схема бло-15 ка индикации.

На фиг. 1 обозначены датчики Ц-1, блок 2 управления, коммутатор 3,

Блок 6 сравнения (фиг. 6) включа ет регистр 77, 78 и 79 с первого по третий, первый 80 и второй 81 сумма торы, первый инвертор 82, первый эл мент И 83, первый элемент ИЛИ 84, блок 4 задания допусков, аналого-цифровой преобразователь 5, блок 6 срав-20 второй инвертор 85, второй элемент нения, блок 7 формирования признака И 86, второй элемент ИЛИ 87, третий

производной, блок 8 хранения эталонных признаков производных, блок 9 сравнения признаков производных.

элемент И 88, первый триггер 89, четвертый элемент И 90, второй триггер 91, пятый элемент И 92, третий

блок 10 формирования трендов,блок 1 1 - 25 триггер 93, шестой элемент И 94, четхранения эталонных значений трендов,, блок 12 сравнения трендов, блок 13 хранения измерений первого цикла,

блок 14 индикации.

I

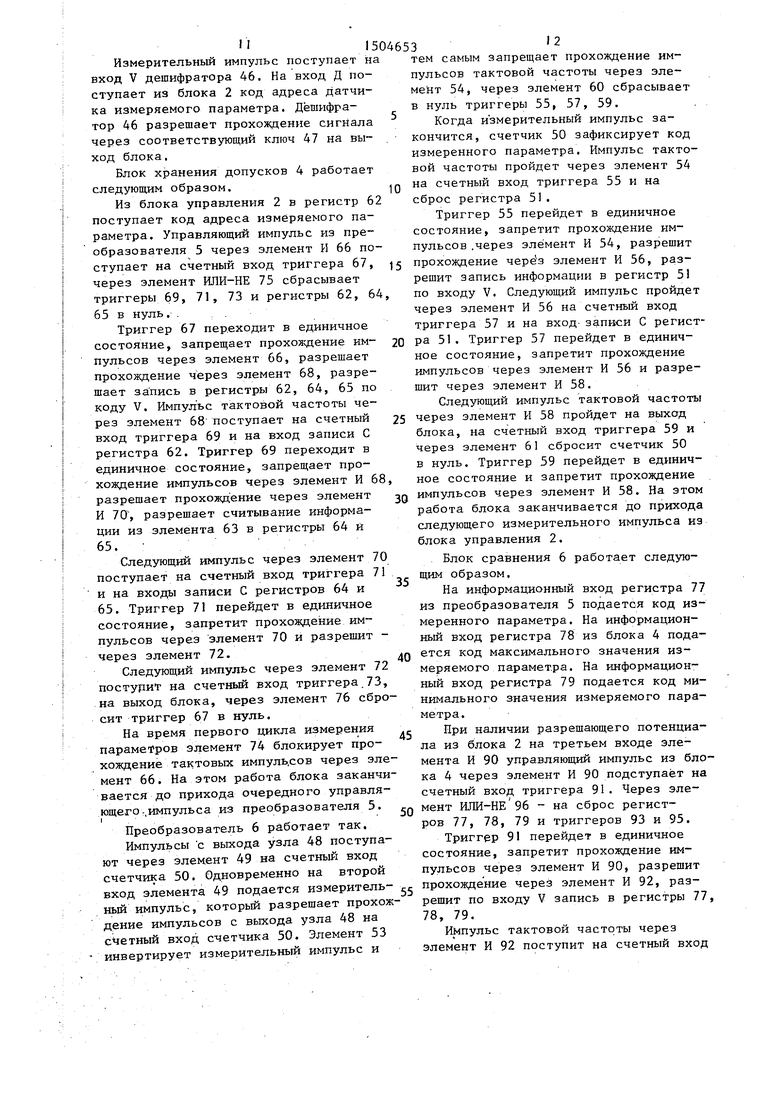

Блок 2 управления (фиг. 2) содержит генератор 15 тактовых- импульсов, делитель частоты , элемент ИЛИ 17, первый элемент И 18, первый двухтактовый триггер 19, первый элемент И 20, второй двухтактовый триг- 35 второй элемент И 108, второй триггер 21, второй элемент И 22, третий гер 109, третий элемент И 110, тре- двухтактовый триггер 23, третий элемент И 24, четвертый двухтактовый

триггер 25, четвертый элемент И 26,

чик 119,дешифратор 120, третий регистр 121, восьмой элемент И 122,первый 123 и второй 124 элементы ИЛИ-НЕ,

тий триггер 111, четвертый элемент И 112, четвертый триггер 113, пятый элемент И 114, пятый триггер 115, пятый двухтактовый триггер 27, пятьш 40 шестой элемент И 116, шестой триг- элемент И 28, первый счетчик 29, пер- гер 117, седьмой элемент И 118, счет- вый дешифратор 30, второй счетчик 31, второй дешифратор 32, шестой 33, седьмой 34, и восьмой 35 элементы И, элемент И-НЕ 36, девятый элемент И 37,45 элементы И 125-129, с девятого по первый 38 и второй 39 элементы ИЛИ-НЕ, тринадцатый, третий элемент ИЛИ-НЕ 130, десятый элемент И 40, шестой двух- четырнадцатый элемент И 131, четвер- тактовый триггер 41, RS-триггер 42, тый элемент ИЛИ-НЕ 132, четырнадца- второй 43 и третий 44 элементы ИЛИ-НЕ, тый элемент И 133, пятый элемент тумблер 45.50 134, пятнадцатый элемент И 135,

Коммутатор 3 (фиг. 3) содержит дешифратор 46 и ключи 47.j-47|.

Преобразователь 5 (Фиг. 4) включает узел-преобразователь аналог - код 48, первый элемент И 49, счетчик 50, регистр 51, первый элемент ИЛИ 52, первый элемент ИЛИ-НЕ 53, ; второй элемент И 54, первый триггер 55, третий элемент И 56, второй

шестой 136, седьмой 137 и восьмой 138 элементы ШШ-НЕ, шестнадцатый 139, семнадцатый 140 и восемнадцатый 141 элементы И, второй элемент ИЛИ 142 55 и сумматор 143.

Блок 8 хранения эталонных признаков производных (фиг. 8) содержит элемент 144 памяти, элемент ИЛИ 145, первый элемент И 146, первый триггер 147,

элемент И 70, третий триггер 71, четвертый элемент И 72, четвертый триггер 73, первый 74, второй 75 и третий 76 элементы ИЛИ-НЕ.

Блок 6 сравнения (фиг. 6) включает регистр 77, 78 и 79 с первого по третий, первый 80 и второй 81 сумматоры, первый инвертор 82, первый элемент И 83, первый элемент ИЛИ 84, второй инвертор 85, второй элемент И 86, второй элемент ИЛИ 87, третий

элемент И 88, первый триггер 89, четвертый элемент И 90, второй триггер 91, пятый элемент И 92, третий

0

вертый триггер 95, первый 96 и второй 97 элементы ИЛИ-НЕ, третий элемент ИЛИ 100 и четвертые инверторы 1 О 1 .. .

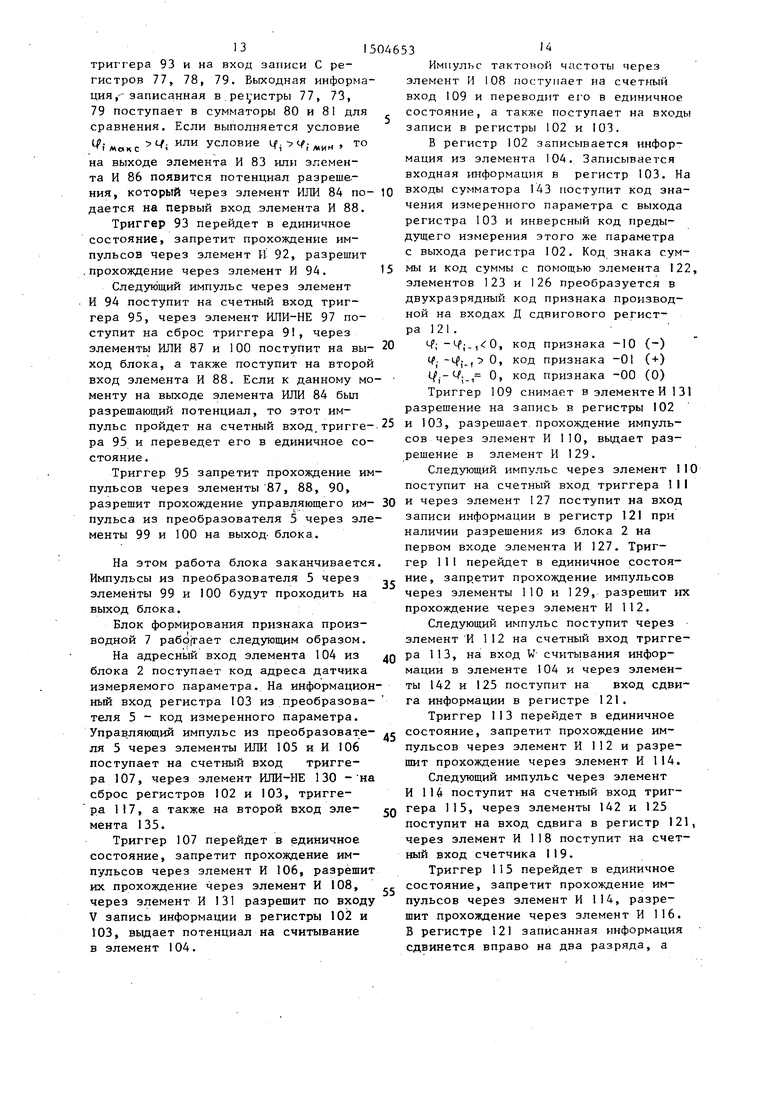

Блок 7 формирования признака производной (Фиг. 7) содержит первый 102 и второй 103 регистры, элемент 104 памяти, первый элемент ИЛИ 105, пер- вьш элемент И 106, первый триггер 107,

чик 119,дешифратор 120, третий регистр 121, восьмой элемент И 122,первый 123 и второй 124 элементы ИЛИ-НЕ,

тий триггер 111, четвертый элемент И 112, четвертый триггер 113, пятый элемент И 114, пятый триггер 115, шестой элемент И 116, шестой триг- гер 117, седьмой элемент И 118, счет- элементы И 125-129, с девятого по тринадцатый, третий элемент ИЛИ-НЕ 130 четырнадцатый элемент И 131, четвер- тый элемент ИЛИ-НЕ 132, четырнадца- тый элемент И 133, пятый элемент 134, пятнадцатый элемент И 135,

тий триггер 111, четвертый элемент И 112, четвертый триггер 113, пятый элемент И 114, пятый триггер 115, шестой элемент И 116, шестой триг- гер 117, седьмой элемент И 118, счет- элементы И 125-129, с девятого по тринадцатый, третий элемент ИЛИ-НЕ 130, четырнадцатый элемент И 131, четвер- тый элемент ИЛИ-НЕ 132, четырнадца- тый элемент И 133, пятый элемент 134, пятнадцатый элемент И 135,

шестой 136, седьмой 137 и восьмой 138 элементы ШШ-НЕ, шестнадцатый 139, семнадцатый 140 и восемнадцатый 141 элементы И, второй элемент ИЛИ 142 и сумматор 143.

Блок 8 хранения эталонных признаков производных (фиг. 8) содержит элемент 144 памяти, элемент ИЛИ 145, первый элемент И 146, первый триггер 147,

15046

второй элемент И J48, второй триггер 149, третий элемент И 150, третий триггер 151, счетчик 152, дешифратор 153, четвертый элемент И. 154, первый 155, второй 156 и третий 157 эле- менты ИЛИ-НЕ, регистр 158.

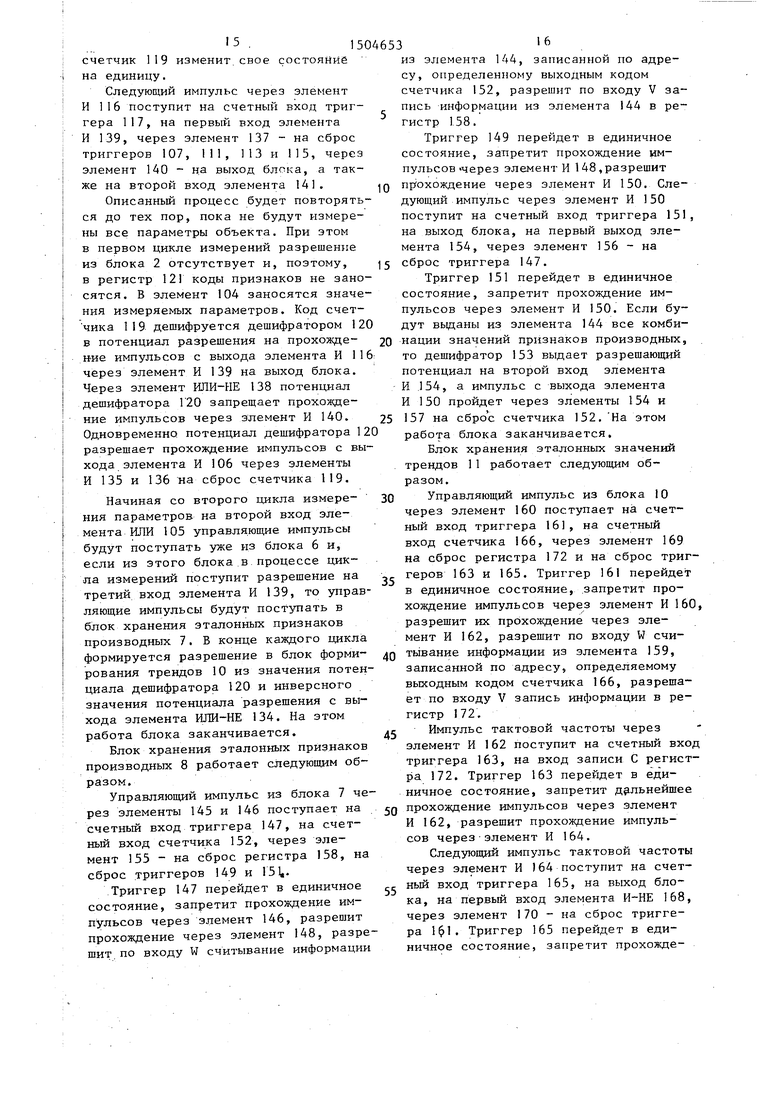

Блок 11 хранения эталонных эначе- ний трендов (фиг. 9) содержит элемент 159 памяти, первый элемент И 160,Q первый триггер 161, второй элемент И 162, второй триггер 163, третий элемент И 164, третий триггер 165, счетчик 16, дешифратор 167, элемент И- НЕ 168,и элементы ИЛИ-НЕ 169, 170, 171 с первого по- третий и регистр 172

Блок 9,сравнения приэнаков производных (фиг. 10) содержит первый 173 и второй 174 регистры, группу из п сумматоров 175, п первых элементов И 176, второй 177 и третий 178 элементы И, первый триггер 179, четвертый элемент И 180, второй .триггер 181, пятый элемент И 182, третий триггер 183,

15

20

первый элемент ИЛИ-НЕ 184, первый 185 25 Р° триггер 272, четвертый элемент

и второй 186 элементы ИЛИ, шестой 187 элементы И, четвертый 188 триггер, седьмой 189 и восьмой 190 элементы И, второй 191, третий 192, четвертый 193 и пятый 194 элементы ИЛИ-НЕ.

Блок 10 формирования трендов (фиг .11) содержит группу иэ п первых элементов ИЛИ-НЕ 195, сумматор 196, элемент 197 памяти, регистр 198, первый 199, второй 200, третий 201 и четвертый 202 элементы И, первый триггер 203, пятый элемент И 204, второй триггер 205, шестой элемент И 206, третий триггер 207, седьмой элемент И 208, счетчик 209,дешифратор 210, восьмой элемент 211 И, четвертый триггер 212, девятый элемент 213 И, пятый триггер 214, десятый элемент 215 И, шестой триггер 216 одиннадцатый элемент И 217, двенадцатый элемент И 218, второй 219, третий 220 и четвертый 221 элементы ИШ-НЕ, тринадцатый элемент И 222.

Блок 12 сравнения трендов (фиг.12) содержит: сумматор 223, первый 224 и второй 225 элементы И, первый элемент 226 ИЛИ-НЕ, третий 227 и четвертый 228 элементы И, первый триггер 229, пятый элемент И 230, второй триггер 231, шестой 232 элемент И, третий триггер 233, счетчик 234,дешифратор 235, второй элемент ИЛИ- НЕ 236, седьмой элемент И 237, первый элемент ИЛИ 238,третий 239 и четвер

ий ере-

тый 240 элементы ИЛИ-НЕ, второй элемент ИЛИ 241 и группу иэ п пятых элементов ИЛИ-НЕ 242,-242„.

1 п

Блок 13 хранения измерений первого цикла (фиг. 13) включает регистр 243, первый элемент ИЛИ-НЕ 244, первый 245 и второй 246 элементы И, первый триггер 247, третий элемент И 248, второй триггер 249, четвертый элемент И 250, третий триггер 251, пятый элемент И 252, четвертый триггер 253, шестой элемент И 254, счетчик 255, дешифратор 256, седьмой элемент И 257, пятый триггер 258, восьмой элемент И 259, второй 260 и третий 261 элементы ИЛИ-НЕ, девятый 262 и десятый 263 элементы И, четвертый 264 и пятый 265 элементы ИЛИ-НЕ и элемент 266 памяти.

Блок 14 индикации включает (фиг .14) первый регистр 267, первый элемент И 268, первый триггер 269, второй 270 и третий 271 элементы И, вто0

5

0

5

0

5

И 273, третий триггер 274, элемент ИЛИ-НЕ 275, первый дешифратор 276, первый 277, второй 278 индикаторы и

второй дешифратор 279. I

Входы и выходы 280-310 блоков устройства.

Устройство работает следующим образом.

По команде ПУСК (тумблер 45 на фиг. 2) блок 2 выдает в коммутатор 3, в блоки 4 и 7 код адреса датчика измеряемого сигнала. Затем в коммутатор 3 и в преобразователь 5 из блока 2 поступает измерительный импульс.

По этому импульсу коммутатор 3 в соответствии с кодом адреса подключает датчик измеряемого сигнала 1 ко входу преобразователя 5. Этот же импульс разрешает преобразование измеряемого сигнала в код. Преобразователь 5 выдает код измеренного сигнала в блок 6, 7 и 13. После выдачи кода управляющий импульс из преобразователя 5 подается одновременно в блоки 4, 6, 7 и 13. Этот импульс записывает в элементы 104 и 266 код измеренного сигнала. В остальных блоках ввиду отсутствия потенциала разрешения иэ блока 2, этот импульс никаких изменений не производит.

Управляющий импульс с выхода блока 7 поступает в блок 2, который вновь выдает код адреса очередного измеря- .емого сигнала, а эатем и измеритель 1504653

ный импульс. Описанный процесс будет повторяться до тех пор, пока не будут измерены все сигналы от датчиков 1.

В результате в элементы памяти ука- ,занных блоков будут записаны коды всех измеренных сигналов, а блок 13 перейдет в режим считывания информации по текущим адресам. Одновременно блок 2

выдает управляющий потенциал, который Q пит не в блок формирования трендов 10,

15

20

переводит блок 7 в режим формирования производных при следующем цикле измерений параметров. Этот же потенциал разрешает прохождение управляющих импульсов в блок 6 из блока 4. I

В следующем цикле измерений па-

раметров управляющий импульс с выхода преобразователя 5 поступит в блоки 4 и 13. Блок 4 выдает в блок 6 коды максимального и минимального значения измеряемого параметра, а также управляющий импульс. Одновременно блок 13 выдает в блок 10 код значения параметра, измеренного в первом цикле, и управляющий импульс.

В блоке 6 производится сравнение текущего значения измеряемого параметра с его допускаемыми пределами. В то же время в блоке 10 производится формирование тренда текущего измеряемого параметра и занесение его в элемент 197.

Если значение измеренного сигнала находится в пределах допусков, т.е.

,л.«кc - „им ТО блок 6 вьщает управ- з ляющий импульс в блок 7, где формируется знак производной измеренного параметра, который заносится в элемент 104,. а управляющий импульс подается в блок 2.

Описанный процесс повторяется для следующего измеряемого параметра, и так далее, пока не будут измерены все параметры. Тогда управляющий импульс поступит не в блок управ- в блок формирования трен30

из блока 7 ления 2, а дов 10. Блок 10

выдает код тренда первого измеренного параметра в блок 12 и управляющий импульс в блок 11.

Блок 11 вьщает код эталонного значения тренда измеренного параметра и управляющий импульс в блок 12.

Если коды текущего к эталонного тренда не совпадают, то управляющий импульс из блока 1 2 поступит в ( 1 блок 10. Блок формирования трендов 10 вновь вьщает код тренда следующего измеренного параметра в блок 12, а упа в блок управления 2.

Блок 2 вьщает команду на -следующий цикл измерения параметров, а блок 14 индуцирует сообщение Тренд не обнаружен. Но если в блоуе 12 произойдет совпадение трендов, то управляющий импульс из блока 12 поступит в блок 14, который вьщает команду стоп в блок 2. Процесс измерения параметров прекратится, а блок 14 индуцирует название неисправности.

Если же в процессе измерения параметров в блоке 6 будет установлено, что измеренный параметр вьшел за до- 25 пустимые пределы, то вырабатывается команда наличия неисправности в виде потенциала, который подается в блок 10 и запрещает прохождение управляющих импульсов в этом блоке. Кроме того, данный потенциал прекращает дальнейшую работу .блока 6, раз- рещает свободный проход управляющих импульсов с выхода преобразователя 5 через блок 6 на вход блока 7.

Когда признаки производных всех измеряемых параметров будут сформированы как описывалось, тогда коды этих признаков будуТ выданы в блок 9, а управляющий импульс - в блок 8.

Блок хранения эталонных признаков производных 8 выдает в блок сравнения признаков производных 9 коды эталонных признаков производных, соответствующих одному из возможных состояний объекта контроля (классу неисправности) .

В блоке 9 производится сравнение . поступивших кодов, Если совпадение произощло, то данный блок вьщает управляющий импульс в блок 14, который как уже бьшо описано в случае наличия тренда, вызовет останов устройства и индуцирует вид неисправности, Но, если совпадение отсутствует, то блок 9 вьщает управляющий импульс в блок 8, который вновь вьщает в блок 9 следующую комбинацию кодов эталонных призг1аков производных, соответствующих другому состоянию объекта. И так

40

45

50

55

8

равляющии импульс - в блок хранений эталонных значений трендов .11. Описанный процесс повторится. Когда все, тренды, хранящиеся в элементе 197, будут сравнены с соответствующими эталонными значениями Трендов, и ни одного совпадения не произойдет, управляющий импульс из блока 12 посту Q пит не в блок формирования трендов 10,

5

0

з 0

а в блок управления 2.

Блок 2 вьщает команду на -следующий цикл измерения параметров, а блок 14 индуцирует сообщение Тренд не обнаружен. Но если в блоуе 12 произойдет совпадение трендов, то управляющий импульс из блока 12 поступит в блок 14, который вьщает команду стоп в блок 2. Процесс измерения параметров прекратится, а блок 14 индуцирует название неисправности.

Если же в процессе измерения параметров в блоке 6 будет установлено, что измеренный параметр вьшел за до- 5 пустимые пределы, то вырабатывается команда наличия неисправности в виде потенциала, который подается в блок 10 и запрещает прохождение управляющих импульсов в этом блоке. Кроме того, данный потенциал прекращает дальнейшую работу .блока 6, раз- рещает свободный проход управляющих импульсов с выхода преобразователя 5 через блок 6 на вход блока 7.

Когда признаки производных всех измеряемых параметров будут сформированы как описывалось, тогда коды этих признаков будуТ выданы в блок 9, а управляющий импульс - в блок 8.

Блок хранения эталонных признаков производных 8 выдает в блок сравнения признаков производных 9 коды эталонных признаков производных, соответствующих одному из возможных состояний объекта контроля (классу неисправности) .

В блоке 9 производится сравнение . поступивших кодов, Если совпадение произощло, то данный блок вьщает управляющий импульс в блок 14, который как уже бьшо описано в случае наличия тренда, вызовет останов устройства и индуцирует вид неисправности, Но, если совпадение отсутствует, то блок 9 вьщает управляющий импульс в блок 8, который вновь вьщает в блок 9 следующую комбинацию кодов эталонных призг1аков производных, соответствующих другому состоянию объекта. И так

0

5

0

5

91504653

пока не будет обнаружено кодовМ1ризнаков, после чего останов устройства и индиравности.

ты сч ег за ре эл ме ме эл сч чи ще пу

Блок 2 управления работает следующим образом.

Выходная частота задающего генера- гора 15 с помощью делителей 16 понижается до значения тактовой частоты. Импульсы тактовой частоты поступают на первые входы элементов 18, 20, 22, 24, 26, 28 и на третий вход элемента 35.

При включении тумблера 45 (команда ПУСК) триггер 42 переходит в нулевое состояниеi Через элемент 43 снимается нулевой потенциал со второго входа элемента И 18 и с установочных вхо- дов триггеров 19, 21, 23, 25, 27, делителей 16, через элемент 38 - с установочного входа счетчика 31. Через элемент 39 снимается нулевой потенциал (сброс общий) со всех блоков уст- ройства.

Первый после включения тумблера 45 тактовый импульс пройдет через элемент И 18 на счетный вход триггера 19 Триггер 19 перейдет в единичное со- стояние и запретит прохождение тактовых импульсов через элемент И 18, разрешит прохождение через элемент 20. Следующий тактовый импульс пройдет через элемент И 20 на счетный вход триггера 21. Триггер 21 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 20, разрешит - через элемент И 22.

Следующий импульс тактовой частоты пройдет через элемент И 22 на счетный вход триггера 23 и счетный вход счетчика 31, служащего для генерации адреса датчика измеряемого параметра.

Триггер 23 перейдет в единичное со- I -.

стояние, запретит прохождение импульсов через элемент И 22 и разрешит через элемент И 24.

Счетчик 31 изменит свое состояние на единицу. Следующий импульс тактовой частоты пройдет через элемент И 24 на счетный вход триггера 25 и переведет его в единичное состояние. Триггер 25 запретит прохождение импульсов через элемент И 24 и разрешит - через элемент И 26. Через элементы И 33 осуществится вывод кода адреса датчика измеряемого параметра с выхода счетчика 31.

10

0

5

0 5

Q

5

0

5

0

5

Следующий импульс тактовой частоты пройдет через элемент И 26 на счетный вход триггера 27 и переведет его в еди {ичное состояние. Триггер 27 запретит прохождение и tпyльcoв через элемент И 26 и разрешит через элемент И 28; разрешит генерацию измерительного импульса на выходе элемента И 34. Следующий импульс через элемент И 28 поступит на счетный вход счетчика 29, служащего для подсчета числа тактовых импульсов, определяющего длительность измерительного импульса.

Как только число тактовых импульсов, прошедших через счетчик 29, станет равным заданному, дешифратор 30 запретит дальнейшее прохождение импульсов тактовой частоты через элемент И 28, прекратит генерацию измерительного импульса на выходе элемента И 34 и через элемент И 36 разрешит прохождение импульсов тактовой частоты на выход блока через элемент И 35.

В этом состоянии блок будет находиться до тех пор, пока на один из входов элемента ИШ1 17 не поступит управляющий импульс. Этот импульс пройдет через элемент ИЛИ 17, через элемент ИЛИ-НЕ 43, сбросит в нуль триггеры 21, 23, 25, 27 и счетчик 29. Триггер 21 вновь разрешит прохождение тактовых импульсов через элемент 20. Описанный процесс повторится до тех пор, пока значение счетчика 31 не станет равным числу измеренных параметров . Тогда дешифратор 32 разрешит прохождение импульса сброса с выхода элемента 20 через элемент И 37 и элемент .И 40 на счетный вход триггера 41, через элемент ИЛИ-НЕ 38 на сброс счет- чика 31. Триггер 41 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 40 и выдаст на выход блока разрешающий потенциал для проведения контроля и диагностики. Блок будет готов для еле- следующего цикла измерения параметров однако, если через элемент ИЛИ- НЕ 44 поступит потенциал команды стоп, то инверсия этого сигнала запретит прохождение измерительного и тактовых импульсов через элементы 34 и 35. Устройство будет оста- ;новлено.

Коммутатор 3 работает следующим образом.

и

Измерительный импульс поступает на вход V дешифратора 46, На вход Д поступает из блока 2 код адреса датчика измеряемого параметра. Дешифратор 46 разрешает прохождение сигнала через соответствующий ключ 47 на выход блока,

Блок хранения допусков 4 работает следующим образом.

Из блока управления 2 в регистр 62 поступает код адреса измеряемого параметра. Управляющий импульс из преобразователя 5 через элемент И 66 поступает на счетный вход триггера 67, через элемент РШИ-НЕ 75 сбрасывает триггеры 69, 71, 73 и регистры 62, 64, 65 в нуль. . .

Триггер 67 пер.еходит в единичное состояние, запрещает прохождение импульсов через элемент 66, разрешает прохождение через элемент 68, разрешает запись в регистры 62, 64, 65 по коду V. Импульс тактовой частоты через элемент 68 поступает на счетный вход триггера 69 и на вход записи С регистра 62. Триггер 69 переходит в единичное состояние, запрещает прохождение импульсов через элемент И 68, разрешает прохозкд ение через элемент И 70, разрешает считывание информации из элемента 63 в регистры 64 и 65.

Следующий импульс через элемент 70 поступает на счетный вход триггера 71 и на входы записи С регистров 64 и 65. Триггер 71 перейдет в единичное состояние, запретит прохождение импульсов через элемент 70 и разрешит - через элемент 72.

Следующий импульс через элемент 72 постурит на счетный вход триггера,73, на выход блока, через элемент 76 сбросит триггер 67 в нуль.

На время первого цикла измерения параметров элемент 74 блокирует прохождение тактовых импуль.сов через элемент 66. На этом работа блока заканчивается до прихода очередного управляющего -.импульса из преобразователя 3. 1

Преобразователь 6 работает так.

Импульсы с выхода узла 48 поступают через элемент 49 на счетный вход счетчика 50. Одновременно на второй

10

20

25

тем самым запрещает прохождение импульсов тактовой частоты через элемент 54, через элемент 60 сбрасывает в нуль триггеры 55, 57, 59.

Когда измерительный импульс закончится, счетчик 50 зафиксирует код измеренного параметра. Импульс тактовой частоты пройдет через элемент 54 на счетный вход триггера 55 и на сброс регистра 5.

Триггер 55 перейдет в единичное состояние, запретит прохождение импульсов .через элемент И 54, разрешит |5 прохождение через элемент И 56, разрешит запись информации в регистр 51 по входу V. Следующий импульс пройдет через элемент И 56 на счетный вход триггера 57 и на вход- записи С регистра 51, Триггер 57 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 56 и разрешит через элемент И 58.

Следующий импульс тактовой частоты через элемент И 58 пройдет на выход блока, на счетный вход триггера 59 и через элемент 61 сбросит счетчик 50 в нуль. Триггер 59 перейдет в единичное состояние и запретит прохождение импульсов через элемент И 58. На этом работа блока заканчивается до прихода следующего измерительного импульса из блока управления 2.

Блок сравнения 6 работает следующим образом.

На информационный вход регистра 77 из преобразователя 5 подается код измеренного параметра. На информационный вход регистра 78 из блока 4 подается код максимального значения измеряемого параметра. На информационный вход регистра 79 подается код минимального значения измеряемого параметра ,

При наличии разрешающего потенциала из блока 2 на третьем входе элемента И 90 управляющий импульс из блока 4 через элемент И 90 подступает на счетный вход триггера 91. Через эле- 50 мент ИЛИ-НЕ 96 - на сброс регистров 77, 78, 79 и триггеров 93 и 95.

Триггер 91 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 90, разрешит

30

35

40

45

вход элемента 49 подается измеритель- 5 прохождение через элемент И 92, разный импульс, который разрешает прохож- решит по входу V запись в регистры 77, дение импульсов с выхода узла 48 на 78, 79.

с 1етный вход счетчика 50. Элемент 53 Импульс тактовой частоты через инвертирует измерительный импульс и элемент И 92 поступит на счетный вход

1504653

12

0

5

тем самым запрещает прохождение импульсов тактовой частоты через элемент 54, через элемент 60 сбрасывает в нуль триггеры 55, 57, 59.

Когда измерительный импульс закончится, счетчик 50 зафиксирует код измеренного параметра. Импульс тактовой частоты пройдет через элемент 54 на счетный вход триггера 55 и на сброс регистра 5.

Триггер 55 перейдет в единичное состояние, запретит прохождение импульсов .через элемент И 54, разрешит прохождение через элемент И 56, разрешит запись информации в регистр 51 по входу V. Следующий импульс пройдет через элемент И 56 на счетный вход триггера 57 и на вход- записи С регистра 51, Триггер 57 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 56 и разрешит через элемент И 58.

Следующий импульс тактовой частоты через элемент И 58 пройдет на выход блока, на счетный вход триггера 59 и через элемент 61 сбросит счетчик 50 в нуль. Триггер 59 перейдет в единичное состояние и запретит прохождение импульсов через элемент И 58. На этом работа блока заканчивается до прихода следующего измерительного импульса из блока управления 2.

Блок сравнения 6 работает следующим образом.

На информационный вход регистра 77 из преобразователя 5 подается код измеренного параметра. На информационный вход регистра 78 из блока 4 подается код максимального значения измеряемого параметра. На информационный вход регистра 79 подается код минимального значения измеряемого параметра ,

При наличии разрешающего потенциала из блока 2 на третьем входе элемента И 90 управляющий импульс из блока 4 через элемент И 90 подступает на счетный вход триггера 91. Через эле- 0 мент ИЛИ-НЕ 96 - на сброс регистров 77, 78, 79 и триггеров 93 и 95.

Триггер 91 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 90, разрешит

0

5

0

5

триггера 93 и на вход записи С регистров 77, 78, 79. Выходная информация,-- записанная в.ре1, истры 77, 73, 79 поступает в сумматоры 80 и 81 для сравнения. Если выполняется условие ..мс.«с условие , , то на выходе элемента И 83 или элемента И 86 появится потенциал разрешения, который через элемент ИЛИ 84 по- дается на первый вход элемента И 88.

Триггер 93 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 92, разрешит .прохождение через элемент И 94.

Следующий импульс через элемент И 94 поступит на счетный вход триггера 95, через элемент ИЛИ-НЕ 97 поступит на сброс триггера 91, через элементы ИЛИ 87 и 100 поступит на вы- ход блока, а также поступит на второй вход элемента И 88. Если к данному мо менту на выходе элемента ИЛИ 84 бьт разрешающий потенциал, то этот импульс пройдет на счетный вход тригге- ра 95 и переведет его в единичное состояние.

Триггер 95 запретит прохождение импульсов через элементы 87, 88, 90, разрешит прохождение управляющего им- пульса из преобразователя 5 через элементы 99 и 100 на выход, блока.

На этом работа блока заканчивается Импульсы из преобразователя 5 через элементы 99 и 100 будут проходить на выход блока.

Блок формирования признака производной 7 следующим образом.

На адресный вход элемента 104 из блока 2 поступает код адреса датчика измеряемого параметра. На информационный вход регистра 103 из преобразователя 5 - код измеренного параметра. Управляющий импульс из преобразовате- ля 5 через элементы ИЛИ 105 и И 106 поступает на счетный вход триггера J07, через элемент ИЛИ-НЕ 130 - на сброс регистров 102 и 103, триггера 117, а также на второй вход эле- мента 135.

Триггер 107 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 106, разрешит их прохождение через элемент И 108, через элемент И 131 разрешит по входу V запись информации в регистры 102 и 103, выдает потенциал на считывание в элемент 104.

Импульс тактовой частоты через элемент И 108 поступает на счетный вход 109 и переводит его в единичное состояние, а также поступает на входы записи в регистры 102 и 103.

В регистр 102 записывается информация из элемента 104. Записывается входная информация в регистр 103. На входы сумматора 143 поступит код значения измеренного параметра с выхода регистра 103 и инверсный код предыдущего измерения этого же параметра с выхода регистра 102. Код знака суммы и код суммы с помощью элемента 122 элементов 123 и 126 преобразуется в двухразрядный код признака производной на входах Д сдвигового регистра 1 2 1 .

W; -Ч ;-1 0, код признака -10 (-)

tf; - Ц.., : О, код признака -01 (+)

Ч |-- ;-1 О °f признака -00 (0)

Триггер 109 снимает в элементе И 13 разрешение на запись в регистры 102 и 103, разрешает прохождение импульсов через элемент И 110, выдает разрешение в элемент И 129.

Следующий импульс через элемент П поступит на счетный вход триггера 1II и через элемент 127 поступит на вход записи информации в регистр 121 при наличии разрешения из блока 2 на первом входе элемента И 127. Триггер 111 перейдет в единичное состояние, запретит прохождение импульсов через элементы ПО и 129, разрешит FfX прохождение через элемент И 112.

Следующий импульс поступит через элемент И 112 на счетный вход триггера 113, на вход W считывания информации в элементе 104 и через элементы 142 и 125 поступит на вход сдвига информации в регистре 121.

Триггер ПЗ перейдет в единичное состояние, запретит прохождение импульсов через элемент И 112 и разрешит прохождение через элемент И 114.

Следующий импульс через элемент И 114 поступит на счетный вход три1- гера 115, через элементы 142 и 125 поступит на вход сдвига в регистр 121 через элемент И 118 поступит на счетный вход счетчика 119.

Триггер 115 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 114, разрешит прохождение через элемент И 116. В регистре 121 записанная информация сдвинется вправо на два разряда, а

счетчик 119 изменит,свое состояние на единицу.

Следующий импульс через элемент И 116 поступит на счетный вход триггера 117, на первый вход элемента И 139, через элемент 137 - на сброс триггеров 107, 111, 113 и 115, через элемент 140 - на выход блока, а также на второй вход элемента 141.

Описанный процесс будет повторяться до тех пор, пока не будут измерены все параметры объекта. При этом в первом цикле измерений разрешение из блока 2 отсутствует и, поэтому, в регистр 121 коды признаков не заносятся. В элемент 104 заносятся значения измеряемых параметров. Код счет- чика 119 дешифруется дешифратором 12 в потенциал разрешения на прохождение импульсов с выхода элемента И 11 через элемент И 139 на выход блока. Через элемент ИЛИ-НЕ 138 потенциал дешифратора Г20 запрещает прохождение импульсов через элемент И 140. Одновременно потенциал дешифратора 12 разрешает прохождение импульсов с выхода элемента И 106 через элементы И 135 и 136 на сброс счетчика 119.

Начиная со второго цикла измере- ния параметров на второй вход элемента ИЛИ 105 управляющие импульсы будут поступать уже из блока 6 и, если из этого блока в процессе цикла измерений поступит разрешение на третий вход элемента И 139, то управляющие импульсы будут поступать в блок хранения эталонных признаков производных 7. В конце каждого цикла формируется разрешение в блок формирования трендов 10 из значения потенциала дешифратора 120 и инверсного значения потенциала разрешения с выхода элемента ИЛИ-НЕ 134. На этом работа блока заканчивается.

Блок хранения эталонных признаков производных 8 работает следующим образом.

Управляющий импульс из блока 7 через элементы 145 и 146 поступает на счетный вход триггера 147, на счетный вход счетчика 152, через элемент 155 - на сброс регистра 158, на сброс триггеров 149 и 151,.

Триггер 147 перейдет в единичное состояние, запретит прохождение импульсов через элемент 146, разрешит прохождение через элемент 148, разрешит по входу W считывание информации

0

5

0 5

0

5

0

из элемента 144, записанной по адресу, определенному выходным кодом счетчика 152, разрешит по входу V запись информации из элемента 144 в регистр 158.

Триггер 149 перейдет в единичное состояние, запретит прохождение импульсов -через элемент И 148,разрешит прохождение через элемент И 150. Следующий импульс через элемент И 150 поступит на счетный вход триггера 151, на выход блока, на первый выход элемента 154, через элемент 156 - на сброс триггера 147.

Триггер 151 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 150. Если будут выданы из элемента 144 все комбинации значений признаков производных, то дешифратор 153 выдает разрешающий потенциал на второй вход элемента И 154, а импульс с выхода элемента И 150 пройдет через элементы 154 и 157 на сброс счетчика 152. На этом работа блока заканчивается.

Блок хранения эталонных значений трендов 11 работает следующим образом.

Управляющий импульс из блока 10 через элемент 160 поступает на счетный вход триггера 161, на счетный вход счетчика 166, через элемент 169 на сброс регистра 172 и на сброс триггеров 163 и 165. Триггер 161 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 160, разрешит их прохождение через элемент И 162, разрешит по входу W считывание информации из элемента 159, записанной по адресу, определяемому выходным кодом счетчика 166, разрешает по входу V запись информации в регистр 172,

Импульс тактовой частоты через элемент И 162 поступит на счетный вход триггера 163, на вход записи С регистра 172. Триггер 163 перейдет в единичное состояние, запретит дальнейшее прохождение импульсов через элемент И 162, разрешит прохождение импульсов черезэлемент И 164.

Следующий импульс тактовой частоты ч:ерез элемент И 164 поступит на счет- ньй вход триггера 165, на выход блока, на первый вход элемента И-НЕ 168, через элемент I70 - на сброс триггера . Триггер 165 перейдет в единичное состояние, запретит прохожде 150

ние импульсов через элемент И 164. Если будут выданы из элемента 159 все эталонные значения трендов, то дешифратор 167 выдает разрешение на второй вход элемента 168, и импульс выхода элемента 164 пройдет через элмент И-НЕ 168, через элемент 171 на сброс счетчика 166. На этом работа блока заканчивается.

Блок сравнения признаков производных 9 работает следующим образом.

Коды эталонных признаков производных поступают на информационный вход регистра 173 из блока хранения эта- лонных признаков производных 8. Коды признаков производных текущего цикла измерений поступают на информационный вход регистра 174 из блока формирования признаков производных 7.

Управляющий импульс из блока 8 через элемент 177 поступает на счетный вход триггера 179, через элемент 194 на сброс регистра 183, через элемент 192 - на сброс регистра 174.

Триггер 179 перейдет в единичное состояние, запретит прохождение импульсов через элемент 178, разрешит прохождение их через элемент 180, разрешит по входу V запись информации в регистр 174.

Импульс тактовой частоты через элемент 180 поступает на счетный вход триггера 181, на вход С записи регистра 174 через элемент 189, на вход С записи регистра 173.

В регистры 173 и 174 запишется информация из п двукразрядных сумматоров 175. Триггер 181 перейдет в единичное состояние, запретит прохожде- ние импульсов через элемент 180, разрешит их прохождение через эле- v мент 182.

Следующий импульс через элемент 18 поступит на счетный вход триггера 183 через элемент 187 - на счетный вход триггера 188, на первые входы элементов 185 и 186.

Если к данному моменту будет иметь место совпадение кодов признаков про- изводных, то на выходе элемента 177 появится разрешающий .потенциал, который позволит импульсу с выхода элемента 182 пройти через элемент 186 на выход блока (в блок индикации 14).

Если совпадение отсутствует, то этот импульс пройдет на вход блока через элемент 185 (в блок 8 хранения эталонных признаков производных).

Q

5 0

5

о

.,.

5

5

Триггер 188 перейдет в еди(гичпое состояние, заггретит 1рохождени(е нм- пульсов через элементы 189 и 190. Триггер 183 перейдет в единичное состояние, запретит прохождение импульсов через элемент 182.

На этом работа блока заканчивается до прихода следующего управляквдего импульса.

Блок формирования трендов 10 работает следующим образом.

На первый вход сумматора 196 через элементы 195 из преобразователя 5 подается код измеренного параметра, на второй вход сумматора 196 из блока 13 подается код этого же параметре,, измеренного в первом цикла.

Управляющий импульс через элементы 201 и 202 подается на счетный вход триггера203, на счетный вход счетчика 209 и через элемент 220 - на сброс регистра 198, триггеров 205 и 207.

Триггер 207 перейдет в единичное состояние, запретит прохождение импульсов через элемент 202, разрешит прохождение импульсов через элемент И 204, выдаст разрешение в элемент 199. Следующий импульс через элемент И 204 поступит на счетный вход триггера 205, через элемент 199 по входу V запишет информацию с вь1хода сумматора 196 в элемент 197 по адресу, определенному выходным кодом счетчика 209, поступит на второй вход элемента 222.

Триггер 205 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 206,

Следующий импульс тактовой частоты через элемент 206 поступит на счетный вход триггера 207, через элемент 219 - на сброс триггера 203, на первый вход элемента И 218. Триггер 207 перейдет в единичное состояние; запретит прохождение импульсов через элемент И 206 и выдаст разрешение на второй вход элемента 215. Описанный процесс повторится столько раз, сколько должно быть измерено параметров в цикле. Тогда дешифратор 210 дешифрирует выходной код счетчика 209 в разрешающий потенциал на первом входе элемента 211 и на втором входе элемента 217.

Следующий импульс через элемент 211 поступит на счетный вход триггера 212. Триггер 212 перейдет в единичное состояние, запретит проховдение импульсов через элементы 211 и 199, выдаст разрешение на первый вход элемен 19

та И 200, на первый вход элемента И 206, переведет элемент 197 в режим считывания.

Следующий импульс через элемент И 213 поступит на счетный вход триггера 214. Триггер 214 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 213, разрешит прохождение импульсов через элемент И 215, выдаст разрешение на третий вход элемента 217.

Следующий импульс через элемент И 215 поступит на счетный вход триггера 216 и через элемент И 208 - на сброс счетчика 209. После этого управляющие импульсы будут поступать из блока 12 на второй вход элемента 202, а выходные управляющие импул

сы - с выхода элемента 206 через эле- 20 или когда все эталонные значения трен- мент 218.дов не будут исчерпаны. Тогда выход- Когда счетчик 209 вновь отсчитает ной код счетчика 234 дешифрируется в сформированное количество трендов, де- разрешающий потенциал с помощью эле- шифратор 210 разрешит прохождение импульса с выхода элемента И 218 через элементы 217 и 221 на сброс триггеров 214, 216 и через элемент 208 - на сброс счетчика 209. На этом работа блока заканчивается,

мента ИЛИ-НЕ 236 на третьем входе эле- 25 мента И 237, и импульс с выхода элемента И 230 поступит через элемент 237 на выход блока.

Следующий импульс с выхода элемента И 232 через элементы ИЛИ 241 и 238

Блок сравнения трендов 12 работает зо сбросит счетчик 234 в нуль. На этом

следующим образом.

На первый вход сумматора 223 из блока хранения эталонных значений трендов 11 подается код эталонного тренда. Через элемент 242 на второй вход сумматора 223 из блока формирования трендов 10 подается код сформированного тренда.

Управляющий импульс из блока 11 через элемент И 228 поступает на счетный вход триггера 229 и счетчика 234, через элемент ИЛИ-НЕ 239 поступает на сброс триггеров 231 и 233 Триггер 229 перейдет в единичное состояние, запретит дальнейшее прохождение импульсов через элемент 228, разрешит их прохождение через элемент 230.

Импульс тактовой частоты через элемент 230 поступит на счетный вход триггера 231, на второй вход элемента И 225., на второй вход элемента И 227, на второй вход элемента 237. Если на выходе сумматора 223 как в знаковом разряде, так и во всех разрядах суммы будут равны, единице (т.е. коды трендов равны), то элемент И 224 выдаст разрешение на первый вход элемента И 225. Тогда им04653 .

пульс с выхода элемента 230 пройдет через элемент И 225 на выход блока. Б противном случае импульс с выхода элемента И 230 пройдет через элемент И 227 на другой выход блока.

Триггер 231 перейдет в единичное состояние, запретит прохождение импульсов через элемент И 230 и разре10 шит прохождение их через элемент И 232. Следующий импульс через элемент И 232 поступит на счетный вход триггера 233, через элемент ИЛИ-НЕ 24С поступит на сброс триггера 229, по15 ступит кроме того на второй вход элемента 241 .

Описанный процесс будет повторяться до тех пор, пока не произойдет совпадение кодов трендов в сумматоре 223

или когда все эталонные значения трен- дов не будут исчерпаны. Тогда выход- ной код счетчика 234 дешифрируется в разрешающий потенциал с помощью эле-

мента ИЛИ-НЕ 236 на третьем входе эле- мента И 237, и импульс с выхода элемента И 230 поступит через элемент 237 на выход блока.

Следующий импульс с выхода элемента И 232 через элементы ИЛИ 241 и 238

5

0

5

0

5

работа блока заканчивается.

Блок хранения измерений первого цикла 13 работает следующим образом.

Б элемент 266 из блока управления 2 поступает адрес измеряемого параметра, из преобразователя 5 - код измеренного по этому адресу параметра.

Управляющий импульс из преобразователя 5 через элемент 246 поступает на счетный вход триггера 247, на счет- ньш вход счетчика 255, через элемент 264 - на сброс регистра 243, через элемент 265 - на сброс триггера 253. Триггер 247 переходит в единичное состояние, запрещает прохождение импульсов через элемент 246, разрешает прохождение их через элемент 248.

Импульс тактовой частоты через элемент 248 поступит на счетный вход триггера 249 и через элемент 262 - на вход V записи входной информации в элемент 266. Триггер 249 перейдет в единичное состояние, запретит прохождение импульсов через элемент 248, разрешит их прохождение через элемент 250, вьщаст разрешение в элемент 245.

211504

Следующий импульс через элемент 250 поступит на счетный вход триггера 251, через элемент 263 - на вход С записи информации из элемента 266 в регистр 243. Запись указанной шфopмa- ции в регистр 243 будет производить

ся, начиная со второго цикла измерений параметров, т.е. когда триггер 258 перейдет в единичное состояние. ю

Триггер 251 перейдет в единичное состояние, запретит прохождение импульсов через элемент 250, разрешит прохождение их через элемент 252.

Следующий импульс через элемент 25215 индицироваться на втором индика20

25

30

поступает на счетн1з1й вход триггера 253, на первый вход элемента 254, через элемент 244 - на сброс триггеров 247, 249 и 251, поступает также на второй вход элементов 257 и 259.

Триггер 253 запрещает прохождение импульсов через элемент 252. Описанный процесс будет повторяться до тех пор, пока не будут измерены все параметры. Тогда выходной код счетчика 255 преобразуется дешифратором 256 в разрешающий потенциал на первых входах элементов 257 и 259.

Импульс с выхода элемента И 252 через элемент И 257 переведет триггер 258 в единичное состояние, который через элемент И 245 переведет элемент 266 в режим считывания информации, разрешит прохождение импульсов через элемент И 263, запретит прохож- ,г дение их через элементы 257 и 262, разрешит прохождение импульсов на выход блока через элемент 254. На этом работа блока заканчивается.

Блок индикации 14 работает следу- кнцим образом.

На информационный вход регистра 279 из блока хранения эталонных призна- I ков производных 8 подается комбинация кодов эталонных признаков производных, характеризующая неисправность объекта.

Если в результате сравнения из блока сравнения признаков производных 9 поступит управляющий импульс через элемент 268 на счетный вход тригге- ра 269, то он перейдет в единичное состояние, запретит прохождение импульсов через элемент 268, разрешит запись информации в регистр 279 по входу V, через элемент 270 вьщаст разрешение на первый вход элемента 276.

Импульс тактовой частоты через элемент 276 поступит на счетный вход

40

45

50

55

22

триггера

272, на вход записи С регистров 279 и 267.

Трипер 272 перейдет в единичное состояние и на выход блока выдаст запрещающий потенциал. Одновременно дешифратор 276 выдаст на первый индикатор 277 код неисправности, которьй индицируется в название неисправности.

Если же управляющий импульс появится из блока сравнений трендов 12, то описанный процесс повторится с той лишь разницей, что неисправность бу

5

0

г

0

5

0

5

торе 278. На этом работа блока закончена.

Формула изобретения

Устройство контроля и диагностики состояний технического объекта, содержащее датчики контролируемых параметров, блок управления, блок задания допусков, аналого-цифровой преобразователь, блок сравнения, блок формирования признака производной, блок хранения эталонных признаков производных,- блок сравнения признаков производных и блок индикации; подключенный первым управляющим и первым информационным входами соответственно к второму управляющему выходу блока сравнения и к информационному выходу блока хранения эталонных признаков производных, у которого первый, второй управляющие входы, управляющий и информационный выходы соединены соответственно с третьим управляющим выходом блока формирования признака производной, с первым управляющим выходом, с управлякхцим и с первым информационным выходами блока сравнения признаков производных, подсоединенного вторым информационным входом к информационному выходу блока формирования признака производной, у которого управлякмцие входы с первого по пятый , первый управляющий и инфopм aци- онньш входы связаны соответственно с вторым и с первым управляющим выходами блока сравнения, с третьим управляющим выходом блока управления, с управляющим выходом преобразователя, с вторым управляющим выходом блока управления и с третьим управляющим входом и с информационным выходом аналого-цифрового преобразователя, соединенным также с информационным входом блока сравнения, у которого установочный вход и управляющие входы с первого по третий связаны соответственно с информационным, с управляющим вьгходами, с третьим и с вторым уп равляющими входами блока задания допусков, два последние из которых подключены соответственно к третьему управляющему выходу блока управления и к управляющему выходу аналого-цифрового преобразователя, у которого информационный и управляющий входы соединены соответственно с информационным и первым управляющим входами коммутатора, информационные и управляющие входы которого связаны с одноименными выходами соответственно датчиков контролируемых параметров и блока управления, первым управляющим входом подсоединенного к командному вьпсоду блока индикации, первый, управляющий вход блока задания допусков соединен с вторым управляющим выходом блока управления, о.тличающе- е с я тем, что, с целью повышения быстродействия и надежности устройства, оно содержит блок хранения эталонных значений трендов и блок хранения измерений первого цикла, блок формирования трендов, блок сравнения трендов, у которого первый, второй информационные и управляющий входы, первый, второй и третий управляющие выходы связаны соответственно с информационным выходом блока хранения эталонных значений трендов, с информационным выходом блока формирования трендов, с управляющим выходом блока хранения эталонных значений трендов, с четвертым управляющим входом блока формирования трендов, с вторым управляющим входом блока управления и с вторым управляющим входом блока индикации, информационный, первый и второй управляющие входы блока хранения измерений первого цикла соединены соответственно с информационным выходом аналого-цифрового преобразователя, с вторым управляющим выходом блока управления и с управляющим выходом аналого-цифрового преобразователя, первый и второй информационные, первый, второй и третий управляющие входы блока формирования трендов связаны соответственно с информационным выходом блока хранения измерений первого цикла, с информационным выходом аналого- цифрового преобразователя, с управляющим выходом блока хранения измерений первого цикла, с первым управляющим выходом блока сравнения и с вторым управляющим выходом блока формирования признака производной, управляющий вход блока хранения эталонных значений трендов подключен к управляющему выходу блока формирования трендов, а также тем, что блок хранения измерений первого цикла содержит регистр, пять элементов ИЛИ-НЕ, десять элементов И, элемент памяти, пять триггеров, дешифратор и счетчик, соединенный счетным, сбросовым входами и выходом соответственно с выходом второго элемента И, с выходом второго элемента ИЛИ-НЕ и с входом дешифратора, выход которого связан с первым входом седьмого элемента И и с первым входом восьмого элемента И, второй вход и выход которого подключены соответственно к выходу пятого элемента И и к первому входу второго

элемента ИЛИ-НЕ, вторым входом соединенного с первым управляющим входом блока, хранения изменений первого цикла с вторым входом пятого элемента Ш1И-НЕ, с входом третьего элемента ИЛИ-НЕ, с вторым входом четвертого элемента ИЖ-НЕ и с первым входом первого элемента ИЛИ-НЕ, выход которого соединен со сбросовыми входами первого, второго и третьего

5

0

5

0

5

триггеров, а второй вход - со счетным входом четвертого триггера, с выходом пятого элемента И, с первым входом шестого элемента И и с вторым входом седьмого элемента И, у которого третий вход подключен к первому входу девятого элемента И и к нулевому выходу пя.того триггера, соединенного своими счетным, сбросовым входами соответственно с выходом седьмого элемента И и с выходом третьего элемента РШИ-НЕ, а единичным выходом - с первыми входами первого и десятого элементов И, а также с вторым входом шестого элемента И, первый вход которого связан с выходом пятого элемента И, а выход - с управляющим выходом блока хранения измерений первого цикла, первый управляющий вход которого соединен с вторыми входами третьего, четвертого и пятого элементов И, первый и третий входы пятого элемента И соединены соответственно с единичным входом третьего триггера и с нулевым выходом четвертого триггера, сбросо

25

вый вход которого связан с выходом пятого элемента ИЛИ-НЕ, первым входом подключенного к выходу второго элемента И, к входу четвертого элемента ИЛИ-НЕ и к сбросовому входу первого триггера, сбросовый и нулевой входы третьего триггера соединены соответственно с выходом и с третьим входом .четвертого элемента И, первый вход которого подключен к единичному выходу второго триггера и к второму входу первого элемента И, первый и второй входы второго элемента И связаны соответственно с вторым управляющим входом блока хранения измерений первого цикла и с нулевым выходом первого триггера, единичный вход которого подключен к первому входу третьего элемента И, связанного третьим входом с нулевым выходом второго триггера, а выходом - со счетным входом второго триггера и с вторым входом девятого элемента И, выход которого соединен с входом управления записью элемента памяти, вход управления считыванием которого, а также первый, второй информационные входы и выход подсоединены соответственно к выходу первого элемента И, к информационному, к второму управляющему входам блока хранения измерений первого цикла и к информационному входу регистра, у которого входы управления за5

писью, управления считыванием, сбросовый и выход связаны соответственно с выходом десятого элемента И, с выходом первого элемента И, с выходом четвертого элемен - та ИЛИ - НЕ и с информационным выходом блока хранения измерений первого цикла, второй вход десятого элемента И соединен с выходом четвертого элемента И, а, кроме того тем, что блок формирования трендов содержит три элемента ИЛИ-НЕ, тринадцать элементов И, шесть триггеров, дешифратор, счетчик, регистр, элемент памяти, сумматор и группу из п элементов ИЛИ-НЕ, входы и выходы которых л входом - с выходом шестого элеменподключены соответственно к второму информационному входу блока формирования трендов и к первому информационному входу сумматора, второй инфорта И, со счетным входом третьего тр гера и с первым входом двенадцатого элемента И, второй, вход которого св зан с единичным выходом шестого .

йены соответственно с первым информационным входом формирования трендов и с информационным входом элемента памяти, адресный вход, а также входы

55мационный вход и выход которого соеди- триггера, а выход - с первым входом

одиннадцатого элмента Икс управляющим выходом блока формирования трендов, счетный и сбросовый входы и выход счетчика соединены соответствен10

J520

0465326

управления записью, считыванием и выход которого связаны соответственно с адресным выходом счетчика, с выходом элемента И, с выходом второго элемента И и с информационным входом регистра, у которого входы управления записью, считыванием и сбросовый, а также выход подсоединены соответственно к выходу тринадцатого элемента И, к выходу второго элемента И, к выходу третьего элемента ИЛИ-НЕ и к информационному выходу блока формирования трендов, первый вход тринадцатого элемента И соединен с единичным выходом четвертого триггера, с первым входом девятого элемента И и с вторым входом второго элемента И, а второй вход - с третьим входом первого элемента И, с выходом пятого элемента И и со счетным входом второго триггера, у которого сбросовый вход, единичный и нулевой выходы соединены соответственно с выходом третьего элемента 25 ИЛИ-НЕ, с первым входом шестого элемента И и с третьим входом пятого элемента И, первый вход первого элемента И подключен к нулевому выходу четвертого- триггера и к третьему входу восьмого элемента И, а второй вход - к единичному выходу первого триггера, к первому входу пятого элемента И и к первому входу второго элемента И, входы четвертого элемента И с первого по четвертый связаны соответственно с третьим синхронизирующим, с вторым управляющим входами блока формирования трендов, с выходом третьего элемента И и с нулевым выходом первого триггера, у которого счетный и сбросовый входы подключены соответственно к выходу четвертого элемента И и к выходу второго элемента ИЛИ-НЕ, соединенного своим первьгм входом с вторым синхронизирующим входом блока, с первым входом третьего элемента ИЛИ-НЕ, с первым входом седьмого элемента И и с первым входом четв ертого элемента ИЛИ-НЕ, а втЪрым

30

35

40

45

входом - с выходом шестого элемента И, со счетным входом третьего триггера и с первым входом двенадцатого элемента И, второй, вход которого связан с единичным выходом шестого .

55 т

но с выходом четвертого элемента И, с выходом седьмого элемента И и с вхдом дешифратора, выход которого подключен к первому входу восьмого элемента И и к второму входу одиннадцатого элемента И, соединенного третьим входом и выходом соответственно с единичным выходом пятого триггера и с вторым входом четвертого элемента ИЛИ-НЕ, выход которого подсоединен к второму входу седьмого элемента И и сбросовым входам четвертого, пятого и шестого триггеров, второй вход девятого элемента И соединен с первым синхронизирующим входом блока формирования трендов и с вторыми входами пятого, шестого, восьмого и десятого элементов И, второй вход третьего элемента ИЛИ-НЕ связан с выходом четвертого элемента И, первый вход шестого элемента И - с нулевым выходом третьего триггера, сбросовый вхо и единичный выход которого подключены соответственно к- вьпсоду третьего элемента ИЛИ-НЕ и к второму входу десятого элемента И, у которого первый и четвертый входы и выход связаны соответственно с единичным-выходом пятого триггера, с нулевым выходом и со счетным входом шестого триггера, выход и третий вход девятого элемента И соединены соответственно со счетным входом и с нулевым выходом пятого триггера, первый вход и выход восьмого элемента И связаны соответственно с вторым входом одиннадцатого элемента И и со счетным выходом

четвертого триггера, третий вход седмого элемента И соединен с выходом десятого элемента И, а входы третьего элемента И с первого по тертий - соответственно с первым, с третьим и с четвертым управляющими входами блока формирования трендов, а также тем, что блок хранения эталонных значений трендов содержит регистр, три элемента ИЛИ-НЕ, дешифратор, счетчик три триггера, три элемента И и эле,мент памяти, соединенный адресным входом с выходом счетчика и с входом дешифратора, входом управления считыванием - с единичным выходом первого триггера, с первым входом второго элемента И и с входом управления записью регистра, а информационным выходом - с информационным входом регистра, первый вход первого элемента ИЛИ-НЕ соединен с выходом первого

0

5

0

5

0

0

5

элемента И и со счетными входами первого триггера и счетчика, сбросовый вход которого соединен с выходом третьего элемента ИЛИ-НЕ, связанного вторым выходом с выходом элемента И-НЕ, а первым входом - с вторым синхронизирующим входом блока хранения эталонных значений трендов, с вторым входом второго элемента ИЛИ-НЕ и с вторым входом первого элемента ИЛИ-НЕ, выход которого подключен к сбросовым входам регистра, второго и третьего триггеров, сбросовый вход и нулевой выход первого триггера подсоединены соответственно к выходу второго элемента ИЛИ-НЕ и к второму входу первого элемента И, первый вход которого соединен с управляющим входом блока хранения эталонных значений трендов, первый синхронизирующий вход которого связан с вторыми входами второго и третьего элементов И, счетный вход, единичный и нулевой выходы второго триггера подключены соответственно к выходу второго элемента И, к первому входу третьего элемента И и к третьему входу второго элемента И, третий вход третьего элемента И связан с нулевым выходом третьего триггера, а выход - со счетным входом третьего триггера, с первым входом элемента И-НЕ, с первым входом второго элемента ИЛИ-НЕ и с управляющим выходом блока хранения эталонных значений трендов, информационный выход которого соединен с выходом регистра, выход дешифратора соединен с вторым входом элемента И-НЁ и, наконец тем, что блок сравнения трендов содержит два элемента ИЛИ, п+4 элемента ИЛИ-НЕ, семь элементов И, дешифратор, счетчик, три триггера и сумматор, вторым информационным входом coeд шeнный че- с рез пятые элементы ИЛИ-НЕ с вторым информационным входом блока сравнения, первый информационный и управля-- ющий входы которого связаны соответственно с первым информационным входом сумматора и с первым входом четвертого элемента И, связанного вторым входом с нулевым выходом первого триггера, а выходом - со счетными входами счетчика и первого триггера, а также с первым входом третьего элемента ИЛИ-НЕ, первый синхронизирующий вход блока сравнения трендов подключен к вторым входам пятого и шестого элементов И, а второй синхро

низирующий вход - к второму входу

третьего элемента ИЛИ-ИЕ, к первому входу первого элемента ИЛИ и к первому входу четвертого элемента ИЛИ-ИЕ, связанного выходом со сбросовым вхо- дом первого триггера, а вторым входом - с вторым входом второго элемента ИЛИ, с выходом шестого элемента И и со счетным входом третьего триггера, сбросовый вход которого вместе со сбросовым входом второго триггера подключены к выходу третьего элемента , первый и третий входы пятого элемента И соединены соответственно с единичным выходом первого триггера и с нулевым выходом второго триггера, а выход пятого элемента И - с вторыми входами второго, третьего, седьмого элементов И и со счетным входом второго триггера, единичный выход которого связан с первым входом шестого элемента И, у которого первый вход подсоединен к нулевому выходу третьего триггера, второй вход и выход первого элемента ИЛИ соедине

0

6

5

5

0

5330

ны соответственно о выходом второго элемента ИЛИ и с входом сброса счетчика, выходом че.рез дешифратор связанного с входом второго элемента ИЛИ-НЕ и с третьим входом третьего элемента И, первый вход которого через первый элемент ИЛИ-11Е подсоединен к выходу первого элемента И, связанного также с первым входом второго элемента И, выход второго элемента ИЛИ-НЕ соединен с третьим входом седьмого элемента И и с первым входом второго элемента ИЛИ, первый вход и выход седьмого элемента И соединены соответственно с выходом первого элемента ИЛИ-НЕ и с вторым управляющим выходом блока сравнения трендов, первый и тре.тий управляющие выходы которого подключены соответственно к выходу третьего и к выходу второго элементов И, первых и второй входы первого элемента И соединены соответственно с вторым и с первым информационными выходами сумматора.

фиг.2

К объекта 7

фиг.З

285

фаг.5

m

(Put.ff

296 301

283

28if

(oTro

214

гзг

Фиг.8

фиг. 9

235

фиг, Ю

-JSL-M рш1 кц

фиг, П ,

| Устройство для контроля параметров объектов | 1973 |

|

SU450183A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля параметров | 1975 |

|

SU607190A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-08-30—Публикация

1987-07-10—Подача