Ј

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор базисных функций | 1980 |

|

SU968796A1 |

| Функциональный преобразователь | 1988 |

|

SU1501021A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для обслуживания группы запросов | 1988 |

|

SU1562913A1 |

| Устройство для извлечения квадратного корня из напряжения | 1989 |

|

SU1721615A1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для синхронизации вычислительной системы, работающей в реальном времени. Устройство позволяет корректировать частоты выходных сигналов. Целью изобретения является повышение точности стабилизации среднего значения выходных частот. Поставленная цель достигается за счет введения регистра 8 и сумматоров 5, 6. 3 ил.

сл

СЛ ГО

О5 СЛ

31

Изобретение относится к- автоматике и вычислительной технике и может быть использовано для синхронизации вычислительной системы, работающей в реальном времени.

Целью изобретения является повышение точности стабилизации среднего значения выходных частот,,

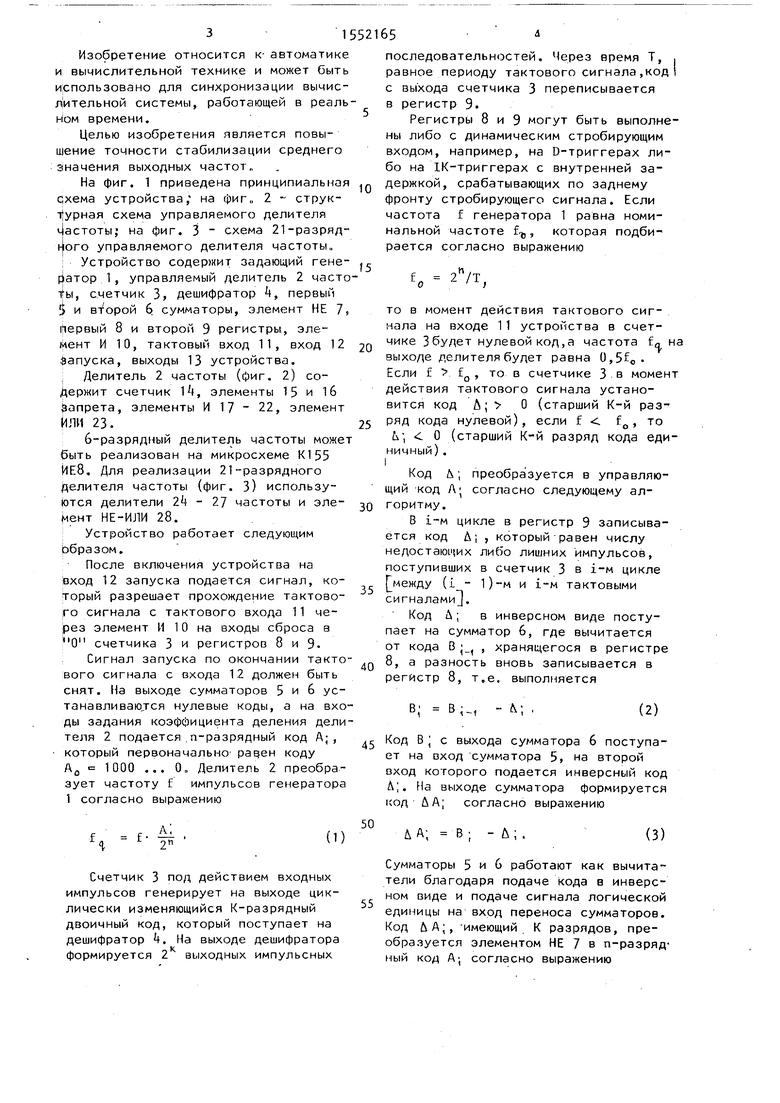

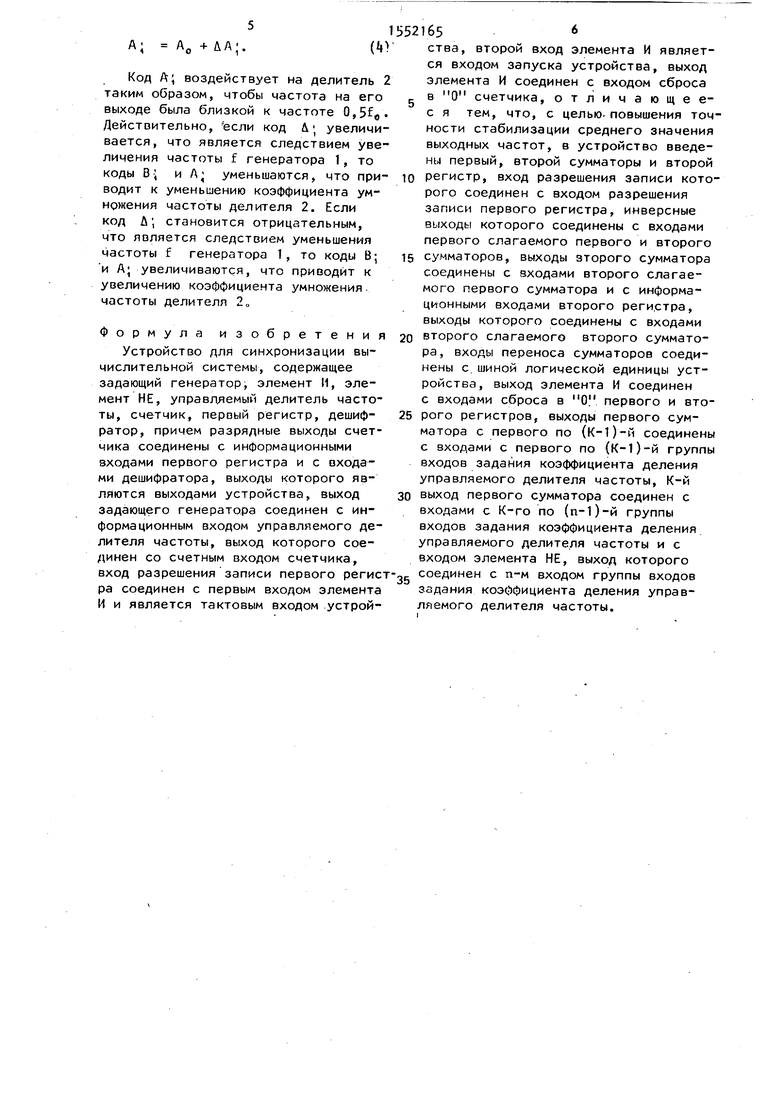

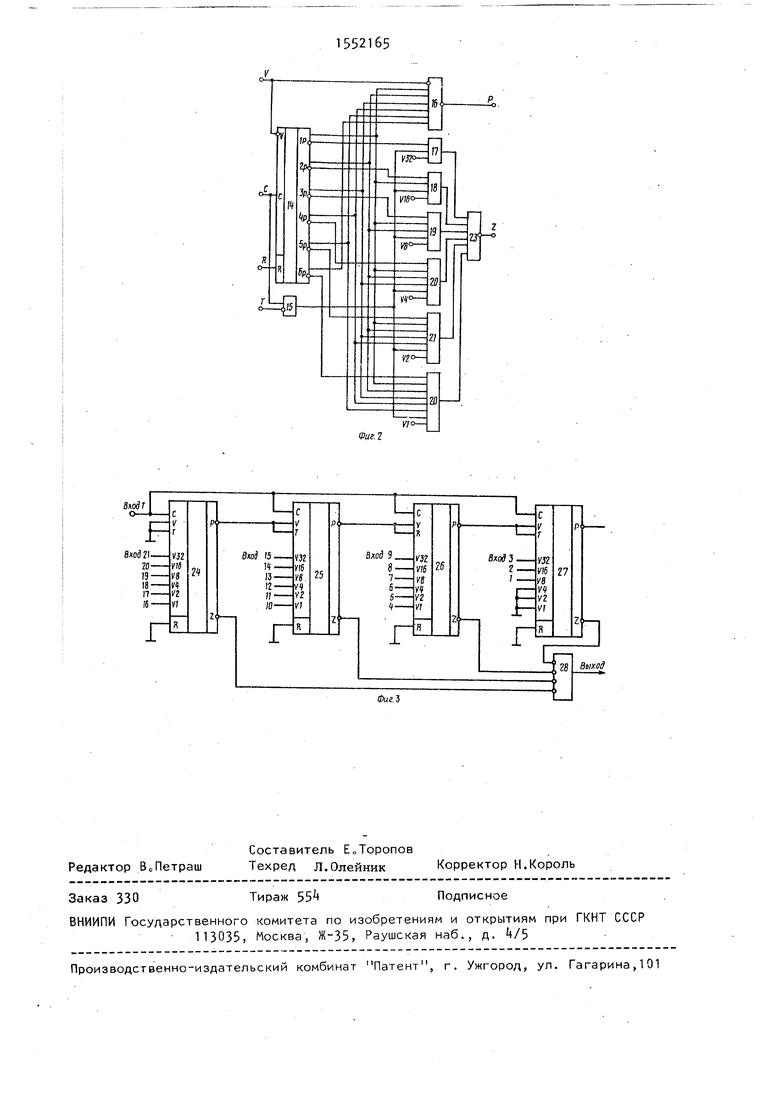

На фиг. 1 приведена принципиальная с,хема устройства; на фиг,, 2 струк- typnafl схема управляемого делителя Частоты; на фиг. 3 схема 21-разряд- Його управляемого делителя частоты,,

Устройство содержит задающий гене- ратор 1, управляемый делитель 2 частоты, счетчик 3, дешифратор k, первый 5 и второй 6 сумматоры, элемент НЕ 7, Первый 8 и второй 9 регистры, элемент И 10, тактовый вход 11, вход 12 Запуска, выходы 13 устройства.

Делитель 2 частоты (фиг. 2) со- Держит счетчик , элементы 15 и 16 Запрета, элементы И 17 22, элемент ИЛИ 23.

6-разрядный делитель частоты может быть реализован на микросхеме К155 ИЕ8, Для реализации 21-разрядного делителя частоты (фиг. 3) используются делители 2 - 27 частоты и эле- Мент НЕ-ИЛИ 28.

Устройство работает следующим образом.

После включения устройства на вход 12 запуска подается сигнал, который разрешает прохождение тактового сигнала с тактового входа 11 через элемент И 10 на входы сброса в О счетчика 3 и регистров 8 и 9.

Сигнал запуска по окончании тактового сигнала с входа 12 должен быть снят. На выходе сумматоров 5 и 6 устанавливаются нулевые коды, а на входы задания коэффициента деления делителя 2 подается n-разрядный код А; , который первоначально рав,ен коду

А,

f - F. A

Ч 2

(D

Счетчик 3 под действием входных импульсов генерирует на выходе циклически изменяющийся К-разрядный двоичный код, который поступает на дешифратор t. На выходе дешифратора формируется 2 выходных импульсных

65 л

последовательностей. Через время Т, , равное периоду тактового сигнала,код 1 с выхода счетчика 3 переписывается в регистр 9.

Регистры 8 и 9 могут быть выполнены либо с динамическим стробирующим входом, например, на D-триггерах либо на IK-триггерах с внутренней задержкой, срабатывающих по заднему фронту стробирующего сигнала. Если частота f генератора 1 равна номинальной частоте f, которая подбирается согласно выражению

fo

,

0

Q

0

то в момент действия тактового сигнала на входе 11 устройства в счетчике 3будет нулевой код,а частота f, на выходе делителя будет равна 0,5f0. Если Ј fQ, то в счетчике 3 в момент действия тактового сигнала установится код Л; 0 (старший К-й разряд кода нулевой), если f f0, то h . О (старший К-й разряд кода единичный) . I

Код Д; преобразуется в управляющий код Л; согласно следующему алгоритму.

В i-м цикле в регистр 9 записывается код Д; , который равен числу недостающих либо лишних импульсов, поступивших в счетчик 3 в i-м цикле между (1 - 1)-м и i-м тактовыми сигналами.

Код Д; в инверсном виде поступает на сумматор 6, где вычитается от кода В j( , хранящегося в регистре 8, а разность вновь записывается в регистр 8, т.е. выполняется

В; В;м - Д:

(2)

Код В ; с выхода сумматора 6 поступает на оход сумматора 5, на второй вход которого подается инверсный код А;. На выходе сумматора формируется код ДА; согласно выражению

50

Д А; В ; - Л ; .

(3)

Сумматоры 5 и 6 работают как вычита- тели благодаря подаче кода в инверсном виде и подаче сигнала логической единицы на вход переноса сумматоров. Код ДА;, -имеющий К разрядов, преобразуется элементом НЕ 7 в п-разряд- ный код А; согласно выражению

А

А„ н- ДА;

Код А; воздействует на делитель 2 таким образом, чтобы частота на его выходе была близкой к частоте 0,5f0- Действительно, если код Л; увеличивается, что является следствием увеличения частоты f генератора 1, то коды В; и Л уменьшаются, что приводит к уменьшению коэффициента умножения частоты делителя 2. Если код Л , становится отрицательным, что является следствием уменьшения частоты f генератора 1, то коды В; и А; увеличиваются, что приводит к увеличению коэффициента умножения частоты делителя 2„

Формула изобретения

Устройство для синхронизации вычислительной системы, содержащее задающий генератор, элемент И, элемент НЕ, управляемый делитель частоты, счетчик, первый регистр, дешифратор, причем разрядные выходы счетчика соединены с информационными входами первого регистра и с входами дешифратора, выходы которого являются выходами устройства, выход задающего генератора соединен с информационным входом управляемого делителя частоты, выход которого соединен со счетным входом счетчика, вход разрешения записи первого регист ра соединен с первым входом элемента И и является тактовым входом устрой(

5521656

ства, второй вход элемента И является входом запуска устройства, выход элемента И соединен с входом сброса в О счетчика, отличающее- с я тем, что, с целью- повышения точности стабилизации среднего значения выходных частот, в устройство введены первый, второй сумматоры и второй

Ю регистр, вход разрешения записи которого соединен с входом разрешения записи первого регистра, инверсные выходы которого соединены с входами первого слагаемого первого и второго

15 сумматоров, выходы второго сумматора соединены с входами второго слагаемого первого сумматора и с информационными входами второго регистра, выходы которого соединены с входами

2о второго слагаемого второго сумматора, входы переноса сумматоров соединены с шиной логической единицы устройства, выход элемента И соединен с входами сброса в О первого и вто25 рого регистров, выходы первого сумматора с первого по (К-1)-й соединены с входами с первого по (К-1)-й группы входов задания коэффициента деления управляемого делителя частоты, К-й

30 выход первого сумматора соединен с входами с К-го по (п-1)-й группы входов задания коэффициента деления управляемого делителя частоты и с входом элемента НЕ, выход которого

35

соединен с n-м входом группы входов задания коэффициента деления управляемого делителя частоты.

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1149235A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для синхронизации вычислительной системы | 1986 |

|

SU1456942A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-03-23—Публикация

1988-07-07—Подача