131

фазовращатель 4 смещения, блоки 5, 15 компенсирующего тока,, рабочий фазовращатель 6, блок 7 фазовых компараторов, шифратор 8, счетчики 9, 14, опорные компараторы 10,- 11, логический блок 12, генератор импульсов 13, блок 16 адаптации, блок 17 управления, токоограничивающий элемент 18, двухполюсный выключатель 19. Цель достигается тем, что для компенсации согласования используются неустановившиеся значения токов, генерируемых блоками 5 и 15 компенсирующего тока, промежуточных значений которых, различных для различных значений входных сигналов, компенсирующие токи достигают значительно быстрее. Для фиксации моментов времени соот1

Изобретение относится к измерительной и вычислительной технике.

Целью изобретения является повьше няе быстродействия.

Поставленная цель достигается путем изменения времени компенсации в зависимости от величины преобразуемого сигнала за счет введения счет-- чика грубого отсчета и наличия цепи переноса между счетчиками грубого и точного отсчетов.

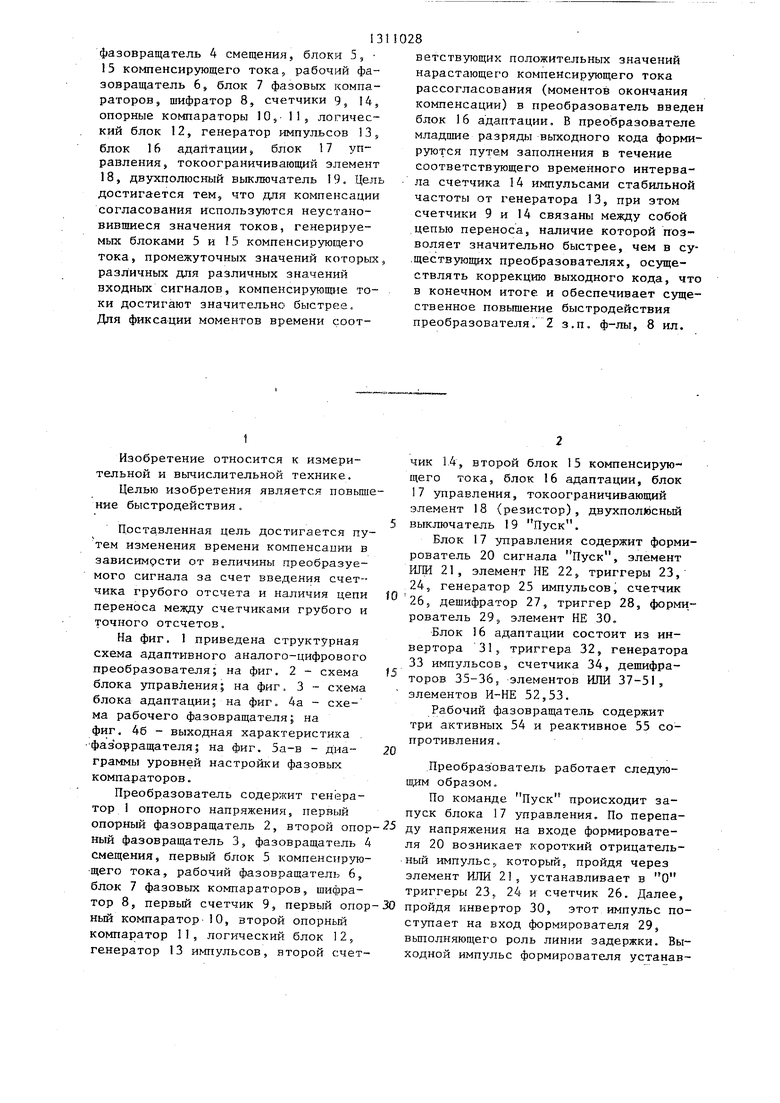

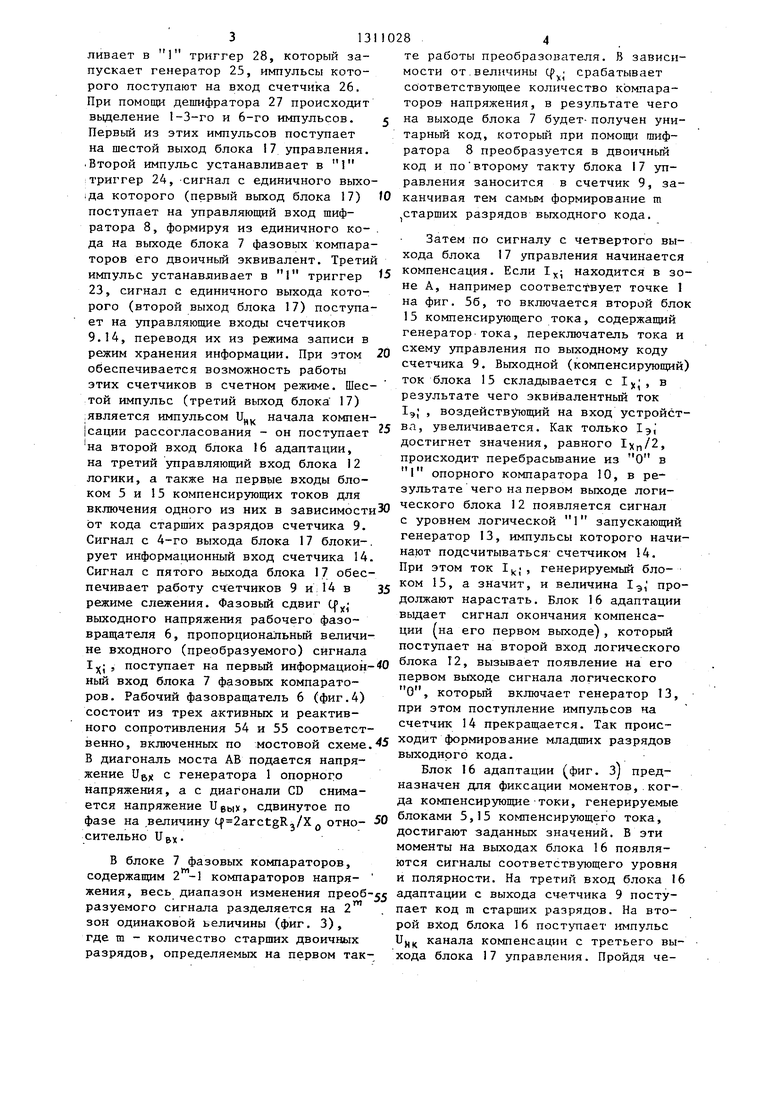

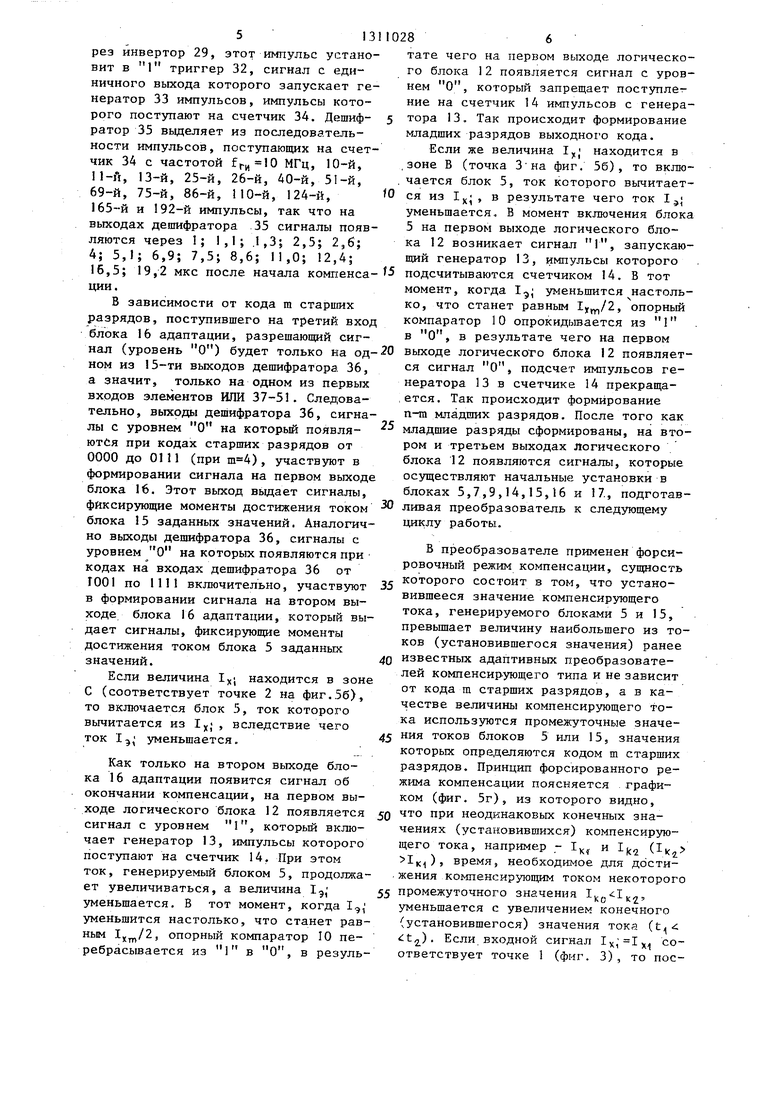

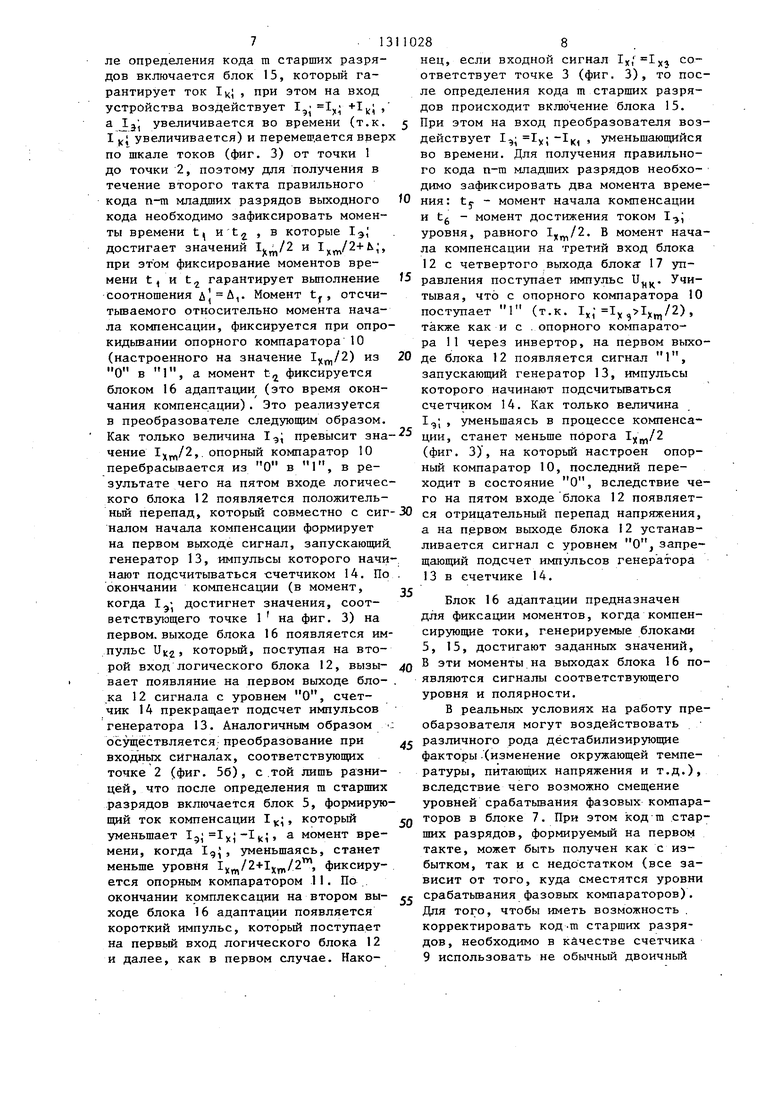

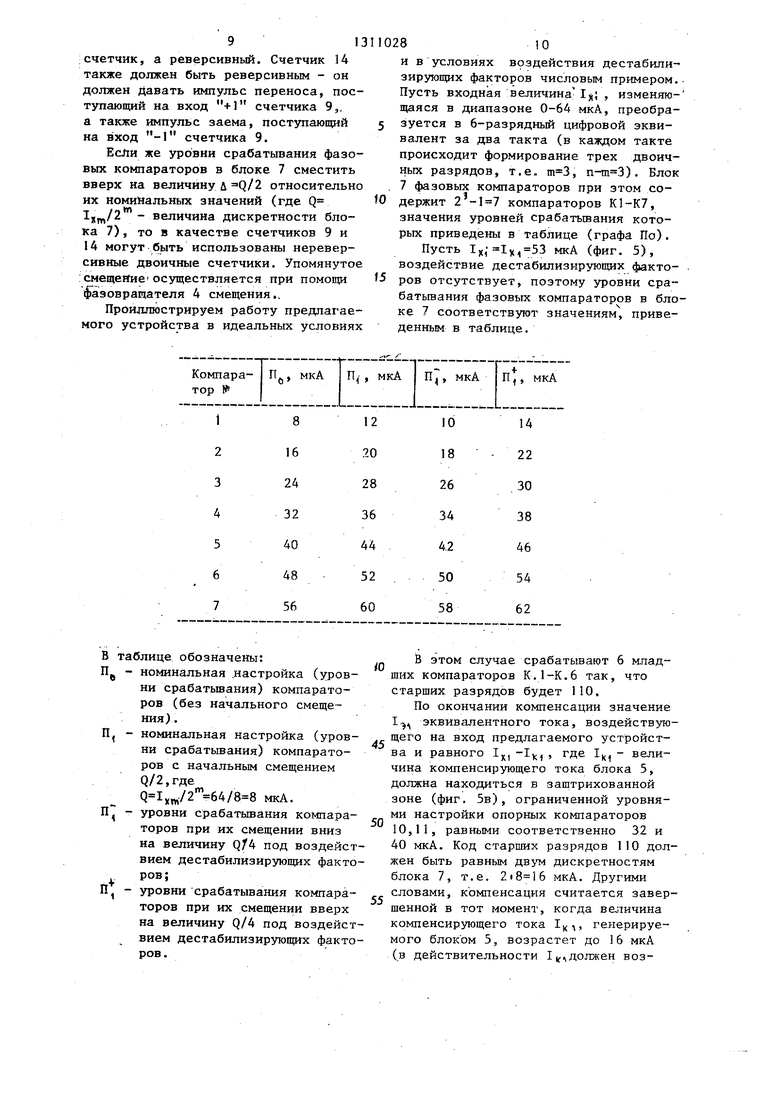

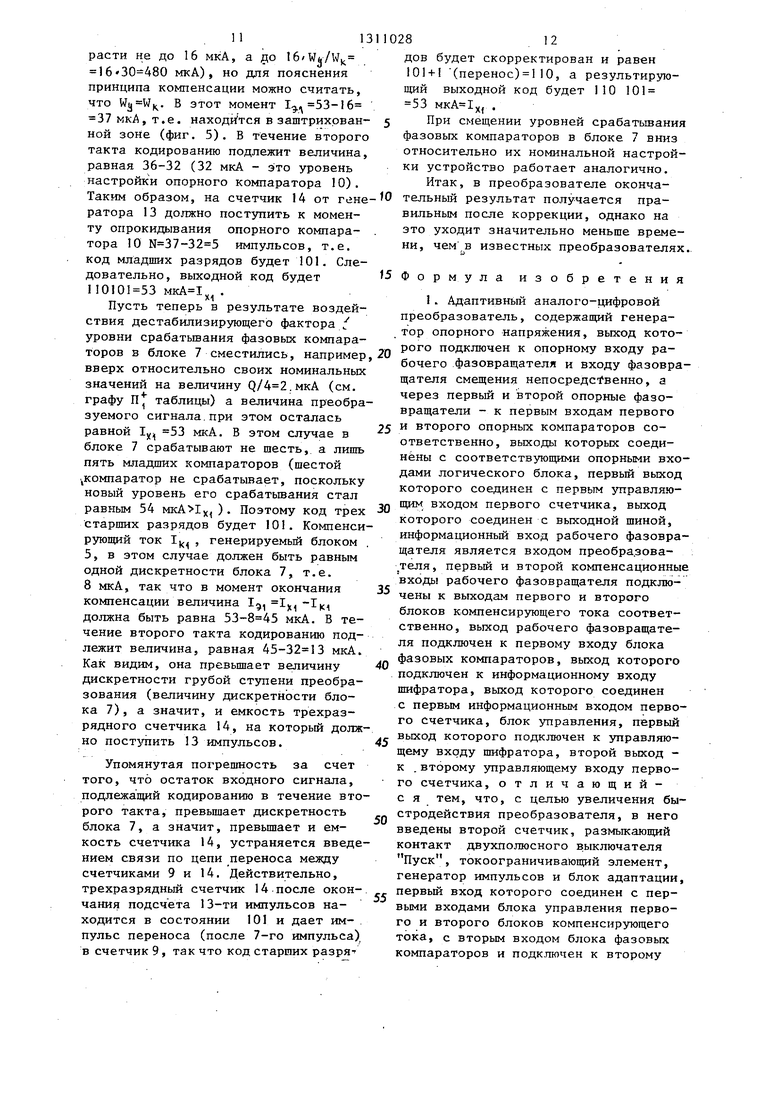

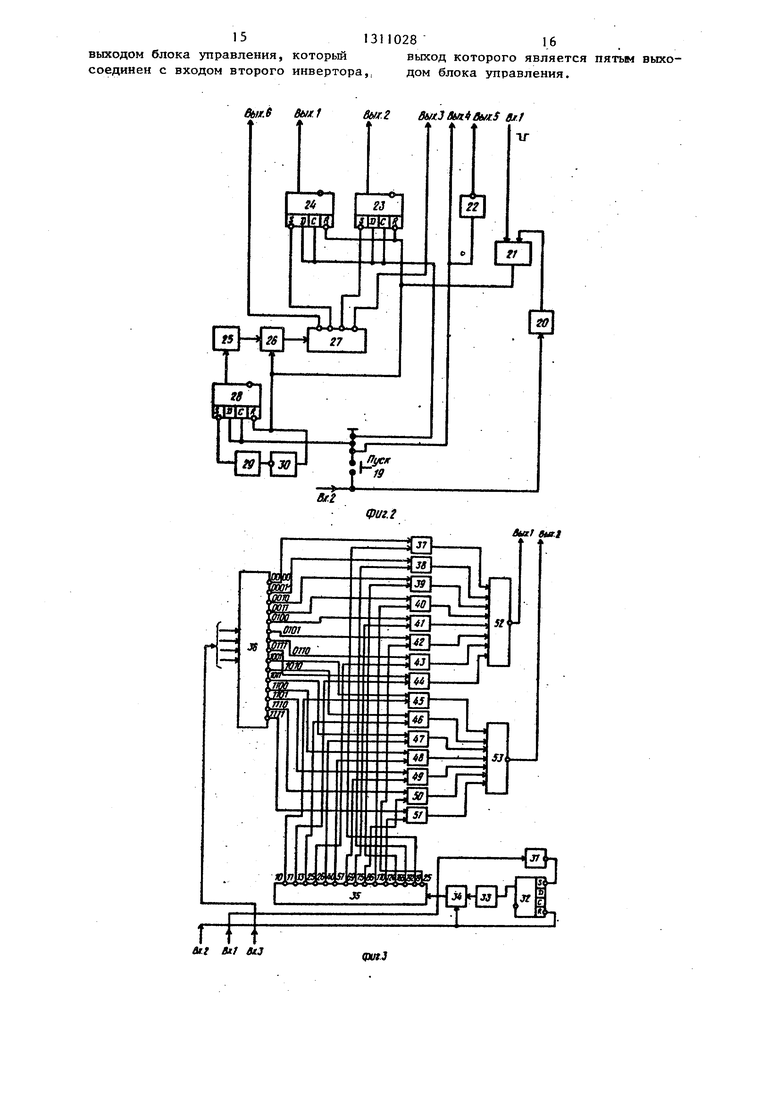

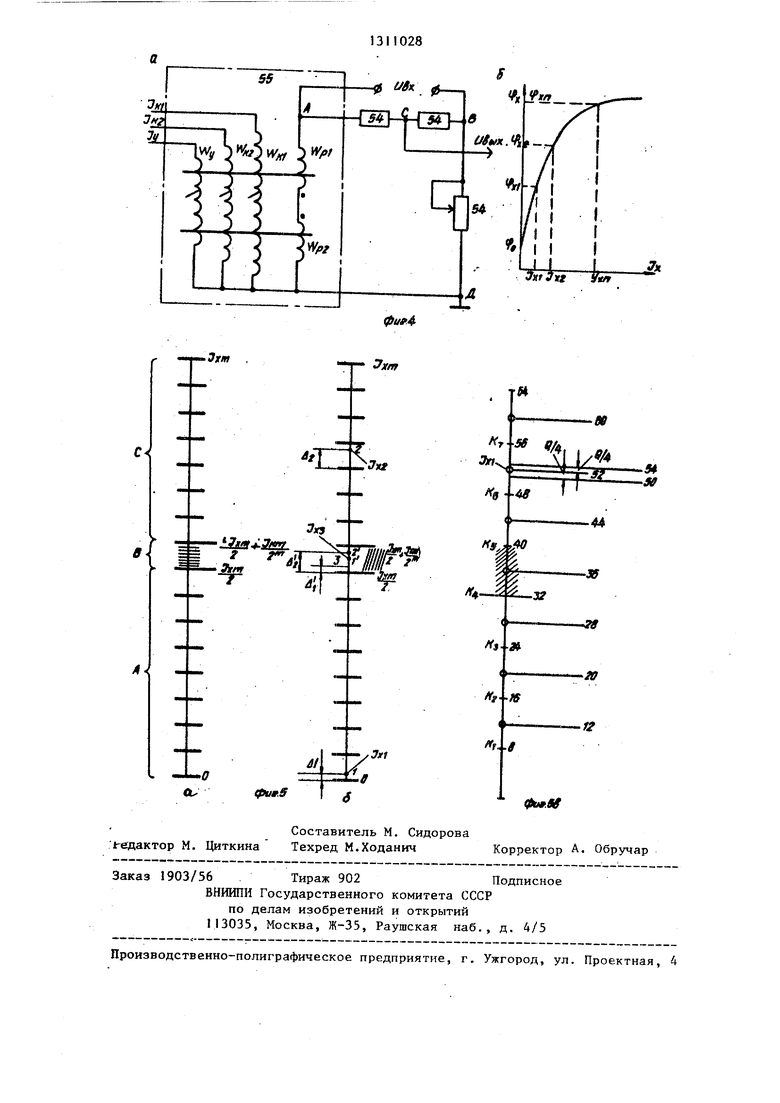

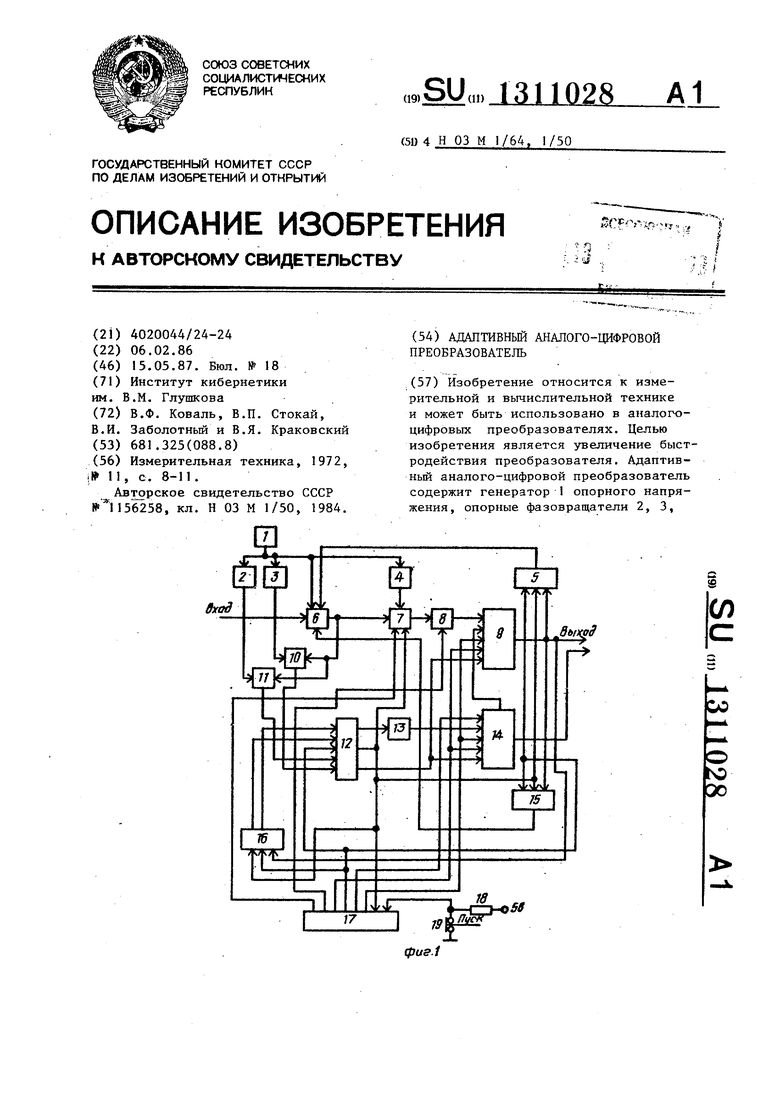

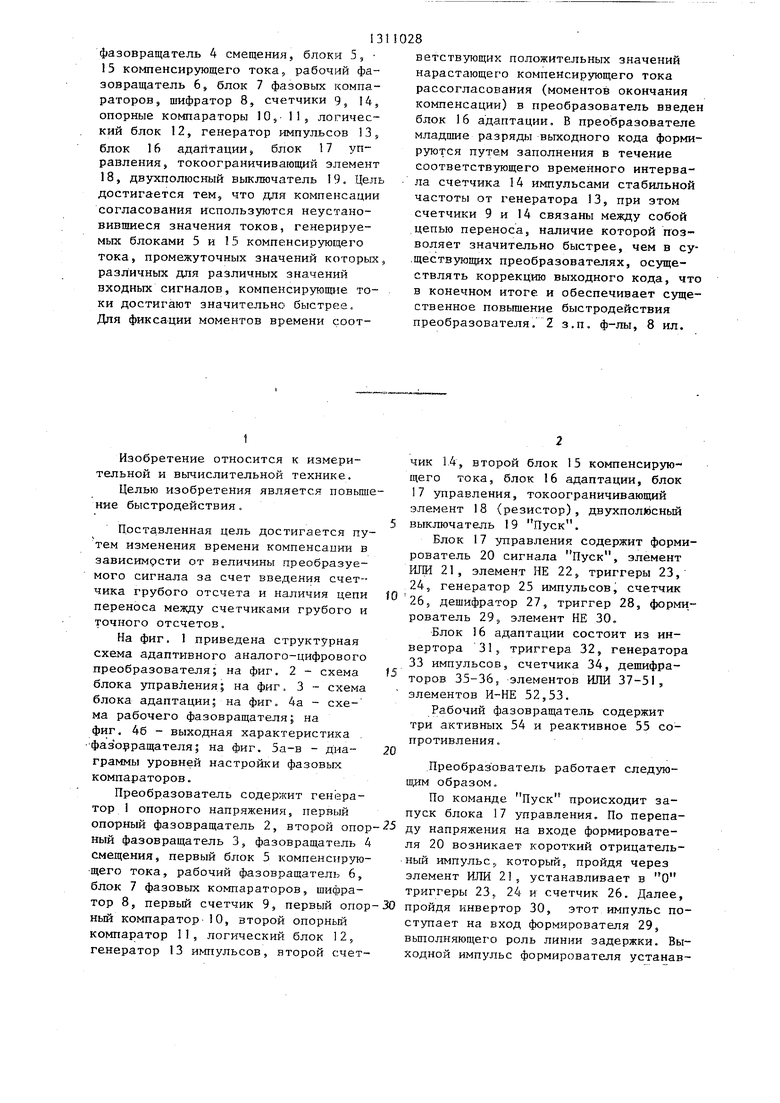

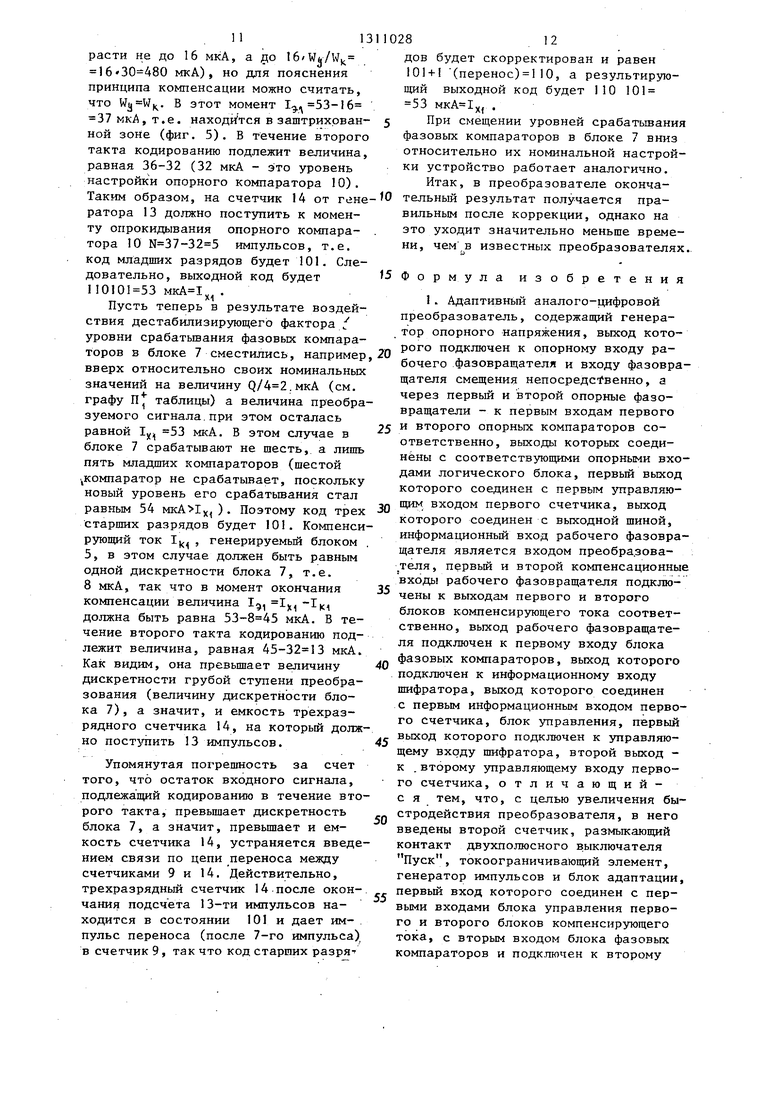

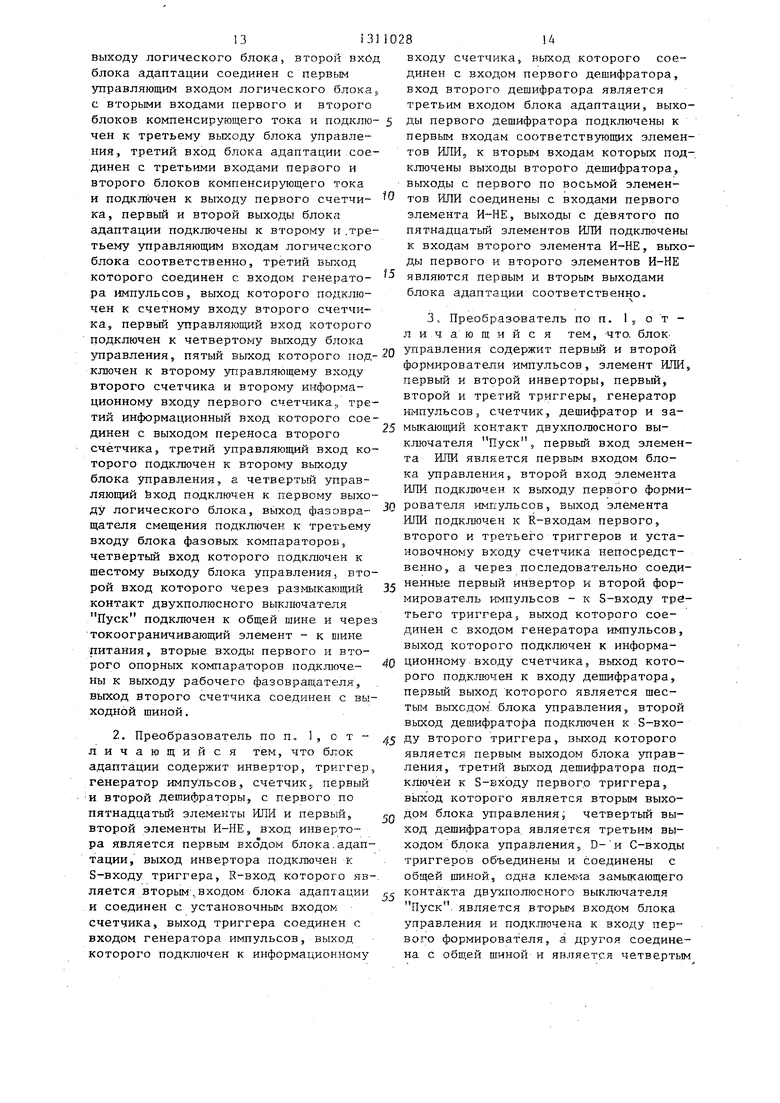

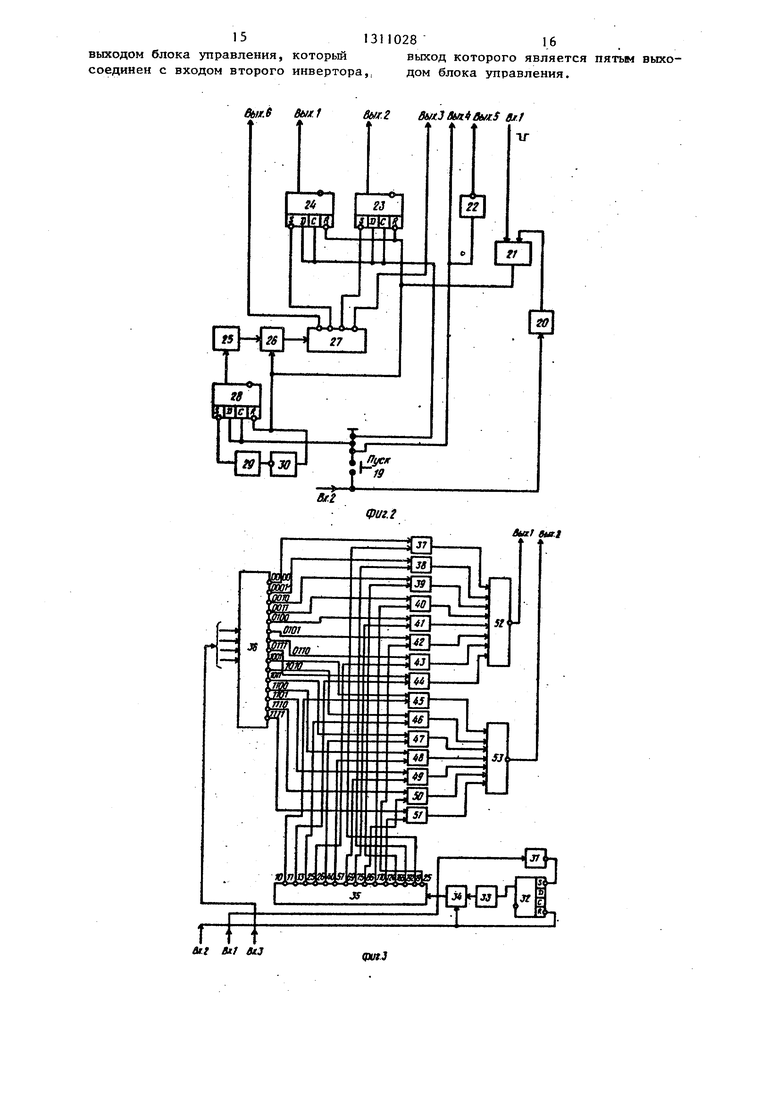

На фиг. 1 приведена структурная схема адаптивного аналого-цифрового преобразователя; на фиг. 2 - схема блока управления; на фиг, 3 - схема блока адаптации; на фиг. 4а - схе- ма рабочего фазовращателя; на фиг. 4б - выходная характеристика фаз орращателя; на фиг. 5а-в - диаграммы уровней настройки фазовых компараторов.

Преобразователь содержит генератор опорного напряжения, первый опорный фазовращатель 2, второй опорный фазовращатель 3, фазовращатель 4 смещения, первый блок 5 компенсирзто- щего тока, рабочий фазовращатель 6, блок 7 фазовых компараторов, шифратор 8, первый счетчик 9, первый опорный компаратор 10, второй опорньй компаратор 11, логический блок 12, генератор 13 импульсов, второй счет28

ветствующих положительных значений нарастающего компенсирующего тока рассогласования (моментов окончания компенсации) в преобразователь введен блок 16 адаптации. В преобразователе младшие разряды выходного кода формируются путем заполнения в течение соответствующего временного интервала счетчика 14 импульсами стабильной частоты от генератора 13, при этом счетчики 9 и 14 связаны между собой цепью переноса, наличие которой позволяет значительно быстрее, чем в су- .ществующих преобразователях, осуществлять коррекцию выходного кода, что в конечном итоге и обеспечивает существенное повышение быстродействия преобразователя. Z з.п. ф-лы, 8 ил.

чик 14, второй блок 15 компенсирующего тока, блок 16 адаптации, блок 17 управления, токоограничивающий элемент 18 (резистор), двухполюсный выключатель 19 Пуск.

Блок I7 управления содержит формирователь 20 сигнала Пуск, элемент ИЛИ 21, элемент НЕ 22, триггеры 23, 24, генератор 25 импульсов, счетчик

26, дешифратор 27, триггер 28, формирователь 29;, элемент НЕ 30.

Блок 16 адаптации состоит из инвертора 31, триггера 32, генератора 33 импульсов, счетчика 34, дешифраторов 35-36, элементов ИЛИ 37-51, элементов И-НЕ 52,53.

Рабочий фазовращатель содержит три активных 54 и реактивное 55 сопротивления.

Преобразователь работает следующим образом,,

По команде Пуск происходит запуск блока 17 управления. По перепаду напряжения на входе формирователя 20 возникает короткий отрицательный импульс,, который, пройдя через элемент ШШ 21, устанавливает в О триггеры 23,, 24 и счетчик 26. Далее,

пройдя инвертор 30, этот импульс поступает на вход формирователя 29, вьшолняющего роль линии задержки. Выходной импульс формирователя устанавливает в 1 триггер 28, который запускает генератор 25, импульсы которого поступают на вход счетчика 26, При помощи дешифратора 27 происходит выделение 1-3-го и 6-го импульсов. /j Первый из этих импульсов поступает на шестой выход блока 17 управления. Второй импульс устанавливает в 1 триггер 24, сигнал с единичного выхо- 1да которого (первый выход блока 17) 10 поступает на управляющий вход шифратора 8, формируя из единичного ко- . да на выходе блока 7 фазовых компараторов его двоичный эквивалент. Третий импульс устанавливает в 1 триггер -5 23, сигнал с единичного выхода которого (второй выход блока 17) поступает на управляющие входы счетчиков 9.14, переводя их из режима записи в режим хранения информации. При этом 20 обеспечивается возможность работы этих счетчиков в счетном режиме. Шестой импульс (третий выход блока 17)

те работы преобразователя. В зависимости от.величины ср срабатывает соответствующее количество компараторов напряжения, в результате чего на выходе блока 7 будет- получен унитарный код, который при помощи шифратора 8 преобразуется в двоичный код и по второму такту блока 17 управления заносится в счетчик 9, заканчивая тем самым формирование m старших разрядов выходного кода.

Затем по сигналу с четвертого выхода блока 17 управления начинается компенсация. Если находится в зоне А, например соответствует точке 1 на фиг. 56, то включается второй блок 15 компенсирующего тока, содержащий генератор тока, переключатель тока и схему управления по выходному коду счетчика 9. Выходной (компенсирующий)

ток блока 15 складывается с I результате чего эквивалентный ток

X,

:является импульсом и„., начала компен-9,

воздействующий на вход устройст1- П1ч,с ва, увеличивается. Как только It,

|сации рассогласования - он поступает

достигнет значения, равного 1хг,/2,

происходит перебрасьшание из О в I опорного компаратора 10, в результате чего на первом выходе логи на второй вход блока 16 адаптации, на третий управляющий вход блока 12 логики, а также на первые входы блоком 5 и 15 компенсирующих токов для включения одного из них в зависимости30 от кода старших разрядов счетчика 9. Сигнал с 4-го выхода блока 17 блоки-. рует информационный вход счетчика 14. Сигнал с пятого выхода блока 17 обеспечивает работу счетчиков 9 И;14 в 35 режиме слежения. Фазовый сдвиг Cf выходного напряжения рабочего фазовращателя 6, пропорциональный величине входного (преобразуемого) сигнала , поступает на первый информацион-40 ный вход блока 7 фазовых компараторов. Рабочий фазовращатель 6 (фиг.4) состоит из трех активных и реактивческого блока 12 появляется сигнал с уровнем логической I запускающий генератор 13, импульсы которого начинают подсчитываться счетчиком 14. При этом ток lid, генерируемый блоком 15, а значит, и величина I-j, продолжают нарастать. Блок 16 адаптации выдает сигнал окончания компенсации (на его первом выходе), который поступает на второй вход логического блока 12, вызывает появление на его первом вьгходе сигнала логического О, который включает генератор 13, при этом поступление импульсов на счетчик 14 прекращается. Так происческого блока 12 появляется сигнал с уровнем логической I запускающий генератор 13, импульсы которого начинают подсчитываться счетчиком 14. При этом ток lid, генерируемый блоком 15, а значит, и величина I-j, продолжают нарастать. Блок 16 адаптации выдает сигнал окончания компенсации (на его первом выходе), который поступает на второй вход логического блока 12, вызывает появление на его первом вьгходе сигнала логического О, который включает генератор 13, при этом поступление импульсов на счетчик 14 прекращается. Так происного сопротивления 54 и 55 соответст(5 ходит формирование младших разрядов

выходного кода.

Блок 16 адаптации (фиг. з предназначен для фиксации моментов,.когда компенсирующие-токи, генерируемые Q блоками 5,15 компенсирующего тока, достигают заданных значений. В эти моменты на выходах блока 16 появляются сигналы соответствующего уровня

венно, включенных по мостовой схеме, В диагональ моста АВ подается напряжение UBX с генератора 1 опорного напряжения, а с диагонали CD снимается напряжение U еых сдвинутое по фазе на .величину Cf 2arctgRj/X относительно UBX

и полярности. На третий вход блока 16

В блоке 7 фазовых компараторов, содержащим 2 -1 компараторов напряжения, весь диапазон изменения преоб-сг адаптации с выхода счетчика 9 постуYW

разуемого сигнала разделяется на 2 .пает код га старших разрядов. На втозон одинаковой ьеличины (фиг. 3),рой вход блока 16 поступает импульс

где m - количество старших двоичныхUj, канала компенсации с третьего выразрядов, определяемых на первом так-хода блока 17 управления. Пройдя чете работы преобразователя. В зависимости от.величины ср срабатывает соответствующее количество компараторов напряжения, в результате чего на выходе блока 7 будет- получен унитарный код, который при помощи шифратора 8 преобразуется в двоичный код и по второму такту блока 17 управления заносится в счетчик 9, заканчивая тем самым формирование m старших разрядов выходного кода.

Затем по сигналу с четвертого выхода блока 17 управления начинается компенсация. Если находится в зоне А, например соответствует точке 1 на фиг. 56, то включается второй блок 15 компенсирующего тока, содержащий генератор тока, переключатель тока и схему управления по выходному коду счетчика 9. Выходной (компенсирующий)

ток блока 15 складывается с I результате чего эквивалентный ток

X,

-9,

ческого блока 12 появляется сигнал с уровнем логической I запускающий генератор 13, импульсы которого начинают подсчитываться счетчиком 14. При этом ток lid, генерируемый блоком 15, а значит, и величина I-j, продолжают нарастать. Блок 16 адаптации выдает сигнал окончания компенсации (на его первом выходе), который поступает на второй вход логического блока 12, вызывает появление на его первом вьгходе сигнала логического О, который включает генератор 13, при этом поступление импульсов на счетчик 14 прекращается. Так происи полярности. На третий вход блока 16

адаптации с выхода счетчика 9 посту513

рез инвертор 29, этот и myльc установит в 1 триггер 32, сигнал с единичного выхода которого запускает генератор 33 импульсов, импульсы которого поступают на счетчик 34. Дешифратор 35 выделяет из последоват ль- ности импульсов, поступающих на счетчик 34 с частотой ff,j,10 МГц, 10-й, Il-ft, 13-й, 25-й, 26-й, 40-й, 51-й, 69-й, 75-й, 86-й, 110-й, 124-й, 165-й и 192-й импульсы, так что на выходах дешифратора 35 сигналы появляются через 1; 1,1; 1,3; 2,5; 2,6; 4; 5,1; 6,9; 7,5; 8,6; 11,0; 12,4; 16,5; 19,2 МКС после начала компенсации.

В зависимости от кода га старших разрядов, поступившего на третий вход блока 16 адаптации, разрешающий сигнал (уровень О) будет только на одном из 15-ти выходов дешифратора 36, а значит, только на одном из первых входов элементов ИЛИ 37-51. Следовательно, выходы дешифратора 36, сигналы с уровнем О на которьй появляются при кодах старших разрядов от 0000 до 0111 (при ), участвуют в формировании сигнала на первом выходе блока 16. Этот выход выдает сигналы, фиксирующие моменты достижения током блока 15 заданных значений. Аналогично выходы дешифратора 36, сигналы с уровнем О на которых появляются при кодах на входах дешифратора 36 от TOOI по 1111 включительно, участвуют в формировании сигнала на втором выходе блока 16 адаптации, который выдает сигналы, фиксирующие моменты достижения током блока 5 заданных значений.

Если величина 1 находится в зоне С (соответствует точке 2 на фиг.56), то включается блок 5, ток которого вычитается из , вследствие чего ток I, уменьшается.

Как только на втором выходе блока 16 адаптации появится сигнал об окончании компенсации, на первом выходе логического блока 12 появляется сигнал с уровнем I, который включает генератор 13, импульсы которого поступают на счетчик 14. При этом ток, генерируемый блоком 5, продолжает увеличиваться, а величина 1, З меньшается. В тот момент, когда 1, уменьшится настолько, что станет равным , опорный компаратор 10 перебрасывается из 1 в О, в резуль86

тате чего на первом выходе логического блока 12 появляется сигнал с уровнем О, который запрещает поступление на счетчик 14 импульсов с генератора 13. Так происходит формирование младших разрядов выходного кода.

Если же величина находится в зоне В (точка З на фиг. 56), то включается блок 5, ток которого вычитается из 1х; в результате чего ток I уменьшается., В момент включения блока 5 на первом выходе логического блока 12 возникает сигнал I, запускающий генератор 13, импульсы которого

подсчитываются счетчиком 14. В тот момент, когда уменьшится настолько, что станет равным , опорный компаратор 1 О опрокидывается из I в О, в результате чего на первом

выходе логического блока 12 появляется сигнал О, подсчет импульсов генератора 13 в счетчике 14 прекраща- ется. Так происходит формирование п-га младших разрядов. После того как

младшие разряды сформированы, на втором и третьем выходах логического блока 12 появляются сигналы, которые осуществляют начальные установки в блоках 5,7,9,14,15,16 и 17, подготавливая преобразователь к следующему цик:лу работы.

В преобразователе применен форси- ровочный режим компенсации, сущность

которого состоит в том, что установившееся значение компенсирующего тока, генерируемого блоками 5 и 15, превьштает величину наибольшего из токов (установившегося значения) ранее

известных адаптивных преобразователей компенсирующего типа и не зависит от кода m старших разрядов, а в качестве величины компенсирующего тока используются промежуточные значения токов блоков 5 или 15, значения которых определяются кодом m старших разрядов. Принцип форсированного режима компенсации поясняется графиком (фиг. 5г), из которого видно,

что при неодинаковых конечных значениях (установившихся) компенсирующего тока, например - 1 и 1 (1к, 1), время, необходимое для дости- жения компенсирующим током некоторого

промежуточного значения ,„, уменьшается с увеличением конечного (установившегося) значения тока (t t). Если входной сигнал 1х, соответствует точке 1 (фиг. 3), то после определения кода m старших разрядов включается блок 15, который гарантирует ток 1ц; , при этом на вход

.

(т.к.

устройства воздействует I

а увеличивается во

I .xi увеличивается) и перемещается вверх

91

времени

по шкале токов (фиг, 3) от точки 1 до точки 2, поэтому для получения в течение второго такта правильного кода n-m младших разрядов выходного кода необходимо зафиксировать моменты времени t H t в которые 1, достигает значений I) и 1,(/2+Л;, при этом фиксирование моментов времени t, и t гарантирует выполнение

Момент t,, отсчинец, если входной сигнал ответствует точке 3 (фиг. 3), то пос ле определения кода m старших разрядов происходит включение блока 5. При этом на вход преобразователя воздействует I,; 1у; -IK, , уменьшающийся во времени. Для получения правильного кода n-m младших разрядов необходимо зафиксировать два момента време- ния: tc - момент начала компенсации

fO

Ч tfe момент достижения током

J5

соотношения д| Д,. ., тываемого относительно момента начала компенсации, фиксируется при опрокидывании опорного компаратора 10 (настроенного на значение ) из 20 О в 1, а момент t фиксируется блоком 16 адаптации (это время окончания компенсации). Это реализуется в преобразователе следующим образом. Как только величина превысит зна-- чение 15(/2,. опорный компаратор 10 перебрасывается из О в 1, в результате чего на пятом входе логического блока 12 появляется положительный перепад, который совместно с сиг-30 ся отрицательный перепад напряжения,

уровня, равного . В момент начала компенсации на третий вход блока 12 с четвертого выхода блока 17 управления поступает импульс U-.... Учип 1

тывая, что с опорного компаратора 10 поступает 1 (т.к. 1, 1 /2), также как и с .опорного компаратора 11 через инвертор, на первом выходе блока 12 появляется сигнал 1, запускающий генератор 13, импульсы которого начинают подсчитьгоаться счетчиком 14. Как только величина Ig;, уменьшаясь в процессе компенсации, станет меньше порога (фиг. 3), на который настроен опорный компаратор 10, последний переходит в состояние О, вследствие чего на пятом входе блока 12 появляетналом начала компенсации формирует на первом выходе сигнал, запускающий, генератор 13, импульсы которого начинают подсчитьшаться счетчиком 14. По окончании компенсации (в момент,

когда достигнет значения, соответствующего точке 1 на фиг. 3) на первом, выходе блока 16 появляется импульс Uj;2, который, поступая на второй вход логического блока 12, вызывает появляние на первом выходе бло- . ка 12 сигнала с уровнем О, счетчик 14 прекращает подсчет импульсов генератора 13. Аналогичным образом : осуществляется; преобразование при входньпс сигналах, соответствующих точке 2 (фиг. 56), с .той лишь разницей, что после определения m старших разрядов включается блок 5, формируюа на п.ервом выходе блока 12 устанавливается сигнал с уровнем О, запрещающий подсчет импульсов генератора 13 в счетчике 14.

35

40

Блок 16 адаптации предназначен для фиксации моментов, когда компенсирующие токи, генерируемые блоками 5, 15, достигают заданных значений,

8эти моменты на выходах блока 16 появляются сигналы соответствующего уровня и полярности.

В реальных условиях на работу пре- обарзователя могут воздействовать

различного рода дестабилизирующие факторы .(изменение окружающей температуры, питающих напряжения и т.д.), вследствие чего возможно смещение уровней срабатьшания фазовых компаращий ток компенсации I

уменьшает 1,

Ixi-I

1С1

который

j, а момент времени, когда Igi уменьшаясь, станет

меньше уровня i /2+Iy /2 фиксируется опорньм компаратором 11. По . окончании крмплексации на втором выходе блока 16 адаптации появляется короткий импульс, который поступает на первьй вход логического блока 12 и далее, как в первом случае. Нако

Ixj СО

110288

нец, если входной сигнал ответствует точке 3 (фиг. 3), то пос ле определения кода m старших разрядов происходит включение блока 5. При этом на вход преобразователя воздействует I,; 1у; -IK, , уменьшающийся во времени. Для получения правильного кода n-m младших разрядов необходимо зафиксировать два момента време- ния: tc - момент начала компенсации

fO

Ч tfe момент достижения током

ся отрицательный перепад напряжения,

уровня, равного . В момент начала компенсации на третий вход блока 12 с четвертого выхода блока 17 управления поступает импульс U-.... Учип 1

тывая, что с опорного компаратора 10 поступает 1 (т.к. 1, 1 /2), также как и с .опорного компаратора 11 через инвертор, на первом выходе блока 12 появляется сигнал 1, запускающий генератор 13, импульсы которого начинают подсчитьгоаться счетчиком 14. Как только величина Ig;, уменьшаясь в процессе компенсации, станет меньше порога (фиг. 3), на который настроен опорный компаратор 10, последний переходит в состояние О, вследствие чего на пятом входе блока 12 появляета на п.ервом выходе блока 12 устанавливается сигнал с уровнем О, запрещающий подсчет импульсов генератора 13 в счетчике 14.

Блок 16 адаптации предназначен для фиксации моментов, когда компенсирующие токи, генерируемые блоками 5, 15, достигают заданных значений,

8эти моменты на выходах блока 16 появляются сигналы соответствующего уровня и полярности.

В реальных условиях на работу пре- обарзователя могут воздействовать

различного рода дестабилизирующие факторы .(изменение окружающей температуры, питающих напряжения и т.д.), вследствие чего возможно смещение уровней срабатьшания фазовых компараторов в блоке 7. При этом код m старших разрядов, формируемый на первом такте, может быть получен как с избытком, так и с недостатком (все зависит от того, куда сместятся уровни

срабатьшания фазовых компараторов). Для того, чтобы иметь возможность . корректировать код-га старших разрядов, необходимо в качестве счетчика

9использовать не обычный двоичный

913

:счетчик, а реверсивный. Счетчик 14 также должен быть реверсивным - он должен давать импульс переноса, поступающий на вход +1 счетчика 9;,, а также импульс заема, поступающий на вход -1 счетчика 9.

Если же уровни срабатывания фазовых компараторов в блоке 7 сместить вверх на величину относительно их номинальных значений (где Q 1, величина дискретности блока 7), то в качестве счетчиков 9 и 14 могут быть использованы нереверсивные двоичные счетчики. Упомянутое :смещеяие осуществляется при помовщ фазовращателя 4 смещения..

Проиллюстрируем работу предлагаемого устройства в идеальных условиях

блице обозначены:

номинальная .настройка (уровни срабатьшания) компараторов (без начального смещения) .

номинальная настройка (уровни срабатьшания) компараторов с начальным смещением д/2,где

мкА. уровни срабатывания коютара- торов при их смещении вниз на величину Qf4 под воздействием дестабилизирующих факто- ров;

- уровни срабатывания компараторов при их смещении вверх на величину Q/4 под воздействием дестабилизирующих факторов.

102810

и в условиях воздействия дестабили-- зирующих факторов числовым примером, Пусть входная величина , изменяю- щаяся в диапазоне 0-64 мкА, преобра- 5 зуется в 6-разрядньй цифровой эквивалент за два такта (в каждом такте происходит формирование трех двоичных разрядов, т.е. , ). Блок . 7 фазовых компараторов при этом содержит 2 компараторов К1-К7, значения уровней срабатьшания которых приведены в таблице (графа По).

Пусть 1х, мкА (фиг. 5), воздействие дестабилизирующих факторов отсутствует, поэтому уровни срабатьшания фазовых компараторов в блоке 7 соответствуют значениям, приведенным в таблице.

o

5

В этом случае срабатывают 6 младших компараторов К.1-К.6 так, что старших разрядов будет 110.

По окончании компенсации значение 1 эквивалентного тока, воздействующего на вход предлагаемого устройства и равного Ij(, Ifci где 1 - величина компенсирующего тока блока 5, должна находиться в защтрихованной зоне (фиг. 5в), ограниченной уровнями настройки опорных компараторов 10,11, равными соответственно 32 и 40 мкА. Код старших разрядов 110 должен быть равным двум дискретностям блока 7, т.е. мкА. Другими словами, компенсация считается завершенной в тот момент, когда величина компенсирующего тока . генерируемого блоком 5,, возрастет до 16 мкА (в действительности 1,должен воз1113

расти не до 16 мкА, а до 16 Wh/W| 16-30 480 мкА), но для пояснения принципа компенсации можно считать.

что ,.

В этот момент 1.53-16

37 мкА, т.е. находится в заштрихованной зоне (фиг, 5). В течение второго такта кодированию подлежит величина, равная 36-32 (32 мкА - это уровень настройки опорного компаратора 10). Таким образом, на счетчик 14 от гене ратора 13 должно поступить к моменту опрокидывания опорного компара- тора 10 N 37-32 5 импульсов, т.е. код младших разрядов будет 101. Следовательно, выходной код будет 1 10101 53 .

Пусть теперь в результате воздействия дестабилизирующего фактора уровни срабатьшания фазовых компараторов в блоке 7 сместились, например вверх относительно своих номинальных значений на величину .MKA (см. графу п| таблицы) а величина преобразуемого сигнала.при этом осталась равной Ту;, 53 мкА. В этом случае в блоке 7 срабатывают не шесть, а лишь пять младших компараторов (шестой .компаратор не срабатывает, поскольку новый уровень его срабатьшания стал равным 54 , ). Поэтому код трех старших разрядов будет 101. Компенсирующий ток Т) , генерируемый блоком 5, в этом случае должен быть равным одной дискретности блока 7, т.е. 8 мкА, так что в момент окончания компенсации величина I , должна быть равна мкА. В течение второго такта кодированию подлежит величина, равная 45-32 13 мкА. Как видим, она превьшгает величину дискретности грубой ступени преобразования (величину дискретности блока 7) , а значит, и емкость трехразрядного счетчика 14, на который должно постзттить 13 импульсов.

Упомянутая погрешность за счет того, что остаток входного сигнала, подлежащий кодированию в течение второго такта, превьш ает дискретность блока 7, а значит, превьш1ает и емкость счетчика 14, устраняется введением связи по цепи переноса между счетчиками 9 и 14. Действительно, трехразрядный счетчик 14.после окончания подсчета 13-ти импульсов находится в состоянии 101 и дает импульс переноса (после 7-го импульса) в счетчик 9, так что код старших разря-.

10

20

25

1102812

ДОН будет скорректирован и равен 101+1 (перенос)110, а результирующий выходной код будет 110 101 53 .

5 При смещении уровней срабатьшания фазовых компараторов в блоке 7 вниз относительно их номинальной настройки устройство работает аналогично. Итак, в преобразователе окончательный результат получается правильным после коррекции, однако на это уходит значительно меньше времени, чем в известных преобразователях.

ij

t5 Фор мула изобретения

1. Адаптивньш аналого-цифровой преобразователь, содержащий генератор опорного напряжения, выход которого подключен к опорному входу рабочего фазовращателя и входу фазовращателя смещения непосредс венно, а через первый и второй опорные фазовращатели - к первым входам первого и второго опорных компараторов соответственно, выходы которых соединены с соответствующими опорными входами логического блока, первый выход которого соединен с первьм управляющим входом первого счетчика, выход которого соединен с выходной шиной, информационный вход рабочего фазовращателя является входом преобра.зова- .теля, первьй и второй компенсационные входы рабочего фазовращателя подключены к выходам первого и второго блоков компенсирующего тока соответственно, выход рабочего фазовращателя подключен к первому входу блока фазовых компараторов, выход которого подключен к информационному входу шифратора, выход которого соединен с первым информационным входом первого Счетчика, блок управления, первый выход которого подключен к управляющему входу шифратора, второй выход - к .второму управляющему входу первого счетчика, отличающий- с я тем, что, с целью увеличения быстродействия преобразователя, в него введены второй счетчик, размыкающий контакт двухполюсного выключателя

30

35

40

45

50

Пуск , токоограничивающий элемент, генератор импульсов и блок адаптации, первый вход которого соединен с первыми входами блока управления первого и второго блоков компенсирующего тока, с вторым входом блока фазовых компараторов и подключен к второму

13i 3

выходу логического блока, второй вход блока адаптации соединен с перВЕ)1М управляющим входом логического блока с вторыми входами первого и второго блоков компенсирующего тока и подключен к третьему выходу блока управления, третий вход блока адаптации соединен с третьими входами первого и второго блоков компенсирзтощего тока и подключен к выходу первого счетчика, первый и второй выходы блока адаптации подключены к второму и .третьему управляющим входам логического блока соответственно, третий вьпсод которого соединен с входом генератора импульсов, выход которого подключен к счетному входу второго счетчика, первый управляющий вход которого подключен к четвертому выходу блока управления, пятый выход которого подключен к второму управляющему входу второго счетчика и второму информационному входу первого счетчика, третий информационный вход которого соединен с выходом переноса второго счетчика, третий управляющий вход которого подключен к второму выходу блока управления, а четвертый управляющий Ёход подключен к первому выходу логического блока, выход фазовра- щат«шя смещения подключен к третьему входу блока фазовых компараторов, четвертый вход которого подключен к шестому выходу блока управления,, второй вход которого через размыкающий контакт двухполюсного выключателя Пуск подключен к общей шине и через токоограничивающий элемент - к питания, вторые входы первого и второго опорных компараторов подключены к выходу рабочего фазовращателя, выход второго счетчика соединерг с выходной шиной.

2. Преобразователь по п 1, отличающийся тем, что блок адаптации содержит инвертор, триггер, генератор импульсов, счетчик первый

И второй дешифраторы, с первого по пятнадцатый элементы ИЛИ и первый, второй элементы И-НЕ, вход инвертора является первым входом блока.адаптации, выход инвертора подключен к S-входу триггера, R-вход которого является вторым , в ходом блока адаптации

.и соединен с установочным входом счетчика, выход триггера соединен с входом генератора импульсов, выход, которого подключен к информационному

входу счетчика, выход которого соединен с входом первого дешифратора, вход второго дешифратора является третьим входом блока адаптации, выходы первого дешифратора подключены к первым входам соответствующих элементов ИШИ, к вторым входам которых подключены выходы второго дешифратора, выходы с первого по восьмой элементов ИЛИ соединены с входами первого элемента , выходы с девятого по пятнадцатый элементов ИЛИ подключены к входам второго элемента И-НЕ, выходы первого и второго элементов И-НЕ

являются первым и вторым выходами блока адапта,ции соответственно.

3-. Преобразователь по п. 1 j о т - личающийся тем, -что. блокуправления содержит первый и второй формирователи импульсов, элемент ИЛИ, первый и второй инверторы, первьм, второй и третий триггеры, генератор Ш пульсов, счетчик, дешифратор и замыкающий контакт двухполюсного выключателя первьш вход элемента ИЖ является первым входом блока управления, второй вход элемента ИПИ подключен к выходу первого формирователя импульсов, выход элемента И,ПИ подключен к R-входам первого, второго и третьего триггеров и установочному входу счетчика непосредственно, а через последовательно соединенные первый инвертор и второй формирователь рпмпульсов - к S-входу третьего триггера5 выход которого соединен с входом генератора импульсов, выход которого подключен к информационному входу счетчика, выход которого подключен к входу дешифратора, первьш выход которого является щес- тьв-1 выходом , блока управления, второй выход дешифратора подключен к S-вхоДУ второго триггера, выход которого является пер)вым выходом блока управления, третий выход дешифратора подключен к S-входу первого триггера, вьгход которого является вторым выходом блока уг(равления5 четвертый выход дешифратора, является третьим выходом блока управления, D- и С-входы триггеров объединены и соединены с общей ШИ.НОЙ5 одна клемма замыкающего

контакта двухполюсного выключателя Пуск, является вторым входом блока управления и подк,гаочена к входу первого формирователя, а другой соединена с обш.ей шиной и является четвертым

15131102816

выходом блока управления, который выход которого является пятым выхо- соединен с входом второго инвертора,. дом блока управления.

вьи.б вых1 бы/г выаз ам. вых.з Sft

лг

Лш1 Аж/

6i.t м ла

цма-З

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное кодирующее устройство | 1983 |

|

SU1166308A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297225A1 |

| Быстродействующий аналого-цифровой преобразователь | 1985 |

|

SU1254584A1 |

| Адаптивный аналого-цифровой преобразователь | 1988 |

|

SU1531222A2 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Аналого-цифровой преобразователь с автокоррекцией погрешности (его варианты) | 1983 |

|

SU1144189A1 |

| Аналого-цифровой преобразователь с автокоррекцией погрешности | 1983 |

|

SU1091337A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884121A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1095393A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU732955A1 |

Изобретение относится к измерительной и вычислительной технике и может быть использовано в аналого- цифровых преобразователях. Целью изобретения является увеличение быстродействия преобразователя. Адаптивный аналого-цифровой преобразователь содержит генератор 1 опорного напряжения, опорные фазовращатели 2, 3, вход /7 (Л /у И фиг л

| Измерительная техника, 1972, 5 11, с | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-05-15—Публикация

1986-02-06—Подача