I

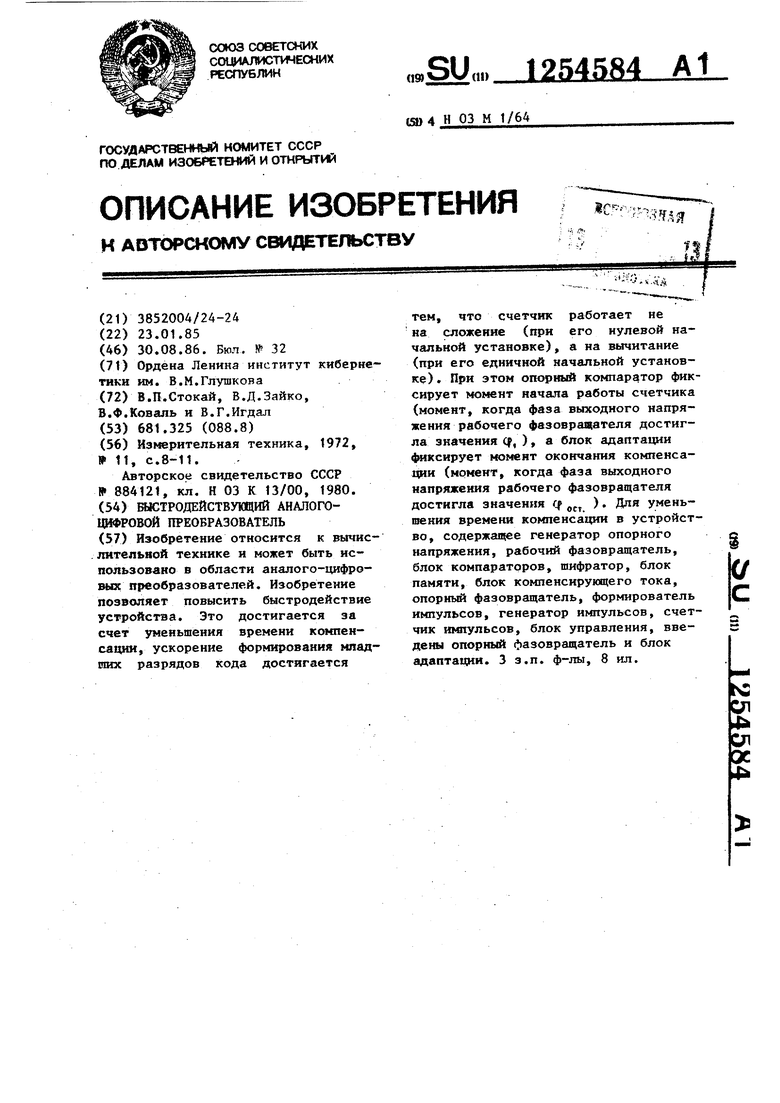

Изобретение относится к вычислительной технике и может быть использовано в области аналого-цифровых преобразователей.

Цель изобретения - повышение быст- 5 родействия.

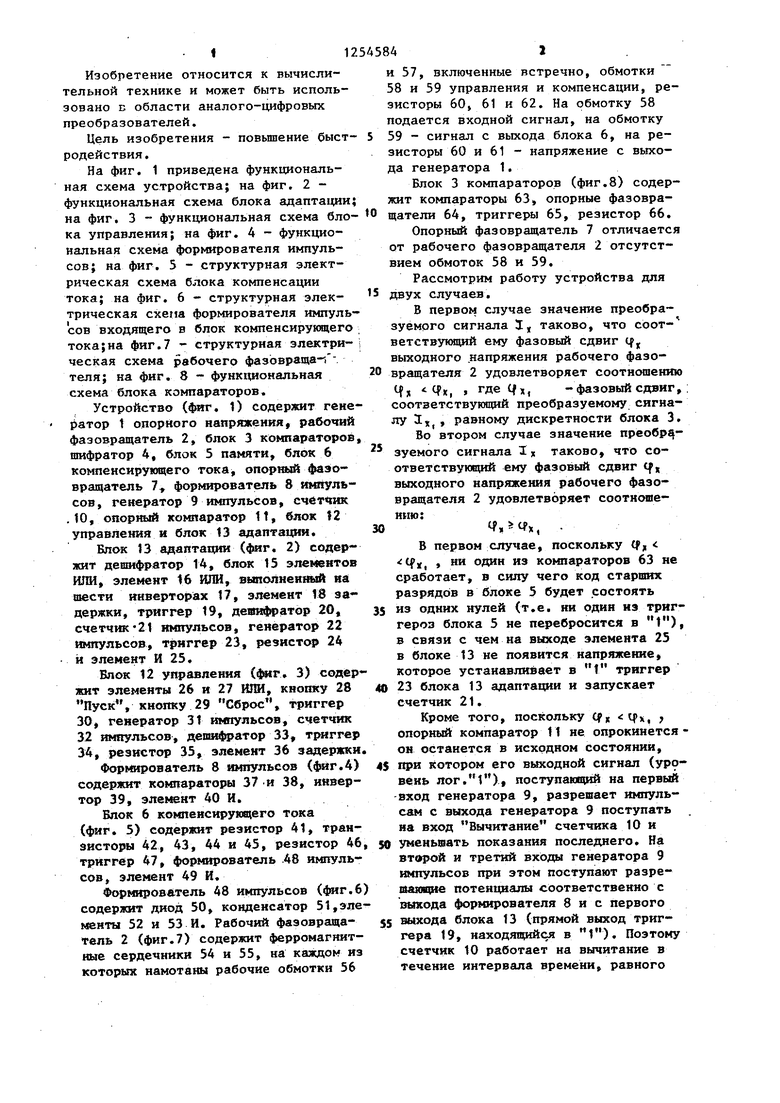

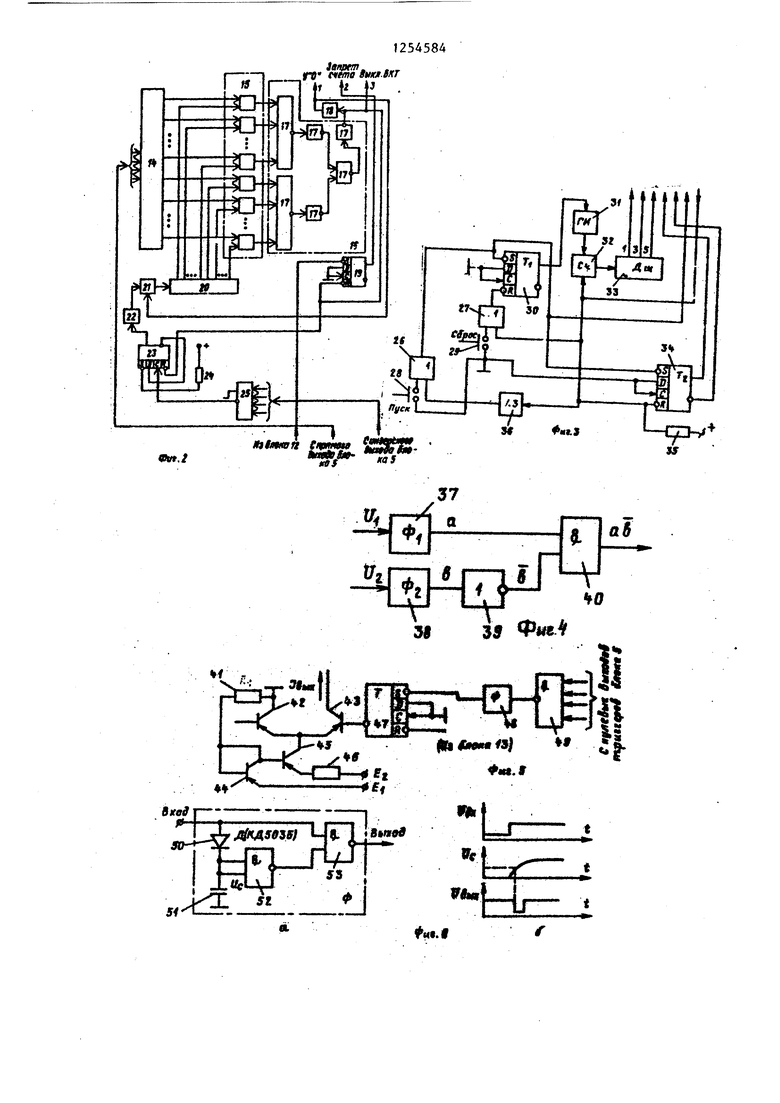

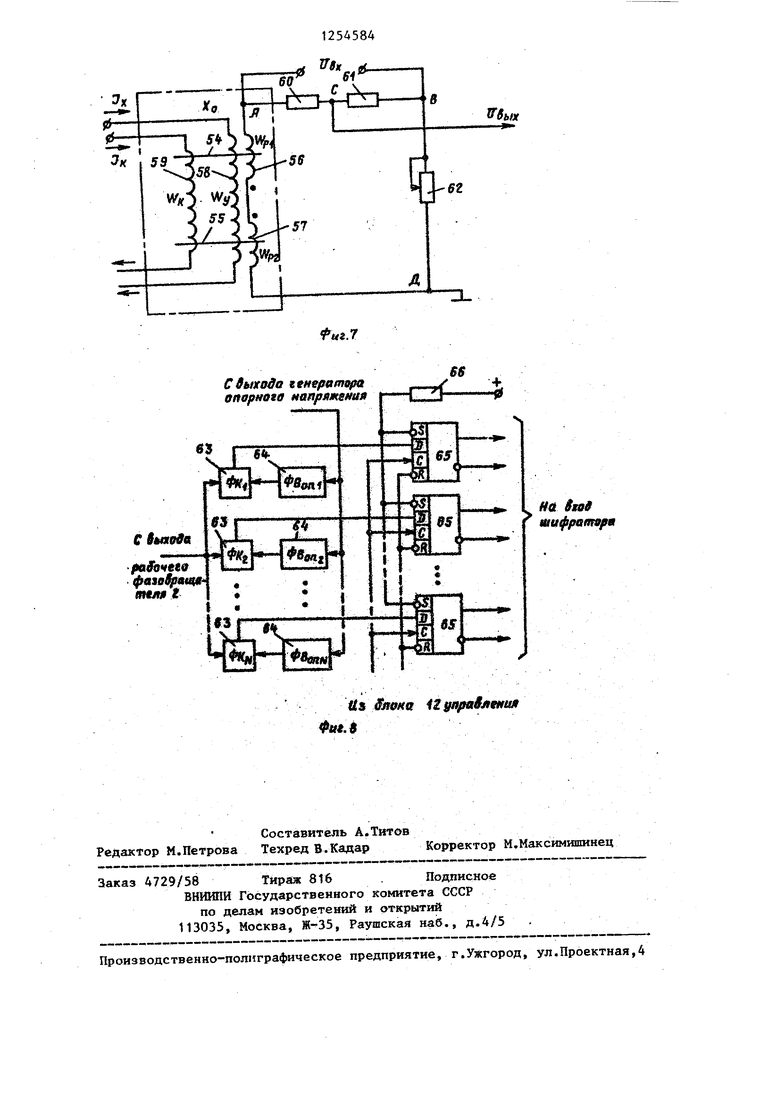

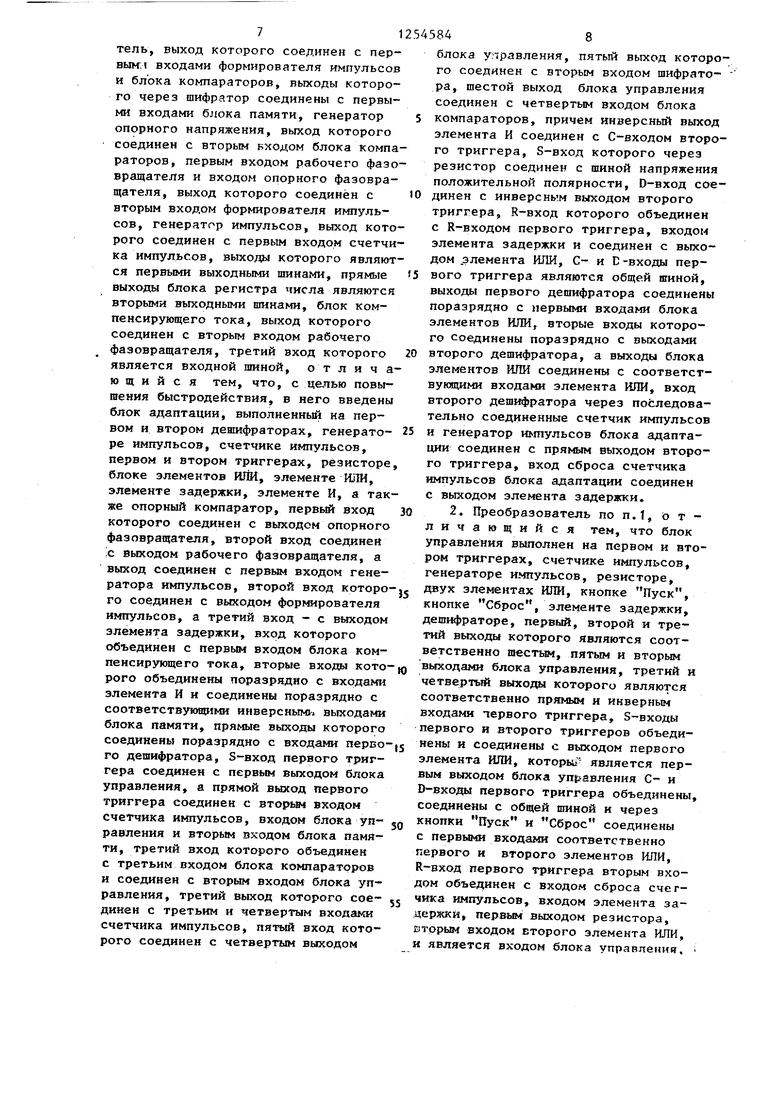

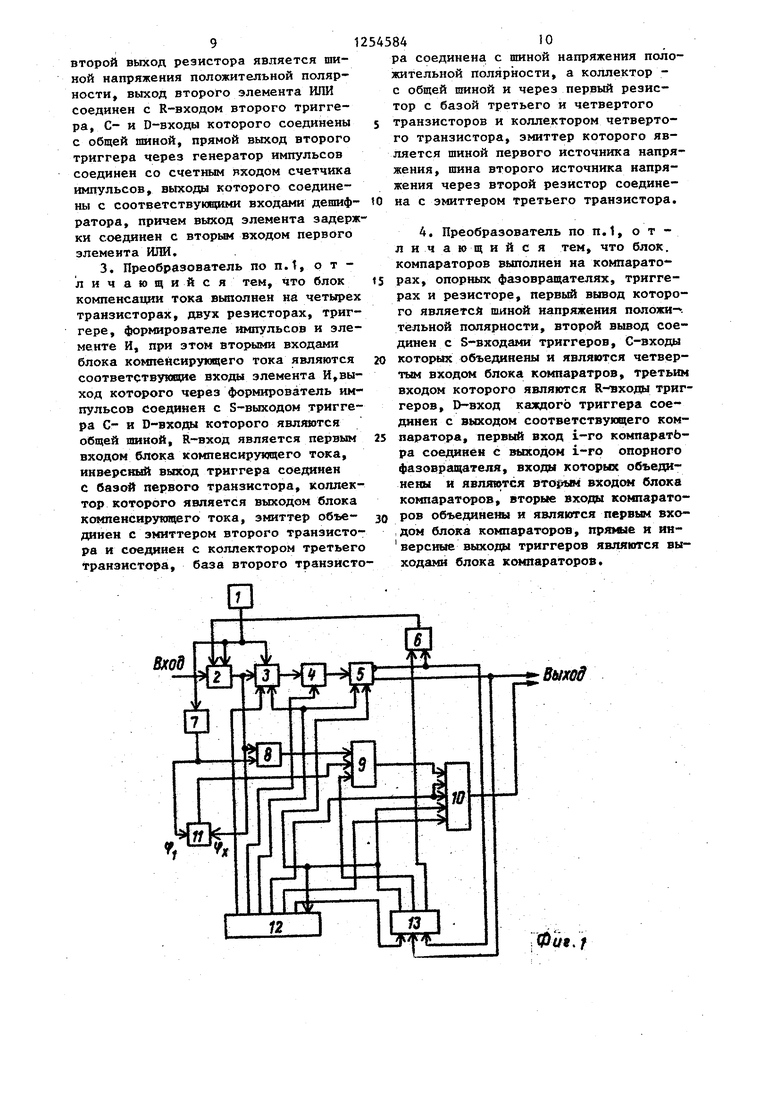

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема блока адаптации;

125А58А2

и 57, включенные встречно, обмотки

58и 39 управления и компенсации, резисторы 60, 61 и 62. На обмотку 58 подается входной сигнал, на обмотку

59- сигнал с выхода блока 6, на резисторы 60 и 61 - напряжение с выхода генератора 1.

Блок 3 компараторов (фиг.8) содержит компараторы 63, опорные фазоврана фиг, 3 - функциональная схема бло- щатели 64, триггеры 65, резистор 66.

ка управления; на фиг. 4 - функциональная схема формирователя импульсов; на фиг. 5 - структурная электрическая схема блока компенсации тока; на фиг. 6 - структурная электрическая схема формирователя импульсов входящего в блок компенсирующего тока;на фиг.7 - структурная электри-1 ческая схема рабочего фазовраща-Г- теля; на фиг. 8 - функциональная схема блока компараторов.

Устройство (фиг, 1) содержит генератор 1 опорного напряжения, рабочий фазовращатель 2, блок 3 компараторов, шифратор 4, блок 5 памяти блок 6 компенсирующего тока, опорный фазовращатель 7, формирователь 8 импульсов , генератор 9 импульсов, .to, опорный компаратор It, блок 12 управлет{я и блок 13 адаптации.

Блок 13 адаптации (фиг. 2) содержит дешифратор 14, блок 15 элементов ИЛИ, элемент 16 ШШ, выполненнь иа шести инверторах 17, элемент 18 задержки, триггер 19, дешв фатор 20, счетчик 21 импульсов, генератор 22 импульсов, триггер 23, резистор 24 и элемент И 25.

Блок 12 управления (г. 3) содержит элементы 26 и 27 ИЛИ, кнопку 28 Пуск, кнопку 29 Сброс, триггер 30, геиератор 31 шв1ульсов, счетчик 32 датульсов, деши4фатор 33, триггер 34, резистор 35, элемент 36 задержки.

Фарьв1рователь В импульсов (фиг.4) содержит компараторы 37 и 38, инвертор 39, элеьшнт 40 И.

Елок 6 компеисируищего тока (фиг. 5) содержит резистор 41, транзисторы 42, 43, 44 и 45, резистор 46, триггер 47, формирователь 48 импульсов, 49 И,

Формяровлтель 48 импульсов (фиг.6) содержит диод 50, конденсатор 51,эле- №нты 52 и 53 И. Рабочий фазовращатель 2 (фиг.7) содержит ферромагнитные сердечники 54 и 55, на каждом из которых намотаны рабочие обмотки 56

- 5

;

125А58А2

и 57, включенные встречно, обмотки

58и 39 управления и компенсации, резисторы 60, 61 и 62. На обмотку 58 подается входной сигнал, на обмотку

59- сигнал с выхода блока 6, на резисторы 60 и 61 - напряжение с выхода генератора 1.

Блок 3 компараторов (фиг.8) содержит компараторы 63, опорные фазовра- щатели 64, триггеры 65, резистор 66.

Опорный фазовращатель 7 отличается от рабочего фазовращателя 2 отсутствием обмоток 58 и 59.

Рассмотрим работу устройства для двух случаев.

В первом случае значение преобразуемого сигнала 1, таково, что соот- ветствующий ему фазовый сдвиг ц выходного напряжения рабочего фазо- 0 вращателя 2 удовлетворяет соотнснпеиию Чх tfx, . где Ч„, - фазовый сдвиг, : соответствующий преобразуемому сигналу 1, , равному дискретности блока 3. Во втором случае значение преобр - зуемого сигнала Iц таково, что соответствующий ему фазовый сдвиг Cf выходного напряжения рабочего фазовращателя 2 удовлетворяет соотношению:0.х,

В первом случае, поскольку Cf, , и один из компараторов 63 не сработает, в силу чего код старших разрядов в блоке 5 будет состоять 5 из одних нулей (т.е. ни один из триггеров блока 5 не перебросится в 1), в связи с чем на выходе элемента 25 в блоке 13 не появится напряжение, которое устанавливает в 1 триггер 0 23 блока 13 адаптации и запускает счетчик 21.

Кроме того, поскольку Cfn , у опорный компаратор 11 не опрокинется - он останется в исходном состоянии, $ при котором его выходной сигнал (уровень лог.1), поступающий на первый -вход генератора 9, разрешает импульсам с выхода генератора 9 поступать на вход Вычитание счетчика 1О и 50 уменьшать показания последнего. На второй и третий входы генератора 9 импульсов при этом поступают разрешающие потенциалы соответственно с выхода формирователя 8 и с первого 55 выхода блока 13 (прямой выход триггера 19, находящийся в 1). Поэтому счетчик 10 работает на вычитание в течение интервала времени, равного

длительности импульса на выходе формирователя 8 (длительность этого импульса пропорциональна величине Уу.-фх ) .По окончании преобразования в счетчике 10 будет зафиксиро- s ван код младших разрядов цифрового

эквивалента входного сигнала 3.

Во втором случае опорный компара- тор 11 опрокидывается, на его выходе устанавливается сигнал лог,О, за- О прещакщий импульсам с выхода генератора 9 поступать на счетчик 10, Одновременно в блоке 3 сработает соответствующее величине ( количество компараторов 63, в результате чего 5

на выходе блока 3 будет сформирован единичный (унитарный) код, который по соответствукяцим командам блока 12 сначала будет преобразован в двоичный код (при помощи шифратора 4), а 20 затем записан в блок 5, Так в течение первого такта преобразования происходит формирование старших разрядов цифрового эквивалента входного сигнала 1,,

Поскольку код сформированных в течение первого такта старших разрядов может c дepжaть единицу, на инверсном выходе блока 5 появится отрицательный перепад напряжения (из 30 лрг. Ч в лог,О), котор включит |блок 6, при этом в нем сигнал.с выхода формирователя 48 установит триг- гер 47 в 1, благодаря чему ток от источника, собранного на транзисто- 35 pax 44 и 45 -.ерез транзистор 43 поступит в обмотку 59 рабочего фазовращателя .2, и начнется процесс компенсации, в течение которого фаза выходного напряжения рабочего фазовра- 40 щателя 2 сдвигается в направлении, противоположном тому, в котором она сдвигалась под воздействием входного сигнала 1, Затем включится блок 13 и на выходе элемента 25 появится пе- 45 репад напряжения (из лог,О в лог,1), который установит триггер 23 в 1, при этом импульсы генератора 22 начнут подсчитываться счет25

чиком 22, Дешифратор 20 выделяет из 50 °f блока 13 адаптации кода старших

разрядов разрешающий потенциал (уропоследовательности этих импульсов соответствующие имяульсыв соответствии с необходимым временемксжпенсащш.; Ъдновремейно на второй вход бловень лог,О) будет только на одном из выходов дешифратора 14, а значит и на первом входе только одного элека 13 адаптации с прямого выхода

ка 5 поступает сформированный в течение первого такта код старших разрядов цифрового эквивалента преобра

s

О 5

20

30 354045

254584

зуемого сигнала 3

25

(на фиг, 2 этот сигнал поступает на вход дешифратора 14), В зависимости от поступающего на дешифратор 14 кода разреша сяций потенциал появится на одном из выходов дешифратора 14, Функциональная схема блока 13 адаптации приведена для случая, когда в течение первого такта преобразования происходит определение четырех старших разрядов выходного тока. В таком случае в зависимости от кода полученных в течение первого такта преобразования че- тьфех разрядов разрешающий потенциал будет на соответствующем выходе дешифратора 14, а значит и на первом входе соответствующего элемента ИЛИ блока 15,

На вторые входы элементов ИЛИ блока 15 поступают сигналы с выходов дешифратора 20,

Таким , чем больший код старятх разрядов, тем больший номер lOfeeT элемент ИЛИ, на первый вход которого поступает разрешакиций сигнал с ВЫХОДА дешифратора 14, и тем позднее появятся сигналы на выходах блока t3.

Таким образом блок 13 адаптации 4мксирует момент окончания компенсации (этот м(жеит наступает тем раньше, чем меньше величина входного преобразуемого сигнала 1,

Блок 13 работает следуюпщм образом.

При нажатии кнопки Пуск в блоке 12 управления на его первом выходе появляется сигнал лог,О, который, поступая на третий вход блока 13, устанавливает в 1 триггер 19, сигнал с прямого выхода которого разрешает поступление импульсов с генератора 9 импульсов на счетный вход счетчика 10,

На второй вход блока 13 с прямого выхода блока 5 поступает ког старших разрядов, сфорюсрованный в течение первого такта преобразования, В зависимости от поступившего на второй

вень лог,О) будет только на одном из выходов дешифратора 14, а значит и на первом входе только одного элемента ИШ блока 15,

При поступлении на первые входы блока 13 с ииверсного выхода блока 5 кода, содержащего хотя бы одну единицу, происходит установка в единицу триггера 23, сигнал с прямого выхода которого включает генератор 22 импульсов, импульсы которого поступают на счетчик 21. Деншфратор 20 вьзде- ляет из последовательности поступающих на счетчик 21 импульсов генератора 22 соответствуклцие импульсы, которые поступают на вторые входы блока 15. Следовательно, на втором выходе блока 13 появится один из импульсов генератора 22 (этот импульс свидетельствует об окончании процесса компенсации).

Таким образом, чем больший код поступает на второй вход блока 13 (на вход дешифратора 14), тем позднее появится импульс на втором выходе блока 13, фиксирующий момент окончания компенсации. Этот импульс устанавливает в О триггеры 19 и 23 и в блоке 13 адаптации н выключает блок 6,

Чем больше величина входного (преФормирователь 8 содержит кёютара- трры 37 и 38, преобразукмцие выходные

образуемого) сигнала и чем больше код 25 сигналы рабочего 2 и опорного 7 фастарших разрядов, тем большая величина компенсирующего тока необходима для осуществления компенсации, тем большее время необходимо для того, чтобы требуемое значение компенсиру- ющего тока установилось с требуемой точностью в обмотке 59 рабочего фазовращателя 2 и тем позднее появится импульс на втором выходе блока 13 адаптации.

Импульс с вькода элементов ИЛИ блока 15 устанавливает в О триггеры 19 и 23, пройдя элемент 18, подготавливает блоки устройства к HOBOif-iy

циклу работы: в блоке 13 устанавлива-ед (с требуемой точностью) будет достигет в О счетчик 22j а также выполняет начальные установки в блоках 5,125 счетчике 10 в блоках 3 и 12 осуществляет нулевь1е установки, а счетчик 10 - устанавливает в начальное состояние. 45

Блок 12 работает следующим обра зом.

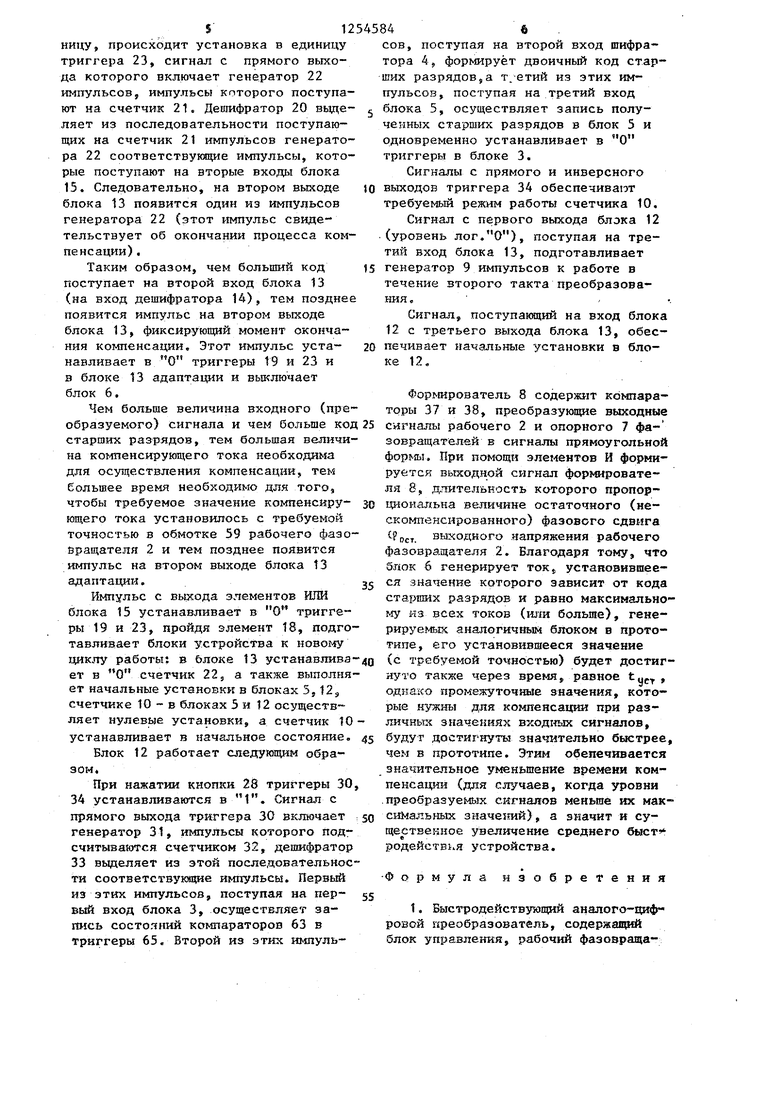

При нажатии кнопки 28 триггеры 30, 34 устанавливаются в 1. Сигнал с прямого выхода триггера 30 включает :sO генератор 31, stMnyjtbCM которого подсчитываются счетчиком 32, дешифратор 33 выделяет из этой последовательности соответствукедие импульсы. Первый из этих импульсов, поступая на пер- 55 вый вход блока 3, осуществляет запись состояний компараторов 63 в триггеры 65. Второй из этих импульсов, поступая на второй вход шифратора 4, формирует двоичный код старших разрядов5 а т.-етий из этих импульсов, поступая на третий вход

5 блока 5, осуществляет запись полученных старших разрядов в блок 5 и одновременно устанавливает в О триггеры в блоке 3.

Сигналы с прямого и инверсного

JO выходов триггера 34 обеспечивапт требуемьй режим работы счетчика 10. Сигнал с первого выхода блока 12 (уровень лог.О), поступая на третий вход блока 13, подготавливает

15 генератор 9 импульсов к работе в течение второго такта преобразования,

Сигнал, поступающий на вход блока 12 с третьего выхода блока 13, обес20 печивает начальные установки в блоке 12,

Формирователь 8 содержит кёютара- трры 37 и 38, преобразукмцие выходные

25 сигналы рабочего 2 и опорного 7 фазовращателей в сигналы прямоугольной формы. При помощи элементов И формируется выходной сигнал фop a poвaтe- ля 8,, длительность которого пропорциональна величине остаточного (нескомпенсированного) фазового сдвига tfp(, выходного напряжения рабочего фазовращателя 2. Благодаря тому, что блок б генерирует ток установившееся значение которого зависит от кода старших разрядов и равно максимальному из всех токов (шга больше), генерируемых аналогичным блоком в прототипе, его установившееся значение

нуто также через время, равное ty , однако промежуточные значения, которые кужтл для компенсации при различных значекиях входных сигналов, будут достигнуты значительно быстрее чем в прототипе. Этим обепечивается значительное уменьшение времени компенсации (для случаев, когда уровни преобразуемых сигналов меньше их максимальных значе5шй), а значит и существенное увеличение среднего быст родействкя устройства.

Формула изобретения

1. Быстродействуищий аналого-цифровой преобразователь, содержаарй блок управления, рабочий фазовращатель, выход которого соединен с пер- ВЫМ.1 входами формирователя импульсов и блока кo mapaтopoв, выходы которого через шифратор соединены с первыми входами блока памяти, генератор опорного напряжения, выход которого соединен с вторым входом блока компараторов, первым входом рабочего фазовращателя и входом опорного фазовращателя, выход которого соединён с вторым входом формирователя к тулъ- сов, генератор импульсов, выход которого соединен с первым входом счетчика импульсов, выходы которого являются первыми выходными шинами, прямые выходы блока регистра числа являются вторыми выходными шинами, блок компенсирующего тока, выход которого соединен с вторым входом рабочего фазовращателя, третий вход которого является входной шиной, о т л и ч а- ю щ и и с я тем, что, с целью повы- гаения быстродействия, в него введены блок адаптации, выполненнь на первом и втором дешифраторах, генерато- ре импульсов, счетчике импульсов, первом и втором триггерах, резисторе, блоке элементов ИЛИ, элементе ИЛИ, элементе задержки, элементе И, а также опорный компаратор, первый вход которого соединен с выходом опорного фазовращателя, второй вход соединен |с выходом рабочего фазовращателя, а выход соединен с первю входом генератора импульсов, второй вход KOTOpO

го соединен с выходом форретрователя импульсов, а третий вход - с выходом элемента задержки, вход которого объединен с первым входом блока компенсирующего тока, вторые входы кото рого объединены поразрядно с входами элемента И и соединены поразрядно с соответствующими инверсньпФ выходами блока памяти, прямые выходы которого соединены поразрядно с вxoдa m перБо го дешифратора, S-вход первого триггера соединен с первым выходом блока управления, а прямой выход первого триггера соединен с вторьм входом сче-гчика импульсов, входом блока уп- равленИя и вторым входом блока памяти, третий вход которого объединен с третьим входом блока компараторов и соединен с вторым входом блока управления, третий выход которого сое- динен с третьим и четвертым входами счетчика импульсов, пятый вход которого соединен с четвертым выходом

блока управления, пятый выход которго соединен с вторым входом шифрато ра, шестой выход блока управления соединен с четвертым входом блока компараторов, причем инверсный выхо элемента И соединен с С-входом вторго триггера, S-вход которого через резистор соединен с шиной напряжени положительной полярности, D-вход содинен с инверсным выходом второго триггера, R-вход которого объединен с R-входом первого триггера, входом элемента задержки и соединен с выходом элемента ИЛИ, С- и D-входы первого триггера являются общей шиной, выходы первого дешифратора соединены поразрядно с первыми входами блока элементов ИЛИ, вторые входы которого соединены поразрядно с выходами второго дешифратора, а выходы блока элементов ИЛИ соединены с соответствующими входами элемента ИЛИ, вход второго дешифратора через последовательно соединенные счетчик импульсов и генератор ш тульсов блока адаптации соединен с прямым выходом второго триггера, вход сброса счетчика импульсов блока адаптации соединен с выходом элемента задержки.

2. Преобразователь по п.1, о т - личающийся тем, что блок управления выполнен на первом и втором триггерах, счетчике импульсов, генераторе импульсов, резисторе, двух элементах ИЛИ, кнопке Пуск, кнопке Сброс, элементе задержки, дешифраторе, первый, второй и третий выходы которого являются соответственно шестым, пятым и вторым выходами блока управления, третий и четверть выходы которого являются соответственно прямым и инверным входами epвoгo триггера, S-входы первого и второго триггеров объединены и соединены с выходом первого элемента ИЛИ, которьи - является первым выходом блока уп|гавления С- и D-входы первого триггера объединены, соединены с общей шиной и через кнопки Пуск и Сброс соединены с первыми входами соответственно первого и второго элементов ИЛИ, Е-8ход первого триггера вторым входом объединен с входом сброса счег- чика импульсов, входом элемента задержки, первым выходом резистора, вторым входом второго элемента ИЛИ, и является входом блока управления,

второй выход резистора является шиной напряжения положительной полярности, выход второго элемента ИЛИ соединен с R-входом второго триггера, С- и D-входы которого соединены с общей шиной, прямой выход второго триггера через генератор импульсов соединен со счетным входом счетчика импульсов, выходы которого соедине ны с соответствующими входами дешиф- ратора, причем выход элемента задержки соединен с вторю входом первого элемента ИЛИ.

3. Преобразователь по пЛ, о т - л и ч а ю щ и и с я тем. Что блок компенсации тока выполнен на четырех транзисторах, двух резисторах, триггере, формирователе импульсов и элементе И, при этом вторьми входами блока компенсирующего тока являются соответствуювще входы элемента И,вы- ход которого через формирователь импульсов соединен с S-выходом триггера С- и D-входы которого являются общей шиной, И-вход является первым входом блока компенсирующего тока, инверсный выход триггера соединен с базой первого транзистора, коллектор которого является выходом блока компенсирующего тока, эмиттер объе- динен с эмиттером второго транзистора и соединен с коллектором третьего транзистора, база второго транэисто1254584

10

ра соединена, с шиной напряжения положительной полярности, а коллектор - с общей шиной и через первый резистор с базой третьего и четвертого транзисторов и коллектором четвертого транзистора, эмиттер которого является шиной первого источника напряжения, шина второго источника напряжения через второй резистор соединена с эмиттером третьего транзистора.

4. Преобразователь по п.1, от - ли чающий с я тем, что блок, компараторов выполнен на компараторах, опорных фазовращателях, триггерах и резисторе, первый вывод которого являетсй шиной напряжения положи, тельной полярности, второй вывод соединен с S-входами триггеров, С-входы которых объединены и являются четвер- чъм входом блока компаратров, третьим входом которого являются R-входы триггеров, D-вход каждого триггера соединен с выходом соответствующего компаратора, первый вход i-ro компаратб- ра coejD инён с выходом i-ro опорного фазоЕ1ращателя, входы которых объединены и являются вторгым входом блока компараторов, вторые входы компараторов объединежл и являются первым вхо- ,дом блока компараторов, прямые и инверсные выходы триггеров являются выходами блока компараторов.

Вход

П п г

- .

1 « I

- BbtxoS

re ntma ttua.tKT

9m,г

3S

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный аналого-цифровой преобразователь | 1986 |

|

SU1311028A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297225A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Адаптивное кодирующее устройство | 1983 |

|

SU1166308A1 |

| Преобразователь угла поворота вала в код | 1980 |

|

SU942095A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Аналого-цифровой преобразователь с автокоррекцией погрешности (его варианты) | 1983 |

|

SU1144189A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Преобразователь перемещений в код | 1983 |

|

SU1111188A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1506460A1 |

Изобретение относится к вычислительной технике и может быть использовано в области аналого-цифровых преобразователей. Изобретение позволяет повысить быстродействие устройства. Это достигается за счет уменьшения времени компенсации, ускорение формирования младших разрядов кода достигается тем, что счетчик работает не на сложение (при его нулевой начальной установке), а на вычитание (при его едничной начальной установке). При этом опорный компаратор фиксирует момент начала работы счетчика (момент, когда фаза выходного напряжения рабочего фазовращателя достигла значения (f, ), а блок адаптации фиксирует момент окончания компенса- оди (момент, когда фаза выходного напряжения рабочего фазовращателя достигла значения q ). Для уменьшения времени компенсации в устройство, содержащее генератор опорного напряжения, рабочий фазовращатель, блок компараторов, шифратор, блок памяти, блок компенсирующего тока, опорньё) фазовращатель, формирователь и myльcoв, генератор импульсов, счетчик шшульсов, блок управления, введешь опорный фазовращатель и блок адаптации. 3 з.п. ф-лы, 8 ил. (/ С ел . ел

35 Фие

«

. $. I

-41

ffS

1

Bt 1ГА«

Э:

;0 ..

УК

bfX

Us ffa&Hti 12 уо/ю9лв1Ю/1 ,в

Ни tmS

| Измерительная техника, 1972, 11, с.8-11 | |||

| Аналого-цифровой преобразователь | 1980 |

|

SU884121A1 |

Авторы

Даты

1986-08-30—Публикация

1985-01-23—Подача