ел

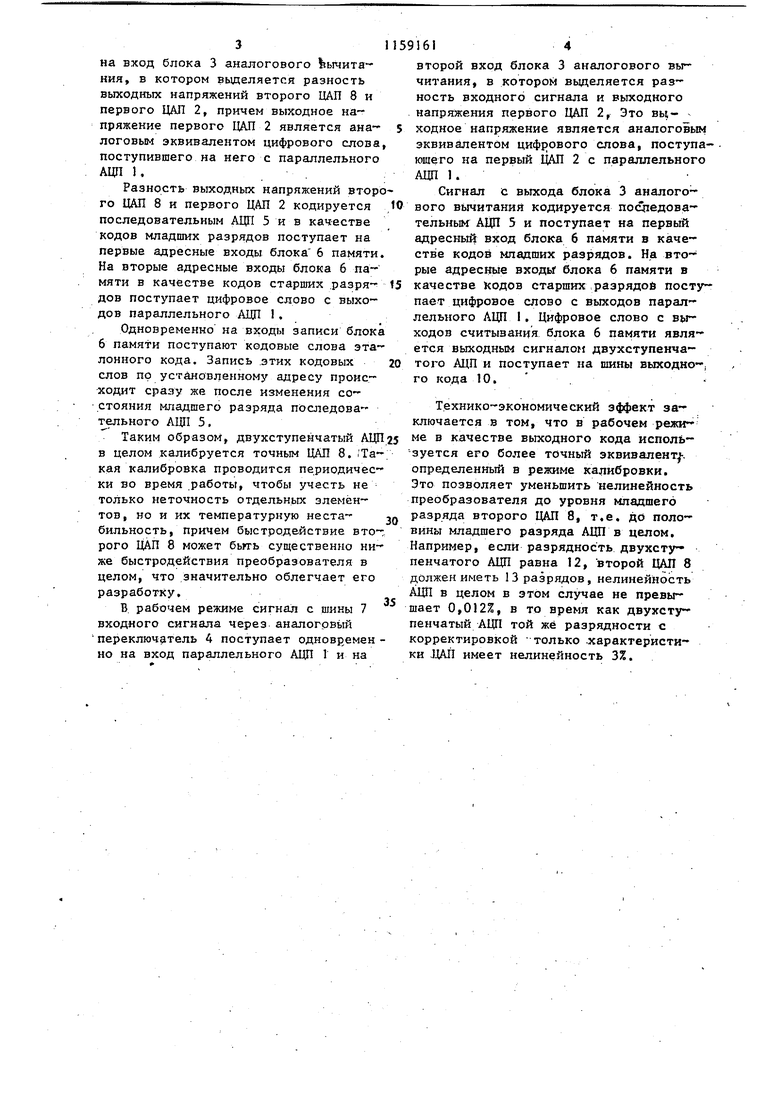

со 111 Изобретение относится к анапого цифровым преобразователям и может быть использовано в технике физичес кого эксперимента, в частности в яде ной электронике, а также в вычисли-. тельной технике, гидролокации, радио локации и технике связи. Известно устройство аналого-цифр.о вого преобразования, содержащее два параллельных аналого-цифровых преоб разователя (АЮТ), цифрйаналоговый пр образователь (UAITI и блок аналогового вычитания 03 Недостаток; такого устройства малая точность преобразования, Наиболее близким по технической сущности к предлагаемому является двухступенчатьй аналого-цифровой преобразователь, содержащий параллельный АЦП, блок аналогового вычи- тания, последовательный АДП, коммутатор, бдок памяти и сумматор,выход которого соединены с выходной шиной, первые входы с выходом блока памят а вторые входы :- с выходами последонательного АЦП и первыми входами блока памяти, вторые входы которого соединены с первыми выходами коммута тора, вторые выходы которого соедине ны с первыми входами цифроаналоговог коммутатора и первым входом последовательного АЩ1| второй в.ход которого соединен -с выходом аналогового вычитателя, первый вход которого соедине с входной шиной и входом параллельного АЩ1,а второй вход -с выходом ДАЛ, . входы которого соединены с вы ходами параллельного АЦП и первыми входами коммутатора , вторые входы ко торого соединены с шинами эталонного кода 2J. Недостаток этого устройства - невысокая точность коррекции погрешностей двухступенчатого АЦП в целом. так как коррекции подвергаются тольк погрешности ЦАП, Погрешности параллельного АЦП, блока аналогового вычнтания -и последовательного АЦП в этом устройстве не могут быть скорректированы и проявляются на выходе устройства. Целью изобретения является повышение точности преобразования. Поставленная цель достигается тем что в двухступенчатый аналого-цифровой преобразователь,содержащий параллельный АЦП, выходы которого через пер- вьШ иди соединены с первым входом блока 12 аналогового вычитания ,второй вход которого подключен к входу параллельного АЦП, а выход - к входу последовательного АЦП, выходы которого соединены с первыми адресными входами блока памяти, введены аналоговый переключатель и второй ДАЛ, входы которого подключены к шинам эталонного кода и входам записи блока памяти, а выход - к первому входу аналогового переключателя, второй вход которого соединен с шиной входного сигнала, а выход - с входом параллельного АШ, при этом вторые адресные входы блока памяти подключены к выходам параллельного ДЦП, а выходы - к шинам выходного кода. На черте)ке представлена функциональная схема двухступенчатого АЦП. Устройство содержит параллельный АЦП 1, первый 1ДАП 2, блок 3 аналогового вычитания, аналоговый переключатель 4, последовательный АЦП 5, блок 6 памяти, шина 7 входного сигнала, второй ЦАП 8, шины 9 эталонного кода, шины 10 выходного кода, Выходы АЦП с разрядностью,N1 через первый ЦАП 2, разрядность которого также равна N1, соединены с входом) блока 3 аналогового вычитания, второй вход которого подключен к входу параллельного МЩ 1 и одновременно к выходу аналогового переключателя 4, выход блока 3 аналогового . вычитания соединен с входом последовательного АЦП 5 разрядностью N2, выходы которого соединены с первыми ад- ресньгми входами блока 6 памяти, его вторые адресные входы соединены с выходами параллельного АЦП 1, первый вход аналогового переключателя 4 соединен с шиной 7 входного .сигнала,а второй его, вход - с выходом второго ЦАП 8, имеющего разрядность N3 N1 « N2 + , причем его входы соединены, с шинами 9 эталонного кода и . входами записи блока 6 памяти, выходы которого подключены к шинам 10, выходно о кода двухступенчатого АЦП, Двухступенчатый АЦП работает следующим образом. В режиме калибровки с шин 9 эталонного кода кодовые слова по .тупают на входы ..второго. ЦАП 8, выходное напряжение к.оторого через аналоговый переключатель 4 поступает на вход параллельного АШ1 I и одновременно на вход блока 3 аналогового 1«ычитания, в котором вьщеляется разность выходных напряжений второго ЦАП 8 н первого ЦАП 2, причем выходное на пряжение первого ЦАП 2 является аналоговым эквивалентом цифрового слова поступившего на него с параллельного АЦП 1.. Разность выходных напряжений втор го ЦАП 8 и первого ЦАП 2 кодируется последовательным АЦП 5 и в качестве кодов младших разрядов поступает на первые адресные входы блока 6 памяти На вторые адресные входы блока 6 па мяти в качестве кодов старших .разрядов поступает цифровое слово с выходов параллельного АЦП 1, Одновременно на входы записи блок 6 памяти поступают кодовые слова эта лонного кода. Запись .этих кодовых слов по установленному адресу происходит сразу же после изменения состояния младшего разряда поа1едова тельного АЦП 5, Таким образом, двухступенчатый АЦ в целом калибруется точным ЦАП 8. /Та кая калибровка проводится периодичес ки во время .работы, чтобы учесть не только неточность отдельных элементов, но и их температурную нестабильность, причем быстродействие вто рого ЦАП 8 может бьпь существенно ни же быстродействия преобразователя в целом, что значительно облегчает его разработку. В. рабочем режиме сигнал с шины 7 входного сигнала через аналоговый переключатель 4 поступает одновремен но на вход параллельного АЦП 1 и на второй вход блока 3 аналогового вычитания, в котором выделяется разность входного сигнала и выходного напряжения первого ЦАП 2, Это выходное напряжение является аналоговым эквивалентом цифр)ового слова, поступающего на первый ЦАП 2 с параплельного АЦП К Сигнал с выхода блока 3 аналогового вычитания кодируется пос&едовательным АЦП 5 и поступает на первый адресный вход блока 6 памяти в качестве кодов младших разрядов. На вторые адресные входы блока 6 памяти в качестве кодов старших разрядов поступает цифровое слово с выходов параллельного АЦП I. Цифровое слово с в{ гходов считывания блока 6 памяти является выходным сигналом двухступенчатого АЦП и поступает на шины выходно-, го кода 10. . Технико-экономический эффект заключается в том, что в рабочем режиме в качестве выходного кода используется его более точный эквивапент. определенный в режиме калибровки. Это позволяет уменьшить нелинейность преобразователя до уровня младшего разряда второго ЦАП 8, т.е. до половины младшего разряда АЦП в целом. Например, если разрядность двухступенчатого АЦП равна 12, второй ЦАЛ 8 должен иметь 13 разрядов, нелинейность АЦП в целом в этом случае не превышает 0,012%, в то время как двухсту пенчатый АЦП той же разрядности с корректировкой только .характеристи ки .1ДАП имеет нелинейность 3%.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1319279A1 |

| Устройство для двухступенчатогоАНАлОгО-цифРОВОгО пРЕОбРАзОВАТЕля | 1977 |

|

SU809543A1 |

| Устройство двухступенчатого аналого-цифрового преобразования | 1985 |

|

SU1266003A1 |

| Гибридный функциональный преобразователь | 1980 |

|

SU879610A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для ввода-вывода аналоговых сигналов | 1981 |

|

SU1015369A1 |

| Вычислительный узел сеточной модели для решения нелинейных уравнений теплопроводности | 1986 |

|

SU1388912A1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1541778A1 |

| Преобразователь код-напряжение | 1984 |

|

SU1197084A1 |

ДВУХСТУПЕНЧАТЫЙ АНАЛОГОЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий параллельный аналого-цифровой преобразователь, выходы которого через первый цифроаналоговый преобразователь соединены с первым входом блдка аналогового вычитания, второй вход которого соединен с входом параллельного .аналого-цифрового преобразователя, а - с входом последовательного аналого-цифрового преобразователя, выходы которого соединены с первыми адресными входами блока памяти, отличающийс я тем, что, с целью повышения точ ности преобразования, в него введены аналоговый переключатель и второй цифроаналоговый преобразователь, входы которого подключены к шинам эталонного кода и входам записи блока памяти, а выход - к первому входу аналогового переключателя, второй вход которого соединен с шиной входного сигнала, а выход - с входом параллельного аналого-цифрового.преобразователя , при- этом вторые адрес(Л ные входы блока памяти подключены к выходам параллельного аналого-цифрового преобразователя, а выходы - с шинами выходного кода.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| РЫБОЗАЩИТНОЕ СООРУЖЕНИЕ | 2006 |

|

RU2310036C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для двухступенчатогоАНАлОгО-цифРОВОгО пРЕОбРАзОВАТЕля | 1977 |

|

SU809543A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| . | |||

Авторы

Даты

1985-05-30—Публикация

1983-09-16—Подача