t

Изобретен le относится к вычислительной технике и может быть исполь эовано при построении быстродейству ющих устройств обработки цифровой информации.

Целью изобретения является упрощение одноразрядного четверичного сумматора.

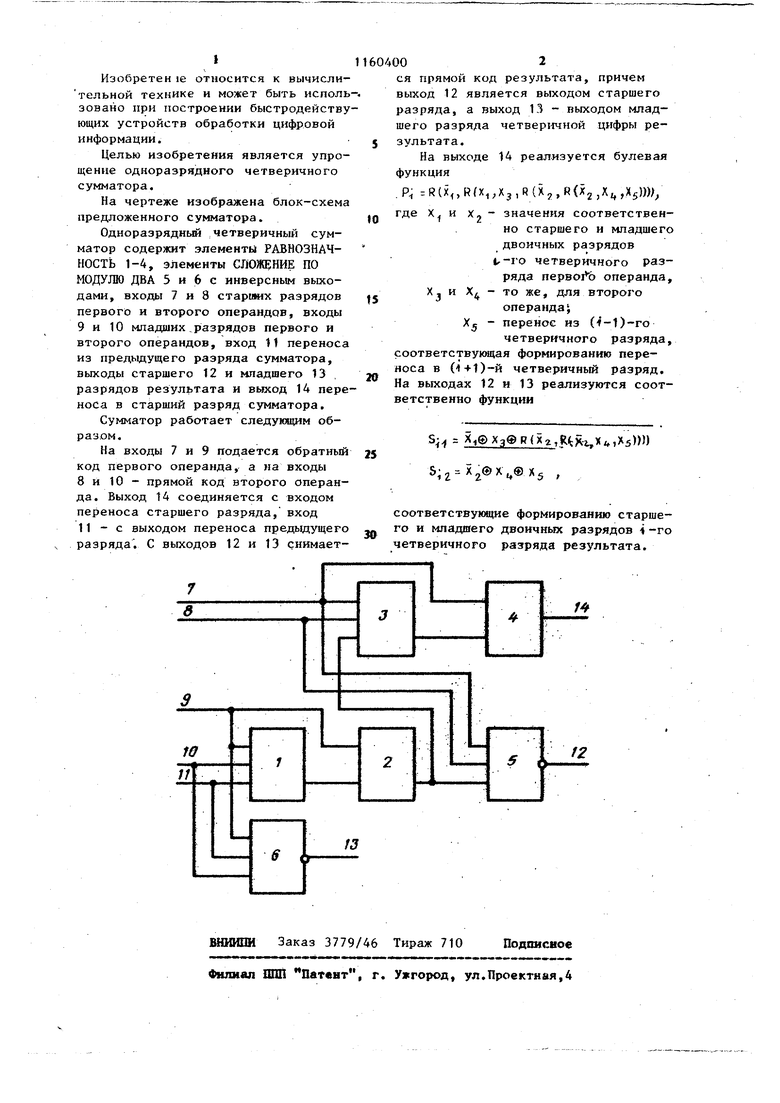

На чертеже изображена блок-схема предложенного сумматора.

Одноразрядньш , четверичный сумматор содержит элементы РАВНОЗНАЧНОСТЬ 1-4, элементы СЛОЖЕНИЕ ПО МОДУЛЮ ДВА 5 и 6 С инверсным выходами, входы 7 и 8 старижх разрядов первого и второго операндов, входы 9 и 10 младших.разрядов первого и второго операндов, вход 11 переноса из предыдущего разряда сумматора, выходы старшего 12 и младшего 13 , разрядов результата и выход 14 переноса в старший разряд сумматора.

Сумматор работает следующим образом.

На входы 7 и 9 подается обратный код первого операнда, а на входы 8 и 10 - прямой код второго операнда. Выход 14 соединяется с входом переноса старшего разряда, вход 11 - с выходом переноса предыдущего разряда. С выходов 12 и 13 снимает11604002

ся прямой код результата, причем выход 12 является выходом старшего разряда, а выход 13 - выходом младшего разряда четверичной цифры ре5 зультата.

На выходе 14 реализуется булевая функция

.P rR(X,R(Xi;X3,R(X2,R(X2,X;,,X5)));/

где х и

Х значения соответственно старшего и младшего двоичных разрядов 1,-1о четверичного разряда перво1 6 операнда, X. и Х - то же, для второго

oneрандаJ Х - перенос из (f-1)-ro

четверичного разряда, соответствующая формированию переноса в ()+1)-й четверичный разряд. На выходах 12 и 13 реализуются соответственно функции

S Хдф R ( X 2 ,RtX-2,X и .Хз))))

,

соответствуняцие формированию старшего и младшего двоичных разрядов i -го четверичного разряда результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный четверичный сумматор-вычитатель | 1984 |

|

SU1229756A1 |

| Четверичный сумматор | 1983 |

|

SU1124290A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ N ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2047897C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ СЕМИ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018930C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018925C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018927C1 |

| Одноразрядный четверичный сумматор | 1981 |

|

SU1023322A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018923C1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2018924C1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2028660C1 |

ОДНОРАЗРЯДНЫЙ ЧЕТВЕРИЧНЫЙ СУММАТОР, содержащий элементы РАВНОЗНАЧНОСТЬ, причем первый вход первого элемента РАВНОЗНАЧНОСТЬ яйляется входом переноса из предыдущего разряда сумматора, отличающийся тем, что, с целью упрощения сумматора, он содержит два элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, инверсный выход первого из которых является выходом старщего разряда результата, инверсный выход второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА выходом младшего разряда результата, а его первьй вход - входом младшего разряда первого операнда и соединен с вторым входом первого элемента РАВНОЗНАЧНОСТЬ и первым входом второго элемента РАВНОЗНАЧНОСТЬ, второй вход второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА является .входом младшего разряда второго операнда и соединен с третьим входом первого элемента РАВНОЗНАЧНОСТЬ, третий вход вторЬго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединен с первым входом первого элемента РАВНОЗНАЧНОСТЬ, вы- . ход которого соединен с вторым входом второго элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первьй входом первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА и первым входом ретьего элемента РАВНОЗНАЧНОСТЬ, второй вход сл которого является входом старшего разряда первого операнда и соединен с вторым входом первого элемента СЛОЖЕНИЕ ПО ШДУЛО ДВА и первым входом четвертого элемента РАВНОЗНАЧНОСТЬ, третий вход является входом старшего разряда второго операнда и соединен с третьш входом первого элемента СЛОЖЕНИЕ ПО МОДУШ) ДВА, а Од выход - с вторым входом четвертого о элемента РАВНОЗНАЧНОСТЬ, выход кото4 рого является выходом переноса сумматора.

в

10

1

f2

| Лысиков Б.Г | |||

| Арифметические н логические основы цифровых автоматов | |||

| Минск, Высшая школа, 1980, с | |||

| Рельсовый башмак | 1921 |

|

SU166A1 |

| Одноразрядный четверичный сумматор | 1981 |

|

SU1023322A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-07—Публикация

1983-12-23—Подача