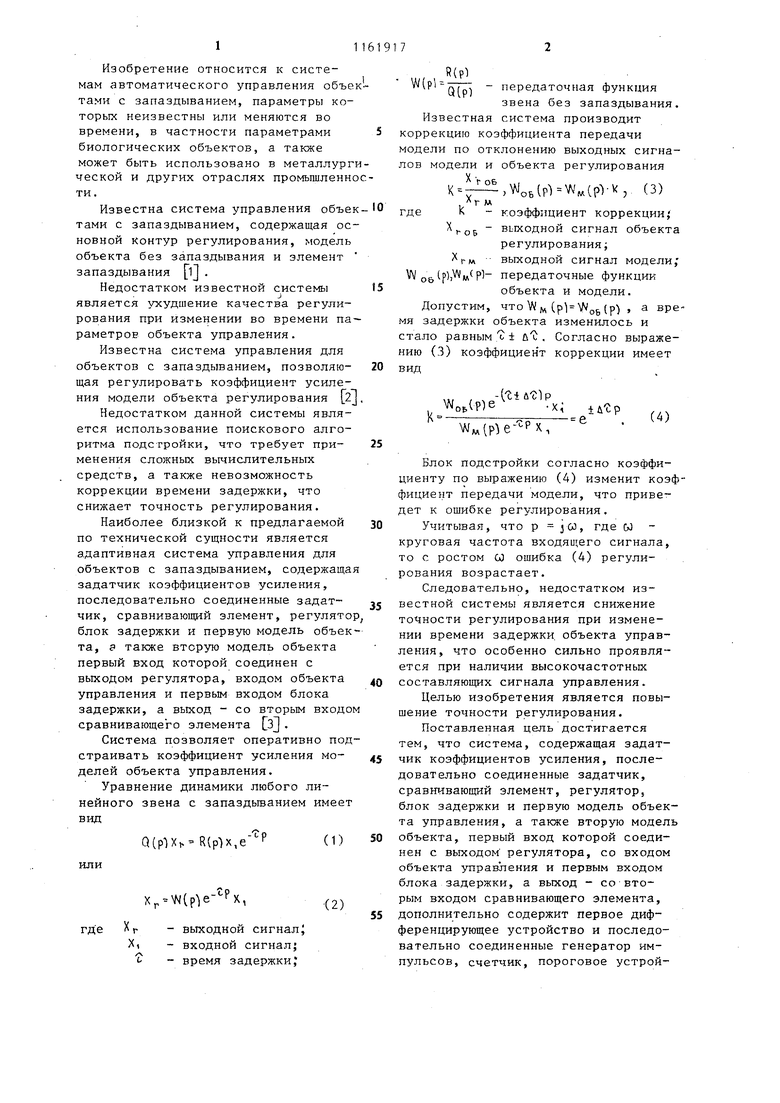

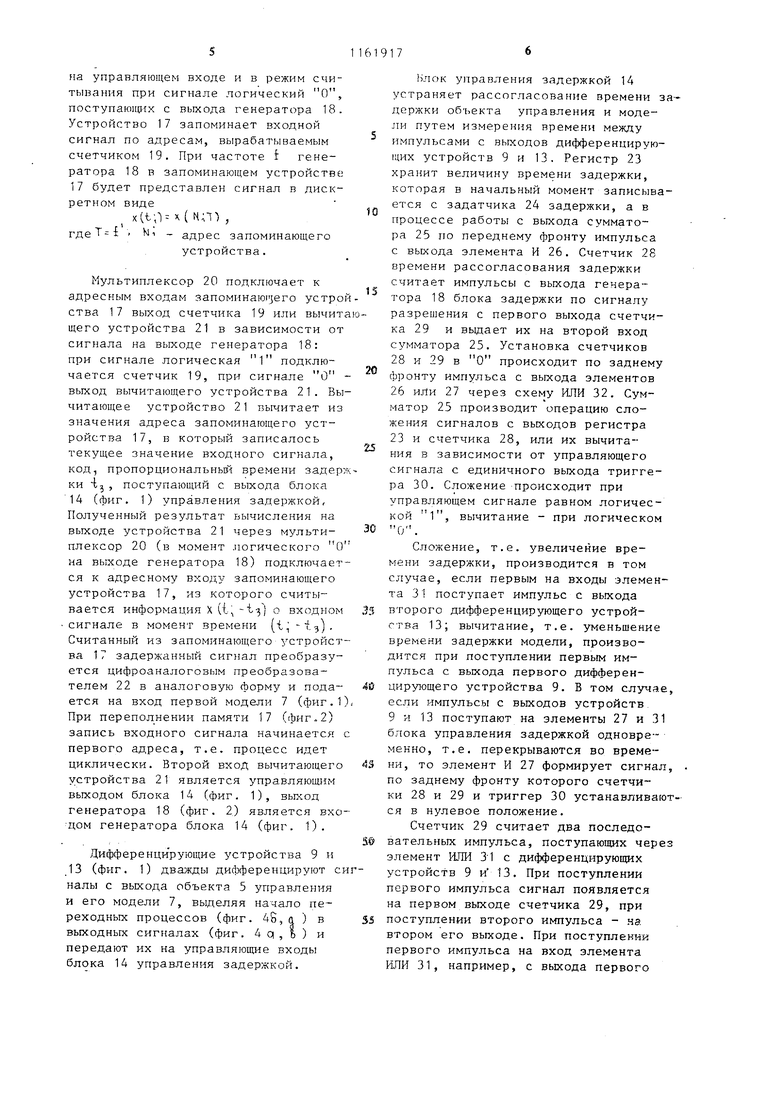

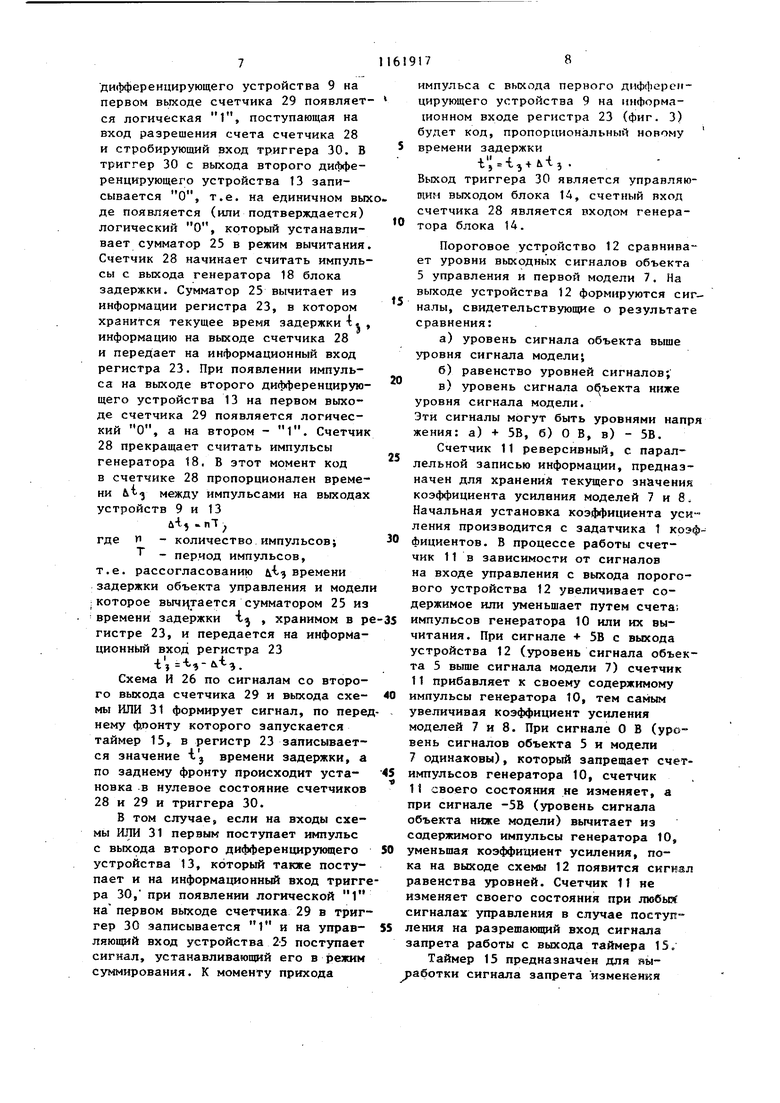

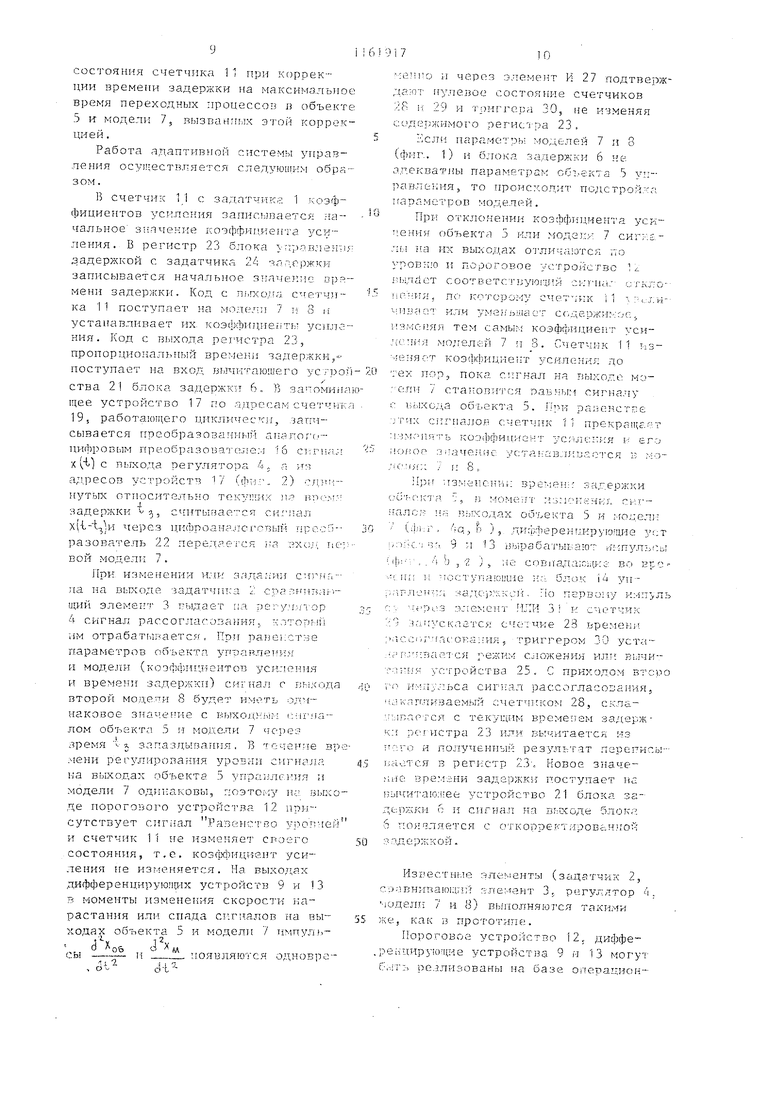

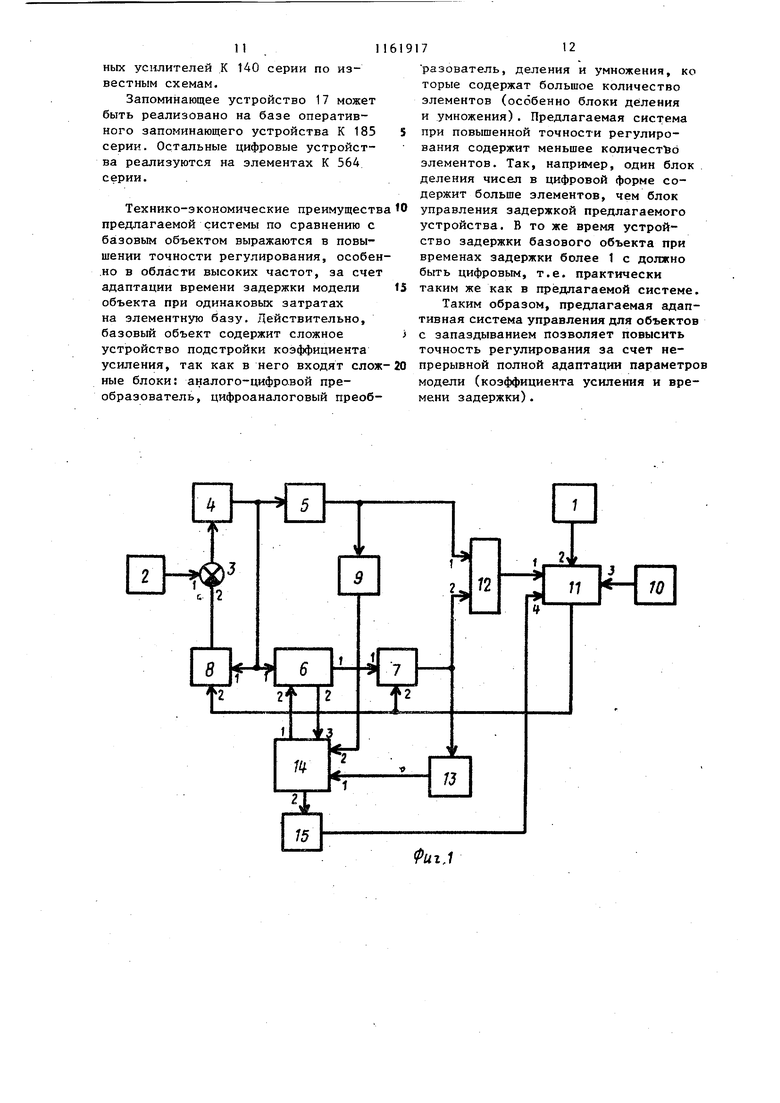

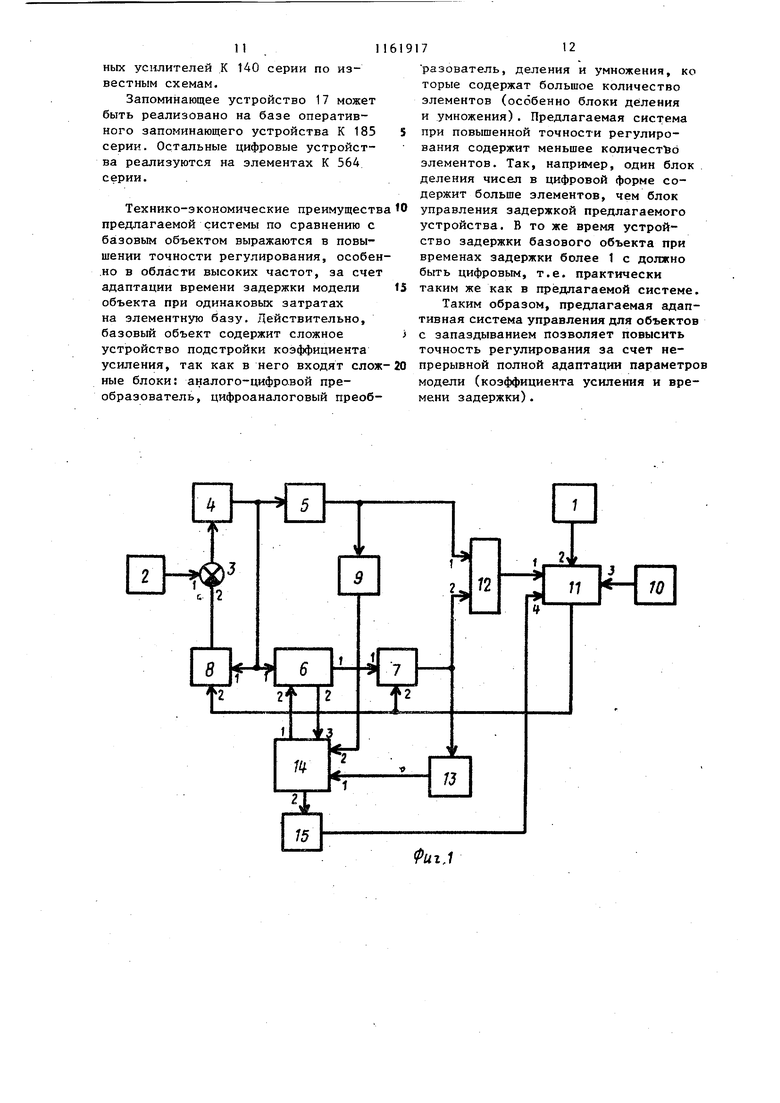

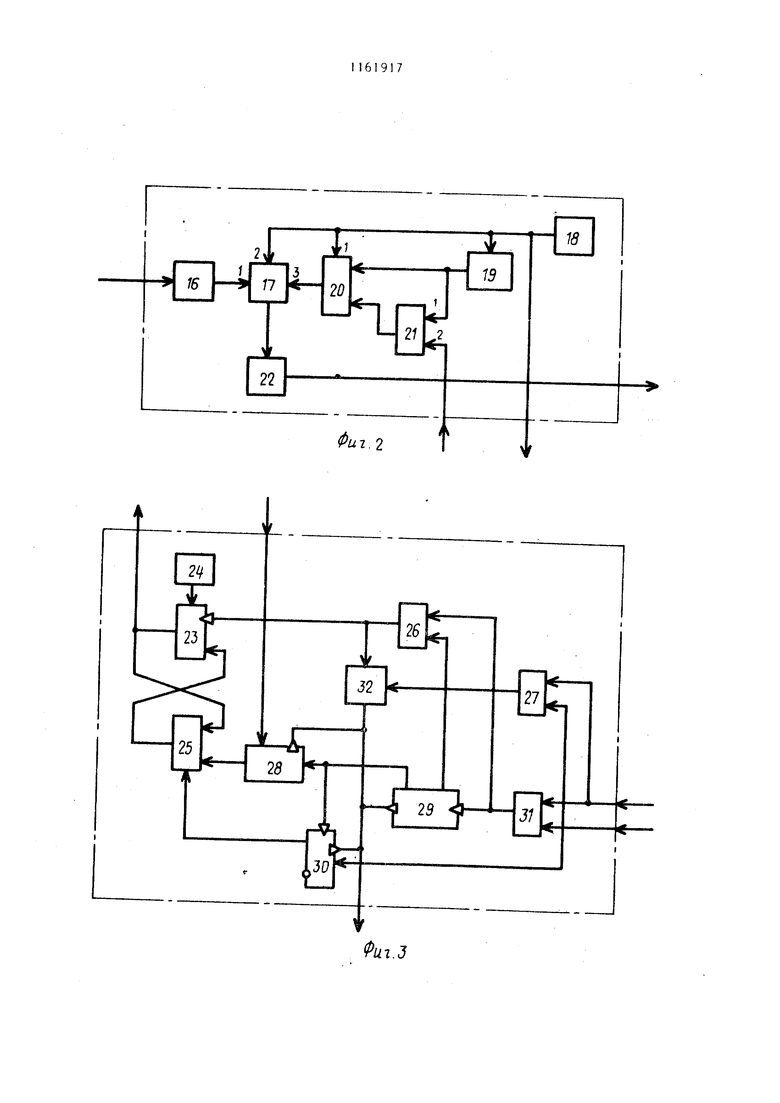

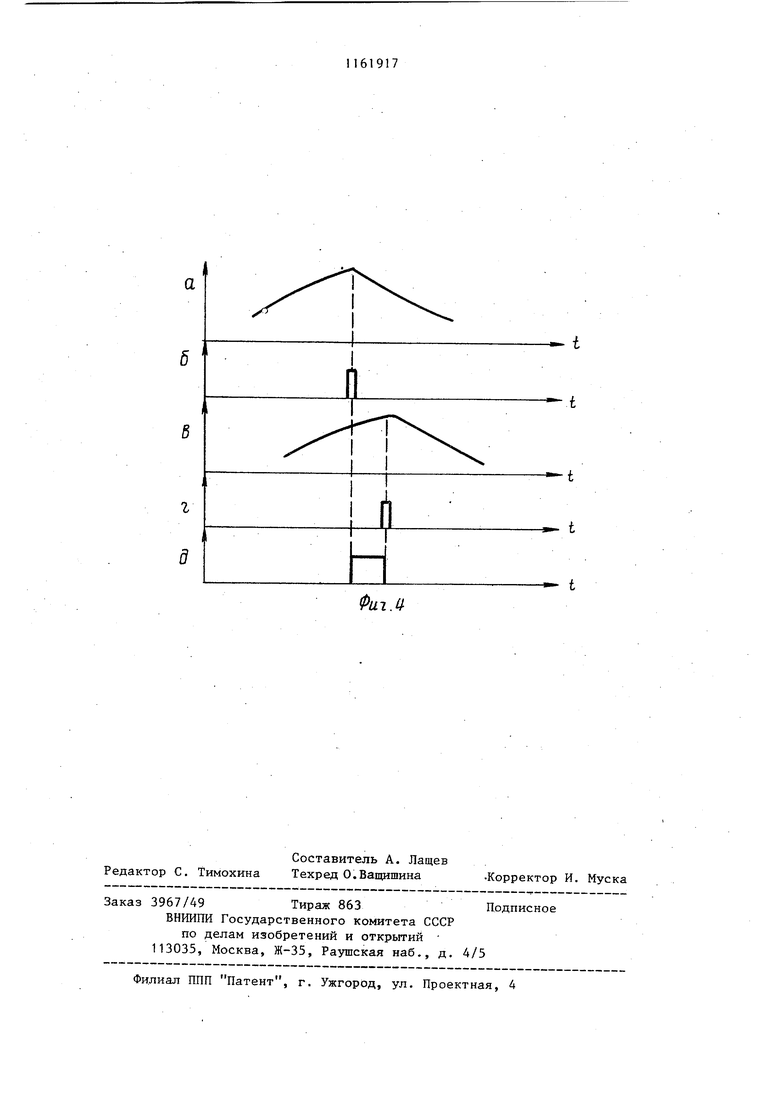

Изобретение относится к системам автоматического управления объ тами с запаздыванием, параметры ко торых неизвестны или меняются во времени, в частности параметрами биологических объектов, а также может быть использовано в металлур ческой и других отраслях промьшленн ти. Известна система управления объе тами с запаздыванием, содержащая ос новной контур регулирования, модель объекта без запаздывания и элемент запаздывания l . Недостатком известной системы является ухудшение качества регулирования при изменении во времени па раметров объекта управления. Известна система управления для объектов с запаздыванием, позволяющая регулировать коэффициент усиления модели объекта регулирования 2 Недостатком данной системы является использование поискового алгоритма подстройки, что требует применения сложных вычислительных средств, а также невозможность коррекции времени задержки, что снижает точность регулирования. Наиболее близкой к предлагаемой по технической сущности является адаптивная система управления для объектов с запаздыванием, содержащ задатчик коэффициентов усиления, последовательно соединенные задатчик, сравнивающий элемент, регулят блок задержки и первую модель объе та, а также вторую модель объекта первый вход которой соединен с выходом регулятора, входом объекта управления и первым входом блока задержки, а выход - со вторым вход сравнивающего элемента 3j . Система позволяет оперативно по страивать коэффициент усиления моделай объекта управления. Уравнение динамики любого линейного звена с запаздьгоанием имее вид Q(pTXt- R(p)x,eP X, W(, XT - выходной сигнал - входной сигнал; - - время задержки, передаточная функция звена без запаздывания. Известная система производит коррекцию коэффициента передачи модели по отклонению выходных сигналов модели и объекта регулирования K Wob((PV (3) м где К - коэффициент коррекции; Xf.g - вьпходной сигнал объекта регулирования; выходной сигнал модели; W 05 (p),VJ|i(pl- передаточные функции объекта и модели. Допустим, что W (,(p) , а время задержки объекта изменилось и стало равным .t ± ui, Согласно выражению (3) коэффициент коррекции имеет вид ,„ , -UiuSlP VJob(P)e -х; ii-jp w ipu- p. Блок подстройки согласно коэффициенту по выражению (4) изменит коэффициент передачи модели, что приведет к ошибке регулирования. Учитывая, что р jCO, где ы круговая частота входящего сигнала, то с ростом СО ошибка (4) регулирования возрастает. Следовательно, недостатком известной системы является снижение точности регулирования при изменении времени задержки, объекта управления, что особенно сильно проявляется при наличии высокочастотных составляющих сигнала управления. Целью изобретения является повышение точности регулирования. Поставленная цель достигается тем, что система, содержащая задатчик коэффициентов усиления, последовательно соединенные задатчик, сравнивающий элемент, регулятор, блок задержки и первую модель объекта управления, а также вторую модель объекта, первый вход которой соединен с выходом регулятора, со входом объекта управления и первым входом блока задержки, а выход - со вторым входом сравнивающего элемента, дополнительно содержит первое дифференцирующее устройство и последовательно соединенные генератор импульсов, счетчик, пороговое устройство, второе дифференцирующее устройство, блок управления задержкой и таймер, вход первого дифференцирующего устройства соединен с вьгходом объекта управления и первьш входом порогового устройства а выхо со вторым входом блока управления задержкой, .второй вход порогового устройства соединен с выходом первой модели объекта управления и в:йодом второго дифференцир; тощего устройства, выход порогового устрой ства соединен с первым входом счетчика $ второй вход которого соединен с задатчиком коэффициентовj третий вход - с генератором импульсов, четвертый вход - с выходом таймера а выход -- со вторыми входами первой и второй моделей объекта, вход таймера, соединен со вторым выходом блока управления задержкой, первый выход которого соединен со вторым входом блока задержки, первый вход с выходом второго дифс еренцирзтощего устройства, а тр-этий вход - со вторым выходом блока задержки. Б основу работы адаптивной системы положен принцип непрерывной адаптации коэффициента усиления двух моделей объекта управления с запаздыванием и без запаздывания за счет поддержания равенства сигна лов на выходах объекта и модели с запаздываниемизменением коэффициента усиления модели о Б Л О J где л05 сигнал на выходе объекта :л - сигнал на выходе модели} - коэффициент усиления модели, и принДип адаптации времени задержки модели объекта за счет непрерывного контроля моментов возникновения переходных процессов на выходах объекта управления и модели, т.е. сравнения моментов времени, в 2 oTOjf существует гфоиззодная выход с} X (зь а К -ff, ных .сигналов --lir и --, d-t Для контроля выбрана вторая прои водная, исходя из того, что представляет собой короткие импульсы, возника1011(Ие только л момент начала переходных процессов, в остальное время она равна нyлю На фиг. 1 представлена структурн схема предла аемой адаптивной системы§ на фиг, 2 - структ рная схе 174 ма блока задержки; на фиг. 3 - структзфная схема блока управления задержкой на фиг. 4.- диаграммъ вы- ;одньгх сигналов; а объекта управления; S - первого дифференцирующего устройства; 6 - первой модели объекта; i - второго дифференцирующэго устройстваJ Q- на управляющем вхо де счетчика рассогласования задержки. Адаптивная система управления (фиг. 1) для объектов с запаздыванием содержит задатчик 1 коэффициентов усиления, задатчик 2, сравнивающий эле:-ант 3, регулятор А, объект управлегтия 5, блок задержки 6, первую модель объекта 7, вторую модель объекта 8 первое дифференцирующее устройство 9, генератор импульсов 10, счетчик 11, пороговое устройство 12, второе дифференцирующее устройство 13, блок /правления задержкой 14, таймер 15. Блок задержки (фиг. 2) включает 3себя аналого-цифровой преобразователь 15, запоминающее устройство 17, генератор 18, счетчик, 19 адресов, мультиплексор 20,, вычитающее устройство 21, цифроаналоговьй преобразователь 22. Блок управления задержкой (фиг.З) содержит регистр 23, задатчик 24 времени задержки, сумматор 25, схемы И 26 и 27, счетчик 28 времени рассогласования задержки, счетчик 29, триггер 30 и схемы ИЛИ 31 и 32. Известные устройства, задатчик 2,, сравнивающий элемент 3, регулятор 4и модели объекта 7 и 8 вьтолняют те лсе функции, что и в прототипе. Блок б задержки сигналов регулятора 4 управляемый. Он может быть выполнен как в аналоговом варианте, так и i; цифровом. В случае аналогового варианта он может представлять собг1Й ультррзвуковую линию задержи с регулируемой характеристикой. а фиг, 2 представлен цифровойваиант блока задержки, как более редпочтительный, так как обладает ольшими возможностями (задержка игнала может быть реализована любой лительности). Аналого-цифровой реобразователь 16 преобразует входой сигнал с регулятора 4 (фиг. 1) цифровой и передает на информаионный вход запоминающего устройтва 17 (фиг. 2). Запоминающее стройство 17 переходят в режим аплсн при сигнале логическая 1 на управляющем входе и в режим считывания при сигнале логический О, поступаю1 1их с выхода генератора 18. Устройство 17 запоминает входной сигнал по адресам, вырабатываемым счетчиком 19. При частоте f генератора 18 в запоминающем устройстве 17 будет представлен сигнал в дискретном виде K(t;V х( N;T) , Ml адрес запоминающего устройства. Мультиплексор 20 подключает к адресн)1м входам запоминаюпзего устро ства 17 выход счетчика 19 или вычит щего устройства 21 в зависимости от сигнала на выходе генератора 18: при сигнале логическая 1 подключается счетчик 19, при сигнале О выход вычитающего устройства 21. Вы читающее устройство 21 вычитает из значения адреса запоминающего устройства 17, в который записалось текущее значение входного сигнала, код, пропорциональньп1 времени задер ки tj , поступающий с выхода блока 14 (фиг. 1) управления задержкой, Полученный результат вычисления на выходе устройства 21 через мультиплексор 20 (в момент логического на выходе генератора 18) подключает ся к адресному входу запоминающего устройства 17, из которого считывается информация X (ti, -t-}} о входном сигнале в момент времени (t )Считанный из запоминающего устройс ва 17 задержанный сигнал преобразу ется дифроаналоговым преобразователем 22 в аналоговую форму и пода ется на вход первой модели 7 (фиг. При переполнении памяти 17 (фиг.2) запись входного сигнала начинается первого адреса, т.е. процесс идет циклически. Второй вход вычитающег устройства 21 является управляющим выходом блока 14 (фиг. 1), выход генератора 18 (фиг. 2) является вх дом генератора блока 14 (фиг. 1). Дифферендирующие устройства 9 и 13 (фиг. 1) дважды дифференцируют налы с выхода объекта 5 управления и его модели 7, выделяя начало переходных процессов (фиг. 4S, о ) в выходных сигналах (фиг. 4 q, Ь ) и передают их на управляющие входы блока 14 управления задержкой. Нлок управления задержкой 14 устраняет рассогласование времени задержки объекта управления и модели путем измерения времени между импульсами с выходов дифференцирующих устройств 9 и 13. Регистр 23 хранит величину времени задержки, которая в начальный момент записывается с задатчика 24 задержки, а в процессе работы с выхода сумматора 25 по переднему фронту импульса с выхода элемента И 26. Счетчик 28 времени рассогласования задержки считает импульсы с выхода генератора 18 блока задержки по сигналу разреи1ения с первого выхода счетчика 29 и вьщает их на второй вход сумматора 25. Установка счетчиков 28 и 29 в О происходит по заднему фронту импульса с выхода элементов 26 или 27 через схему ИЛИ 32. Сумматор 25 производит операцию сложения сигналов с выходов регистра 23 и счетчика 28, или их вычитания в зависимости от управляющего сигнала с единичного выхода триггера 30. Сложение происходит при управляющем сигнале равном логической 1, вычитание - при логическом О. Сложение, т.е. увеличение времени задержки, производится в том случае, если первым на входы элемента 31 поступает импульс с выхода второго дифференцирующего устройства 13; вычитание, т.е. уменьшение времени задержки модели, производится при поступлении первым импульса с выхода первого дифференцирующего устройства 9. В том случае, если импульсы с выходов устройств. 9 и 13 поступают на элементы 27 и 31 блока управления задержкой одновременно, т.е. перекрываются во времени, то элемент И 27 формирует сигнал, по заднему фронту которого счетчики 28 и 29 и триггер 30 устанавливаются в нулевое положение. Счетчик 29 считает два последовательных импульса, поступающих через элемент ИЛИ З с дифференцирующих устройств 9 и 13. При поступлении первого импульса сигнал появляется на первом выходе счетчика 29, при поступлении второго импульса - на втором его выходе. При поступлении первого импульса на вход элемента НИИ 31, например, с выхода первого ди(})ференцирующего устройства 9 на первом выходе счетчика 29 появляется логическая 1, поступающая на вход разрешения счета счетчика 28 и стробируюший вход триггера 30. В триггер 30 с выхода второго дифференцирующего устройства 13 записывается О, т.е. на единичном вых де появляется (или подтверждается) логический О, который устанавливает сумматор 25 в режим вычитания. Счетчик 28 начинает считать импульсы с выхода генератора 18 блока задержки. Сумматор 25 вычитает из информации регистра 23, в котором хранится текущее время задержкит«, информацию на выходе счетчика 28 и передает на информационный вход регистра 23. При появлении импульса на выходе второго дифференцирующего устройства 13 на первом выходе счетчика 29 появляется логический О, а на втором - 1. Счетчик 28 прекращает считать импульсы генератора 18, В этот момент код в счетчике 28 пропорционален времени между импульсами на выходах устройств 9 и 13 ui пТ где )1 - количество, импульсов; - период импульсов, т.е. рассогласованию -t времени задержки объекта управления и модел :которое вычитается сумматором 25 из времени задержки i , хранимом в р гистре 23, и передается на информационный вход регистра 23 -t, -t,-/ii,. Схема И 26 по сигналам со второго выхода счетчика 29 и выхода схемы ИЛИ 31 формирует сигнал, по пере нему флонту которого запускается таймер 15, в регистр 23 записывается значение ij времени задержки, а по заднему фронту происходит установка в нулевое состояние счетчиков 28 и 29 и триггера 30. В том случае, если на входы схемы ИЛИ 31 первым поступает импульс с выхода второго дифференцирующего устройства 13, который также поступает и на информационный вход тригг ра 30, при появлении логической 1 на первом выходе счетчика 29 в триг гер 30 записывается 1 и на управляюпр й вход устройства 2-5 поступает сигнал, устанавливающий его в режим суммирования. К моменту прихода импульса с выхода первого дифференцирующего устройства 9 на информашонном входе регистра 23 (фиг. 3) будет код, пропорциональный новому времени задержки , . Выход триггера 30 является управляюп(им выходом блока 14, счетный вход счетчика 28 является входом генератора блока 14. Пороговое устройство 12 сравнивает уровни выходных сигналов объекта 5 управления и первой модели 7. На выходе устройства 12 формируются сигналы, свидетельствующие о результате сравнения: а)уровень сигнала объекта выше уровня сигнала модели; б)равенство уровней сигналов; в)уровень сигнала объекта ниже уровня сигнала модели. Эти сигналы могут быть уровнями напря жения: а) + 5В, б) О В, в) - 5В. Счетчик 11 реверсивный, с параллельной записью информации, предназначен для хранений текущего значения коэффициента усиления моделей 7 и 8. Начальная установка коэффициента усиления производится с задатчика 1 коэффициентов. В процессе работы счетчик 11 в зависимости от сигналов на входе управления с выхода порогового устройства 12 увеличивает содержимое или уменьшает путем счета; импульсов генератора 10 или их вычитания. При сигнале + 5В с выхода устройства 12 (уровень сигнала объекта 5 выше сигнала модели 7) счетчик 11 прибавляет к своему содержимому импульсы генератора 10, тем самым увеличивая коэффициент усиления моделей 7 и 8. При сигнале О В (уровень сигналов объекта 5 и модели 7 одинаковы), который запрещает счетимпульсов генератора 10, счетчик 11 своего состояния не изменяет, а при сигнале -5В (уровень сигнала объекта ниже модели) вычитает из содержимого импульсы генератора 10, уменьшая коэффициент усиления, пока на выходе схемы 12 появится сигнал равенства уровней. Счетчик 11 не изменяет своего состояния при любы сигналах управления в случае поступления на разрешающий вход сигнала запрета работы с выхода таймера 15. Таймер 15 предназначен для выаботки сигнала запрета изменения состояния счетчика 11 при коррекции времени задержки на максимально время переходных процессов л объект 5 к модели 7, вызванных этой коррек цией . Работа адаптивной системы управления осуи-еств.пяется следующим обра зом. В счетчик 1 1 с задптчзчКс. 1 коэф фициентов усиления записывается лачальное знпчекие коэффицртента усиления. В регистр 23 блока у.:;7)явле;-г; задержкой с задатчикс мени задержк1-г. Код с выхода счетчика 1 1 поступает на моле/ш 7 т- 8 п устанавливает их коэффггциеит : усилС; ния. Код с выхода регистра 23, пропорциональный времени задержки, поступает па вход вычитающего ус rpo ства 21 блока задержки 6, )5 запомин щее устройство 1 7 по -а.пресам счеччик 19, работалогцего циклически, записывается преобразова лпый а па поп:.цифровым преобразоваг(:. 16 сггплл X (.t 1 с в ; гх о д. а р е г ул я тор а -4 ,, а т з а;,ресов устройств 17 (фиг.. 2) лп гxii, через ц1Щ)роапа.17сгст5Ый г рссП-разователь 22 перегнав/ся i;a зход iiC вой моделг; 7 . При изменении vi.n-. задании c. па выходе задатчика 2 ера nrnniai-vщий 3 выдает па регулячор 4 сигнал рассогласозаяияJ K, iiM отрабатывается . При равекст зе параметров объекта упаавлетпя и модели (коэффигл-пептов усиления и времени задержки) сигнал с второй модели 8 будет иметь одинаковое значение с вг,1хоцН -,М (мипа-лом объект 5 и модели 7 через лремя t X запазггь ва1П5я, В точепге вр .чепи регулирования сигнала на выходах объекта 5 упра;злс)П1я и модели 7 одинаковы, поэтомз па выко сутствует сипгал Равепстео у опчей и счетчик 11 не изменяет своего состояния, т.е. козажицггент усиления пе изг-1еняется. На выходах дифференцируюп ; 1Х устройств 9 и 13 в моменты изменения скорости парастания или спада стииталов fia выходах объекта 5 и модели / импульd Xd xсы.- и -.5i. появляются одповре--i 2; , , о V,ci X ;i;nro и через элеме11Т И 27 подтвержда;пт нулевое состоя(ие счетчиков Х8 и; 29 и Tpnrreija 30, не изменяя с;одерлсимого регист-ра 23 . IlcnH параметрь; моделей 7 и 8 (фьиг,. 1) и б.тгока задержки 6 не равлСУ.ня, то происходит подетрой/а. гараметров моделей. При откоюяепии коэффициента yc iт;ения объекта 5 или моде. 7 сигкг:и.1 на их выходах отличаются по уровню и пороговое ycTpoi-icTBO 1 Г :ДаеТ еООТВеТС1ВуЮ1;Г Й СИГН;, мегия, по которО;-;у счет:чк 1 -r-t.j.vrчивае1 или yt- sn- iitai r сс,де зжиг:ое.. изменяя тем самы;--; коэффи1дие 1т усиделия мо;гелей 7 и 8. Счетчик 11 .епяет коэ()фициепт уеилеьгия до ;-ех пор, пока сигнал на выходе мс ели / становимся рав.чым сигналу ::: 1;ыхо;.,а объекта 5. При paiUHiCTre: Ггпх cnrniajjOH счетчик 1 1 прекращает :|з епять коэффициент уемлептия i его пояое ::л-аче;1ие устанавл{;иается в мо.-к:1я;: ;; и 8, При измепотпи: Bpe-ieni; задержки LOF-CKTa, ; , 1; -ЮМеЛ ИЗГКЛКНИЯ Ci-Uналс; ia 1 ькодах объекта 5 и модел ; 1Ф|:ГЛ -qjb ), дг ффере -И1Ируюп1ие у;;т ,(... 9 и 13 иырабачыгагог i-ишульеь; .. А Ь 2 J5 сов 1апа:с;д ;е во вре- lii: п чоступаюиикг ;;a блсж 14 упгаглон;:: заде ;;лКС1 - rio первому ; . Upi.3 з:;е :ет1Т ИЛИ 3; и счетчик ::Т запуекаетея счетчие 23 времек ; аесогчасовапия, триггером 30 устасгливает-ся режим еложения или вычи;:-ггЛЯ устройства 25. С приходом втсро гп и :Д:;льса рассогласозани):. ;акап.пи}заемый счетчиком 28, склакзлаегся с текуиатм временем задержки регистра 23 или вычитается из пого и получепный результат переписьгнаотся в регистр 23, Новое значеMiie времени задержки поступает па пычитаюмдве устройство 21 блока за д ;;ржки б и сигнал на вькоде блока 6 по зляегся с откорректирован ;ой задерл;кой. Из1есгн -ле (задатчик 2, 1ьмвнива 01:1и;т :;ле;-5ент 3, регулятор i . чоделт; 7 и 8) В)полняю1ся такими е, к а к в пр о т о т ип е. Пороговое устройство 12, диффеейдирующие устройства 9 и 13 могут п:гь реализованы па базе операциок11ных усилителей К 140 серии по известным схемам. Запоминающее устройство 17 может быть реализовано на базе оперативного запоминающего устройства К 185 серии. Остальные цифровые устройства реализуются на элементах К 564 серии. Технико-экономические преимущест предлагаемой системы по сравнению с базовым объектом выражаются в повышении точности регулирования, особе но в области высоких частот, за сче адаптации времени задержки модели объекта при одинаковых затратах на элементную базу. Действительно, базовый объект содержит сложное устройство подстройки коэффициента усиления, так как в него входят сло ные блоки: аналого-цифровой преобразователь, цифроаналоговый преоб 712 разователь, деления и умножения, ко торые содержат большое количество элементов (особенно блоки деления и умножения). Предлагаемая система при повышенной точности регулирования содержит меньшее количество элементов. Так, например, один блок деления чисел в цифровой форме содержит больше элементов, чем блок управления задержкой предлагаемого устройства. В то же время устройство задержки базового объекта при временах задержки более 1 с должно быть цифровым, т.е. практически таким же как в предлагаемой системе. Таким образом, предлагаемая адаптивная система управления для объектов с запаздыванием позволяет повысить точность регулирования за счет непрерывной полной адаптации параметров модели (коэффициента усиления и времени задержки).

(Pui.3

Фи-L.ii

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная система автоматического управления для нестационарных объектов с запаздыванием | 1986 |

|

SU1451644A1 |

| СИСТЕМА УПРАВЛЕНИЯ МНОГОКАНАЛЬНЫМ ВИБРОСТЕНДОМ | 1998 |

|

RU2159949C2 |

| Устройство автоматического регулирования толщины полосы на непрерывном прокатном стане | 1987 |

|

SU1435347A1 |

| Адаптивная система управления для объектов с запаздыванием | 1985 |

|

SU1310774A1 |

| Адаптивная система управления для объектов с изменяющимся запаздыванием | 1984 |

|

SU1191884A1 |

| Адаптивная система управления | 1984 |

|

SU1257607A1 |

| СПОСОБ ДЛЯ ПРОВЕРКИ ТЕХНИЧЕСКОГО СОСТОЯНИЯ ОСНОВНЫХ ТОРМОЗНЫХ СИСТЕМ ТРАНСПОРТНЫХ СРЕДСТВ В ДОРОЖНЫХ УСЛОВИЯХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2407661C1 |

| Адаптивная система управления | 1985 |

|

SU1361502A1 |

| Способ определения внешнебаллистических характеристик снарядов и устройство для его осуществления | 2016 |

|

RU2608358C1 |

| Многоканальный регулятор | 1988 |

|

SU1564586A1 |

АДАПТИВНАЯ СИСТЕМА УПРАВЛЕНИЯ ДЛЯ ОБЪЕКТОВ С ЗАПАЗДЫВАНИЕМ, содержащая задатчик коэффициентов, последовательно соединенные задатчик, сравнивающий элемент, регулятор, блок задержки и первую модель объекта управления, а также модель объекта, первый вход которой соединен с выходом регулятора, со входом объекта управления и с первым входом блока заде1Гжки, а выход - со вторым входом сравнивающего элемента, отличающаяся тем, что, с целью повышения точности системы, в нее введены первое дифференцирующее устройство и последовательно соединенные генератор импульсов, счетчик, пороговое устройство, второе дифференцирующее устройство, блок управления задержкой и таймер, вход первого дифференцирующего устройства соединен с выходом объекта управления и первым входом порогового устройства, а выход - со вторым входом блока управления задержкой, второй вход порогового устройства соединен с выходом первой модели объекта управления и входом второго дифференцирующего устройства, выход порогового устройства соединен с первым входом счетчика, второй вход которого соединен с (Л задатчиком коэффициентов, третий вход - с генератором импульсов, четвертый вход - с выходом таймера, а выход - со вторыми входами первой и второй моделей объекта, вход таймера соединен со вторым выходом блЬка управления задержкой, первый выход которого соединен со вторым входом блока задержки, первый вход э с выходом второго дифференцирукяцеS 5 го устройства, а третий вход - со вторым выходом блока задержки.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-06-15—Публикация

1983-12-19—Подача