второй выход второго дешифратора подключен к второму входу п.ервого блока анализа, второму входу второго регистра, третьему входу второго блока контроля и второму входу первого формирователя сигналов, первый выход первого дешифратора подключен к первому входу первого блока памяти второй выход которого подключен к второму входу третьего формирователя сигналов и первому входу четвертого элемента ИЛИ, второй выход первог дешифратора подключен к первому входу второго блока памяти, второй выход второго блока памяти подключен к третьему входу третьего формирователя сигналов и второму входу третьего элемента ИЛИ, второй выход блока коммутации подключен к первому вхдду второго регистра, второму входу первого регистра, первому входу третьего формирователя сигналов и входу элемента задержки, первый выход второго регистра подключен к третьему входу третьего дешифратора, второму входу первого блока контроля, третьему входу третьего элемента ИЛИ, и первому входу первого элемента ИЛИ, выход которого подключен к вторым входам первого, вто рого и третьего блоков памяти, вто1946

рой выход второго регистра подключен к второму входу третьего дешифратора, второму входу второго блока контроля, третьему входу четвертого элемента ИЛИ и второму входу первого элемента ИЛИ, первый выход третьего дешифратора подключен к первому вхоцу первого блока анализа, второй .выход третьего дешифратора подключен к первому входу второго блока анализа, выходы первого, второго и третьего формирователей сигналов обьединены и подключены к первому входу четвертого дешифратора, первый и второй выходы которого являются первым и вторьм выходами устройства соответственно, выход элемента задержки подключен к первому входу третьего дешифратора.

2, Устройство по п. 1, отличающееся тем, что блок анализа содержит два элемента И и R5 триггер, выходы элементов И являются первым и вторым выходами блока Соответственно, их первые входы являются первым входом блока, а вторые подключены к соответствующим выходам (5-триггера, первый и второй входы которого являются соответственно вторым и третьим входами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство отсчета времени в цвм | 1977 |

|

SU691828A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1305698A1 |

| Устройство для обмена информацией | 1983 |

|

SU1142824A1 |

| Устройство для управления подканалами обмена между абонентами и электронно-вычислительной машиной | 1976 |

|

SU739514A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Устройство для управления доступом к памяти от двух ЦВМ | 1985 |

|

SU1304030A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

1. УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ДОСТУПОМ К ПАМЯТИ, содержащее блок коммутации, элемент задержки, первый, второй и третий формирователи сигналов, отличаю щ ее с я тем, что, с целью повышения быстродейств т за счет сокращения времени ожид« ия обменов, оно со- держит первый и второй блоки контроля, первый и второй блоки анализа, первый, второй, третий и четвертый дешифраторы, первый, второй и третий блоки памяти, первый и второй регистры, первый, второй, третий и четвертый элементы ИЛИ, третьи входы первого и второго дешифраторов, первые входы второго и третьего элементов ИЛИ объединены и являются первым входом устройства, выход второго элемента ИЛИ подключен к третьим входам первого, второго и третьего блоков памяти, выход Т1 етьего элемента ИЛИ подключен к третьему входу четвертого дешифратора , первый вход первого блока контроля является вторым входом устройства, вторые входы первого и второго дешифраторов, вторые входы второго и четвертого элементов ИЛИ объединены и являются третьим входом устройства, выход четвертого элемента ИЛИ подключен к второму входу четвертого дешифратора, первый вход второго блока контроля является четвертым входом устройства первые выходы первого и второго блоков контроля объединены и подключены к первому входу второго формирователя сигналов, вторые выходы первого и второго блоков контроля подключены к первым входам первого и второго блоков анализа соответственно, первый выход первого блока анализа подключен к первому входу первого блока памяти, первый выход которого подключен к второму входу второго формирователя сигналов и третьему входу сл второго блока анализа, первый выход которого подключен к первому входу второго блока памяти, первый выход которого подключен к третьему входу второго формирователя сигналов и третьему входу первого блока анализа, вторые выходы первого и второго блоков анализа, объедиОд нены и подключены к первому входу третьего блока памяти, первый выход ;о которого подключен к первому входу блока коммутации, первый вьрсод кото4 О) рого подключен к первому входу первого регистра, второй выход которого подключен к второму входу блока коммутации и первому входу второго дешифратора, первый выход первого регистра подключен к первому входу первого дешифратора, первый выход второго дешифратора подключен к второму входу второго блока анализа, третьему входу второго регистра, третьему входу первого блока контроля и первому входу первого формирователя сигналов.

Изобретение относится к автоматике и вычислительной технике и может быть использовано для организации ввода-вьгеода информации на общую внешнюю память из двух электронновычислительных машин (ЭВМ).

В настоящее время некоторые автоматизированные системы управления (АСУ) народным хозяйством включают в свой состав вычислительный комп-леке (ВК) из двух ЭВМ, сопряженный с другими подсистемами По этим подсистемам в ЭВМ поступает большой объем информации, которьй заносится на общий внешний накопитель,, а по мере необходимости может считываться любой ЭВМ. Создание таких вычислительных комплексов приводит к увеличению производительности

и повьш1ению эффективности использования ресурсов как ВК, так и АСУ.

Цель изобретения - повьшхение быстродействия устройства за счет сокращения времени ожидания обменов и сокращение объема аппаратных средств.

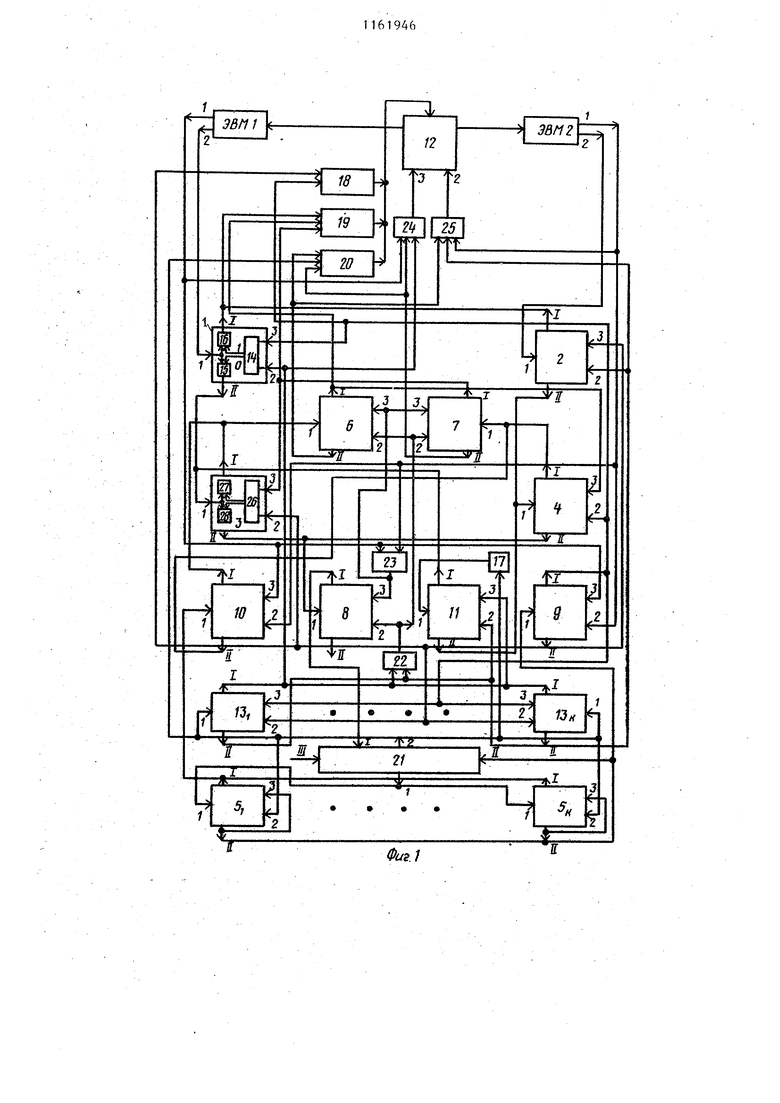

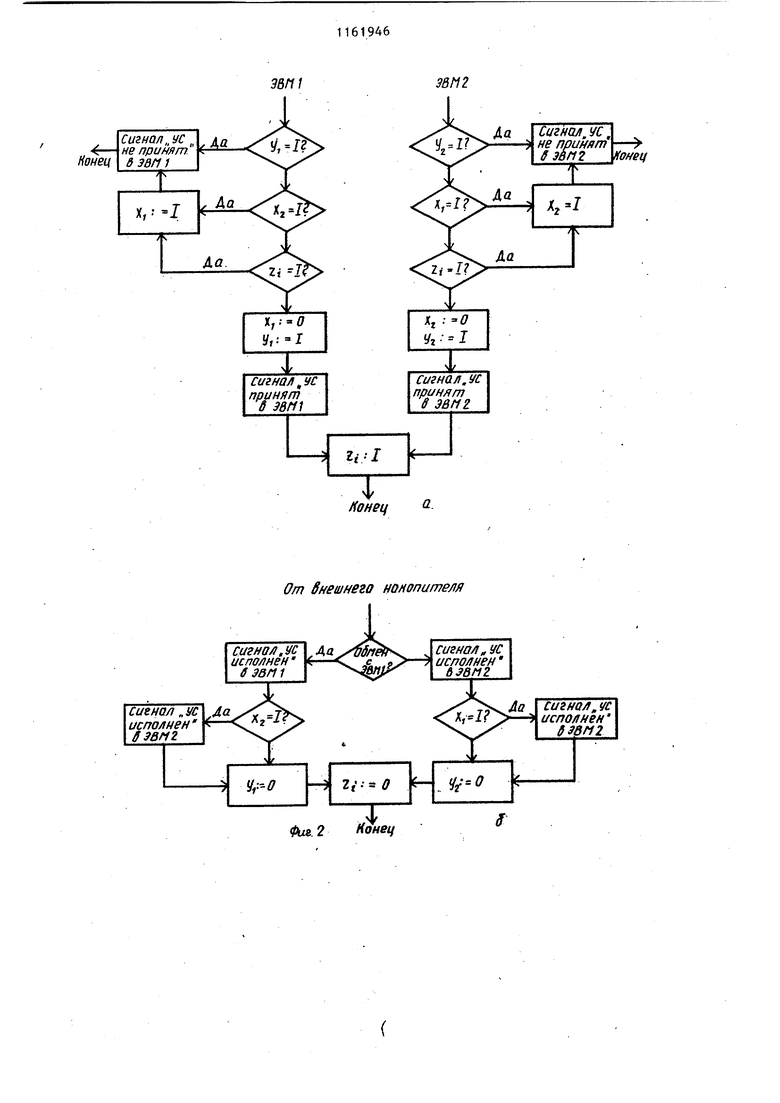

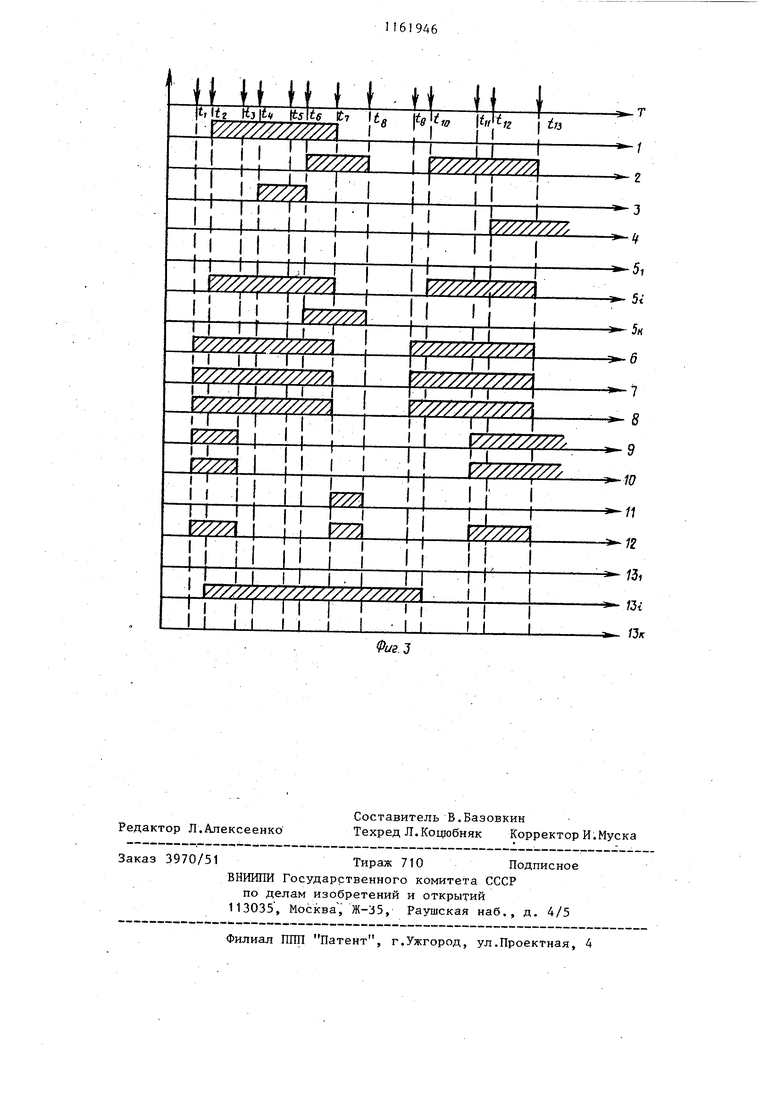

На фиг. 1 представлена блок-схема предлагаемого устройства для

управления доступом к памяти; на фиг 2 - логическая схема работы устройства управления по запросу на обмен с внешней памятью (2а) и по сигналу о завершении обмена

с внешней памятью (2б), поясняющая принцип функционирования устройства; на фиг. 3 - временная диаграмма состояния триггеров, поясняющая работу устройства управления. На фиг. 2 - приняты следующие обозначения: Y - признак занятости канала внешнего накопителя первой ЭВМ Y. - признак занятости канала внешнего накопителя второй ЭВМ; признак ожидания канала внешнего накопителя первой ЭВМ-, Х - признак ожидания кандла внешнего накопителя второй ЭВМ; 2 (1 Ii к) - признак занятости 1-го подканала, На диаграмме (фиг. 3) верхняя ось Т есть ось времени, а остальные оси помечены номерами блоков блок-схемь (фиг. 1). На каждой оси Яомеченной номерами блоков, заштрихован интервал времени, соответствующий пребыванию RS-триггера этого блока в состоянии 1. Моменты -t , помеченные вертикальными стрелками на оси времени, соответст вуют следующей последовательности событий: i -сигнал, поступающий на первый вход устройстваj t - сигнал, поступающий по второму входу устройства, на обмене i-м подкана лом внешней памяти; , сигнал, поступаю1ций на третий вход устройства; i. - сигнал, поступающий по четвертому входу устройства, на обмен с i-M подканалом внешней памят t5 - сигнал,-поступающий на третий вход устройства; t - сигнал, поступающий по четвертому входу устрой ства, на обнг-н с к-м подканалом вне ней памяти; i-,- сигнал от внешней памяти в блок коммутации о завершений обмена с i-м подканалом внешней памяти; -t g сигнал от внешней памяти в блока коммутации о завершении обмена с k-м подканалом внешней памятиj tj - сигнал, посту пающийонатретий вход устройства; - сигнал, поступающий по четве тому входу устройства, на обмен с i-M подканалом внешней памяти; , - сигнал, поступающий на первый вход устройства-, 2 сигна поступающий по второму входу устрой ства-, на обмен с i-м подканалом внешней памяти; - сигнал от вне ней памяти в блок коммутации о заве шении обмена с i-м подканалом внеш ней памяти. ; Устройство содержит первый ивторЬ блоки 1 и 2 контроля, первьй и второй блоки 3 и 4 анализа, первый регистр 5, первый, второй и третий бл ки 6, 7 и 8 памяти, первый - четверты дешифраторы 9-12, второй регистр 13, R5 -триггер 14, первый и второй элементы И 15 и 16, элемент 17 задержки, первый, второй и третий формирователи сигналов 18, 19 и 20, блок 21 коммутации, первый - четвертый элементы HJIIi 2225. Блок 3 анализа содержит RS -триггер 26 и два элемента И 27 и 28. Блоки 1 и 2 контроля, 3 и 4 анализа, 6, 7 и 8 памяти, дешифраторы 912, регистры 5 и 13 по устройству и внутренним функциональным связям идентичны и содержат по одному RSтриггеру 26 и по два элемента И 27 и 28, которые соединены так, как показано на блок-схеме в блоке 3 анализа. Второй выход третьего блока 8 памяти в предлагаемом устройстве не используется и может быть использован при дальнейших усовершенствованиях устройства, а здесь оставлен с целью унификации. Длительность задержки, реализуемой элементом 17, устанавливается равной или несколько более Длительности переключения триггера в третьем дешифраторе, так что поступление сигнала от блока коммутации на первый вход третьего дешифратора происходит после переключения триггера в дешифраторе 11. Устройство работает следующим образом. Пусть внешняя память имеет k подканалов, тогда первый и второй регистры 5 и 13 будут иметь по к блоков. Работа блока заключается в том, что сигнал, поступивший с первого входа блока на входы элементов И 15 и 16, может пройти только через тот элемент И, на другом входе которого уже есть сигнал от RS-триггера. Работа первого блока контроля отображает занятость . канала внешнего накопителя по выполнению запроса, поступившего по второму входу устройства. Если RS-триггер 14 в состоянии 1, то канал занят, а если RS-триггер 14 в состоянии О, то канал внешнего накопителя свободен. Второй блок 2 контроля вьтолняет те же функции, что и блок 1 контроля, но только по вьтолнению запроса, поступившего по четвертому входу устройства. Пусть первый и второй входы VCTройства управления подключены к первой ЭВМ, а третий и четвертый входы устройства - к второй ЭВМ. Сигнал, поступающий в устройство управления по первому или третьему входу, переводит триггера требуемых блоков в состояние, необходимое при работе с первой или второй ЭВМ соответственно, а сигнал, поступающий по второму или четвертому входу устройства, организует обмен первой или второй ЭВМ с внешней памятью. Пусть в исходном состоянии все триггеры находятся в состоянии О и первой ЭВМ необходимо произвести обмен информацией с i-м подканалом общей памяти. Тогда первая ЭВМ формирует и передает по первому входу устройства сигнал, который поступает на третьи входы первого и второго дешифратора 9 и 10, через третий элемент ИЛИ 24 на; третий вход четвертого дешифратора 12, что соответствует работе первой ЭВМ с каналом внешней памяти, через второй элемент ИЛИ 23 на третьи входы первого, второго и третьего блоков 6, 7 и 8 памяти, что соответствует прохождению сигнала из ЭВМ, Затем первая ЭВМ формирует сигнал на обмен с л-м подканалом общей памяти и передает его по второму входу устройства на первый вход первого блока 1 контроля. В зависимости от того, на каком элементе И блока 1 контроля имеется сигнал от КБ-триггера 14, запрос может пройти либо на первый выход, либо на второй. Если запрос проходит на первый выход, то второй формирователь 19 сигналов формирует сигнал и через четвертый дешифра тор 12 засылает его в первзто ЭВМ по первому выходу устройства управления. Если запрос проходит на втор выход, то он пересылается на первый вход первого блока 3 анализа. Если запрос из блока 3 выходит через пер вый выход, то через первьй блок 6 памяти поступает на третий вход вто рого блока 4 анализа и во второй формирователь 19 сигналов, который формирует сигнал и через четвертый дешифратор 12 засылает его в первую ЭВМ по первому выходу устройства управления. Если запрос выходит через второй выход, то через третий блок 8 памяти он поступает в блок 2 коммутации, который по адресу в зап росе определяет и запоминает номер требуемого подканала. Блок 21 коммутации передает запрос на первый вход первого регистра 5. Если i -и подканал занят, то сигнал выходит из первого выхода первого регистра 5 и через первый дешифратор 9 и первьй блок 6 памяти передается на третий вход второго блока 4 анализа и на вход второго формирователя 19 сигналов. Если подканал свободен, то сигнал выходит из второго выхода первого регистра 5, поступает на .третий вход i-ro блока первого регистра 5, тем самым блокируя обращение второй ЭВМ к данному подканалу, на второй вход блока 21 коммутации и через второй дешифратор 10 на третий вход первого блока 1 контроля, на второй вход второго блока 4 анализа и на первьй формирователь 18 сигналов, который формирует сигнал и через четвертый дешифратор 12 и первый выход устройства управления передает его в первую ЭВМ. Блок 21 коммутации, получив сигнал от i-ro блока первого регистра 5, подключает шины интерфейса i-ro подканала к шинам первой ЭВМ. После завершения обмена информацией в блок 21 коммутации из -го подканала поступает сигнал Конец переписи. Блок 21 коммутации засылает сигнал на второй вход i-ro блока первого регистра 5, тем самым снимая блокировку обращения к данному подканалу, через -й блок второго регистра 13 на третий вход третьего дешифратора 11, на второй вход первого блока 1 контроля, через первый элемент ИЛИ 22 на вторые входы первого 6, второго 7 и третьего 8 блоков памяти, через третий элемент ИЛИ 24 на третий вход четвертого дешифратора 12 .и на-третий формирователь 20 сигналов, которьш формирует сигнал и через четвертый дешифратор 12 засылает его в первую ЭВМ по первому вькоду устройства управления, а также через элемент 17 задержки и третий дешифратор 11 на первьй вход первого блока 3 анализа. Если сигнал из первого блока 3 анализа выходит по второму выходу, то устройство управления заканчивает обслуживание данного запроса, а если с первого выхода, то сигнал Через первьй блок- 6 памяти и четвертый эле7

мент ИЛИ 25 поступает на второй вход четвертого дешифратора 12, а также через первый блок 6 памяти на третий формирователь 20 сигналов, который формирует сигнал и через четвертый дешифратор 12 засылает его во вторую ЭВМ по второму выходу устройства управления. На этом устройство для управления доступом к памяти заканчивает обслуживание данного запроса.

Обслуживание запроса от второй ЭВМ производится аналогично обслуживанию запроса от первой ЭВМ.

Предлагаемое устройство является достаточно простым по сравнению с прототипом и состоит из однотипнь1х блоков, практическая реализация которых не представляет трудностей.

Предлагаемое устройство управления выгодно отличается от прототипа тем, что обеспечивает одновременное обращение двух ЭВМ к разным подка468

налам общей внешней памяти, обеспечивает поочередное обращение двух ЭВМ к одному и тому же подканалу, вьфабатывает сигналы о принятии заявки на обмен и о-завершении обменов, вырабатываемых таким образом, чтобы обеспечить возможность исключения излишних запросов из ЭВМ к занятому подканалу, сокращает длительность ожидания обмена и вычислительных затрат на уровне высокоприоритетных канальных подпрограмм операционных систем, а это, в свою очередь, значительно расширяет функциональные возможности устройства по сравнению с прототипом и, следовательно, может более широко использоваться в составе вычислительных комплексов из двух ЭВМ, имеющих общую внещнюю память.

Применение предлагаемого устройства позволит значительно сократить объем аппаратных средств и время ожидания обменов.

)(онец

Сигнал,УС принят

S ЭВМ г

а.

| СПОСОБ РЕАБИЛИТАЦИИ ОБЛУЧЕННОЙ СКЕЛЕТНОЙ МЫШЦЫ В ЭКСПЕРИМЕНТЕ | 1996 |

|

RU2123833C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство управления доступом к общей памяти | 1977 |

|

SU750490A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-15—Публикация

1983-01-11—Подача