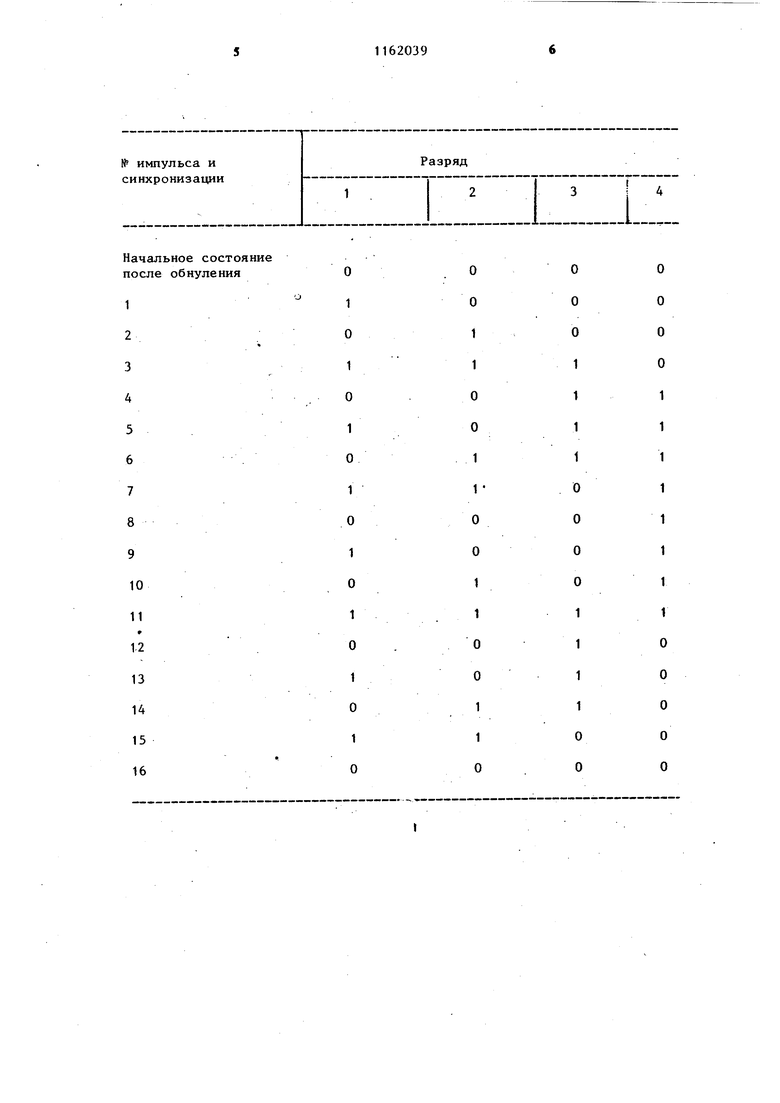

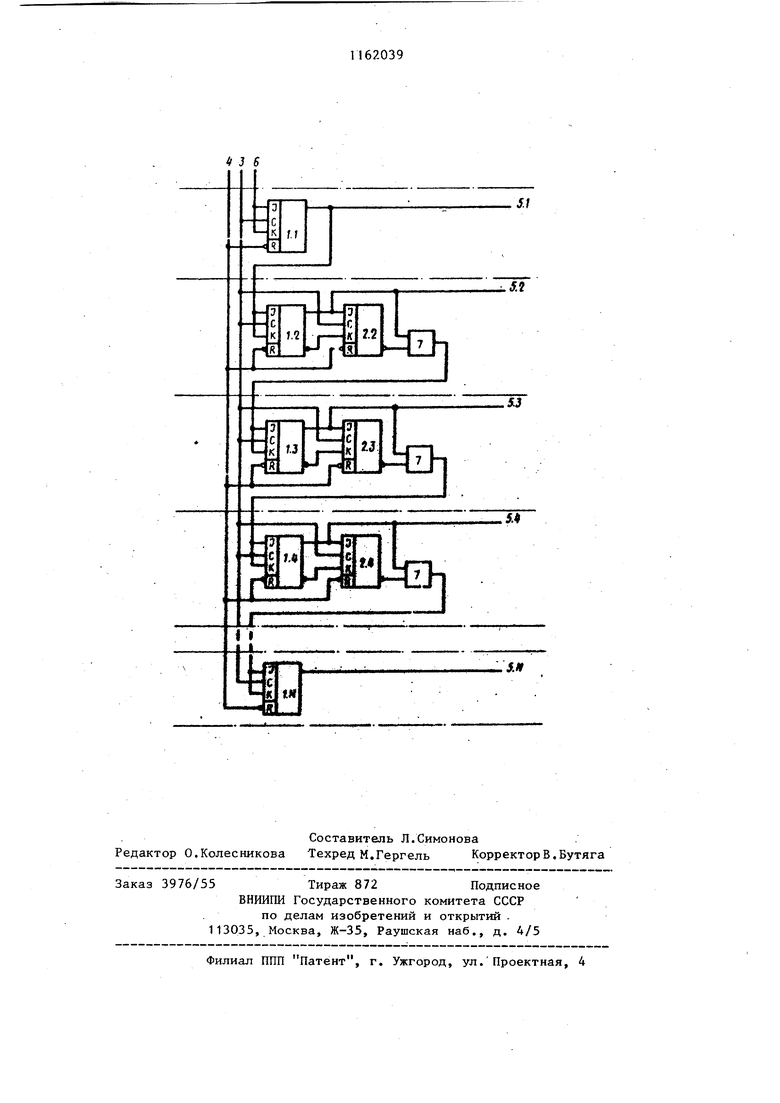

Изобретение относится к оЬласти цифровой вычислительной техники, а именно классу счетчика с произвольным порядком счета, и может быть использовано в устройствах проверки быстродействующих многоразрядных цифровых блоков, например. Таких как логический анализатор или запоминающее устройство. Известен счетчик на основе регист ра сдвига, в котором прямой и инверс ный выходы триггера последнего разряда соединяются с инверсным и прямым информационными управляющими входами первого разряда соответственно lj . Недостатком известного счетчика является больщая избыточность, т.е. он имеет относительно малое количество устойчивых состояний при заданном числе разрядов. Наиболее близким по технической сущности к данному является счетчик, содержащий шину синхронизации, шину сброса и N-разрядов, каждый разряд, кроме первого и последнего, содержит Т-триггер и D-триггер, первый и последний разряды содержат по одному Т-триггеру, синхровходы всех D-триггеров и Т-триггера первого разряда соединены с шиной синхронизации, D-вход каждого D-триггера соединен с прямым выходом Т-триггера своего разряда, шина сброса соединена с вх дами установки всех триггеров 2j. Недостатком известного устройств является относительно низкое быстро действие. Цель изобретения - повышение быс .родействия. Поставленная цель достигается тем что в счетчик, содержащий шину синхронизации, шину сброса и N разрядов каждый разряд, кроме первого и после него, содержит Т-триггер и ti-триггер, первый и последний разряды содержат по одному Т-триггеру, синхровходы всех D-триггеров и Т-триггера первого разряда соединены с шиной синхронизации, D-вход каждого D-триггера соединен с прямым выходом Т-триггера своего разряда, шина сброса соединена с входами всех триггеров, в каждь разряд, кроме первого и последнего введен элемент И,первый вход которого соединен с инверсным выходом Dтриггера своего разряда, второй вход с прямым выходом Т-триггера своего азряда, а выход - с Т-входом Т-триггера последующего разряда, синхровходы Т-триггеров всех разрядов, наиная со второго, соединены с шиной синхронизации, прямой выход Т-триггера первого разряда соединен с Т-вхоом Т-триггера второго разряда, Твход Т-триггера первого разряда соединен с шиной логической единицы. Т и D-триггеры выполнены на 1-Ктриггерах. На чертеже представлена схема счетчика. Устройство содержит Т-триггеры -1.1 - 1.N, D-триггеры 2.2 - 2.4. шину 3 синхронизации, шину 4 сброса, выходную шину 5.1-5.N разряда, щину 6логической единицы, элемент 7 И. Счетчик содержит в первом и последнем разряде один Т-триггер, а в остальных Т- и D-триггеры, С-входы которых соединены с шиной 3 синхронизации, а R-входы - с шиной 4 сброса, причем прямые выходы Т-триггеров всех разрядов соединены с соответствукядими выходными шинами 5 разрядов, Т-вход триггера первого разряда соединен с шиной 6 логической единицы, а его прямой вькод - с Т-входом триггера второго разряда, каждый разряд счетчика, кроме первого и последнего, содержит элемент 7И, первый вход которого соединен с инверсным выходом D-триггера разряда, второй вход - с прямым вьгходом Т-триггера разряда, а выход - с Твходом Т-триггера последующего разряда, в каждом разряде, кроме первого и последнего, прямой выход Т- триггера соединен с D-входом D-триггера этого же разряда, при этом Ти D-триггеры вьтолнены на ЗК-триггерах; Т-вход получается при 3 К, а D-вход получается при 3 К. Перед началом работы на R-входы триггеров по шине 4 приходит сигнал сброса нулевым уровнем, триггеры устанавливаются в нулевое состояние. Устройство работает следукнцим образом. По шине синхронизации 3 на С-входы триггеров приходят импульсы счета. На Т-вход 1ГК(Т) триггера первого разряда приходит уровень 1. ЗК(Т)-триггер первого разряда меняет свое состояние по концу каждого импульса синхронизации. Сигнал с прямого выхода 7К(Т)-триггера первого разряда поступает на выход 5 разряда и на Т-К-входы trK(T)-триггера второго разряда. В моменты, когда уровень сигнала на и -К-входах 3 К (Т)-триггера второго разряда единичный, по концу импульса проТ1сходит переключение состояния триггера. Сигнал с прямого выхода .1К(Т)-триггера второго разряда с частотой в два раза ниже, чем на выходе первого разряда, поступает на выходную шину 5 второго разря да и на вход элемента 7 второго разряда. Сигналы с прямого и инверсного выходов триггера поступают на (1-к)-входы 3K(D)-триггера второго разряда, а так как на С-входы fK(D)триггера второго разряда также поступают импульсы синхронизации, то он повторяет состояние 1ГК(Т)-триггера второго разряда с задержкой на один такт синхронизации. Сигнал с инверсного вькода ОК(D)-триггера 2 второго разряда .поступает на второй, вход элемента 7 второго разряда. На выходе элемента 7 второго разряда формируют сигналы, положительный фронт которых привязан к положитель ному фронту сигнала на выходе ЗК(Т)триггера второго разряда, а длителькость равна одному такту синхронизации. Эти сигналы поступают на 0-Квход ЗК(Т)-триггера третьего разряда, разрешая его переключение. В моменты, уровень на выходе эле мента 7 второго разряда единичен, по концу импульса синхронизации происходит переключение состояния (Т)триггера третьего разряда. Сигнал с прямого выхода ОК(Т)-триггера третье го разряда, имеющий частоту в два раза ниже, чем на выходе второго раз ряда, и фронты, сдвинутые на одинС такт синхронизации относительно фронтов на выходе второго разряда, поступает на выход третьего разряда и на вход элемента 7 третьего разряд Сигналы с прямого и инверсного вы ходов ЦК(Т)-триггера третьего разряда поступают на 1г-К(0)-вход соответственно ЗК(В)-триггера третьего разряда, при этом на его выходах повто ряется состояние ЗК(Т)-триггера с задержкой на один такт синхронизации Сигнал с инверсного выхода 3K(D)триггера третьего разряда поступает. 394 на второй вход элемента 7 третьего разряда. На выходе элемента 7 третьего разряда формируются сигналы единичного уровня, положительный фронт которых привязан к положительному фронту сигналов на выходе ЗК(Т)-триггера третьего разряда, а длительность равна одному такту синхронизации, Этот сигнал поступает на (Т)-вход ЗК(Т)-триггера четвертого разряда, Работа четвертого и последующих разрядов происходит так же, как и третьего, В последнем разряде .IK(D)-триггер отсутствует, так как в нем не требуется формировать сигнал разрешения переключения для последующего разряда. Сигнал на выходной шине 5 каждого разряда предложенного счетчика имеет частоту в два раза ниже, чем на выходной шине 5 предыдущего разряда, а его фронты сдвинуты на один такт синхронизации относительно положительного фронта сигнала на выходной шине 5 предьщущего разряда. Код на выходах счетчика для четырех разрядов привед в таблице. Технико-экономический эффект данного устройства связан с большим быстродействием, так как в нем, как и в счетчиках на основе регистра сдвига, быстродействие определяется только параметрами используемого счетного триггера и элемента И и не зависит от числа разрядов. Если же первые IK(Т)-триггеры выполнить , с двумя tl-входами и двумя К-входами, то элемент И становится ненужным и быстродействие счетчика будет определяться только быстродействием используемых триггеров. Счетчикимеет регулярную структуру, т.е. можно выполнить первый последний разряд так же, как и стальные, с двумя триггерами и элементом И (это на работу счетчика не повлияет). При этом из нескольих однотипных малоразрядных счетиков, например четьфехразрядньк, ожно построить без использования ополнительных элементов счетчик с . юбым количеством разрядов и таким е быстродействием, как у калоразядного.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации обмена микропроцессора с памятью отображения | 1989 |

|

SU1786489A1 |

| Устройство для синхронизации вычислительной системы | 1987 |

|

SU1495773A1 |

| Устройство для контроля передачи информации | 1984 |

|

SU1251083A1 |

| Многоканальный распределитель | 1988 |

|

SU1569970A1 |

| Устройство микропрограммного управления с контролем | 1990 |

|

SU1805466A1 |

| Делитель частоты с целочисленным коэффициентом деления | 1983 |

|

SU1095414A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1988 |

|

SU1554153A1 |

| Устройство для контроля управляющих сигналов микропроцессора | 1989 |

|

SU1656536A1 |

1. СЧЕТЧИК, содержащий шину синхронизации, шину сброса и N разрядов, каждый разряд, кроме первого и последнего, содержит Т-триггер и D-триггер, первый и последний разряды «одержит по одному Т-триггеру, синхровходы всех D-триггеров и Ттриггера первого разряда соединены с шиной синхронизации, D-вход каждого D-триггера соединен с прямым выходом Т-триггера своего разряда, шина сброса соединена с входами установки всех ,триггеров, отличающийся тем, что, с целью повышения быстродействия, в каждый разряд, кроме первого и последнего, введен элемент И, первый вход которого соединен с инверсным выходом D-триггера CBoerot разряда, второй вход - с прямым выходом Т-триггера своего разряда, а выход - с Т-входок Т-триггера последующего разряда, синхровходы Т-триггеров всех разрядов, начиная со второго, соединены с шиной синхронизации, прямой выход Т-триггера первого разряда соединен с Т-входом Т-триггера второго раз(Л ряда, Т-вход Т-триггера первого разряда соединен с шиной логической единицы. 2. Счетчик по п. 1, отличающийся тем, что Т- и D-триггеры выполнены на 3-К-триггерах.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Букреев И.Н., Мансуров Б.М | |||

| и Горячев Б.Н | |||

| Микроэлектронные схемы цифровых устройств | |||

| М., Советское радио, 1973, с | |||

| Универсальный двойной гаечный ключ | 1920 |

|

SU169A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Счетчик Папушина | 1978 |

|

SU890943A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-06-15—Публикация

1983-12-26—Подача