Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах на основе микро- ЭВМ для быстрого заполнения памяти отображения.

Известно устройство для адресации памяти отображения -см. Егоров В.П., Процак A.M., Семенов П.А. Цветная графика в мик- роЭВМ Электроника 60 и Электроника ЕЦ-80 Микропроцессорные средства и системы, 1987 г., № 4, с. 47-54, рис. 1, содержащее регистр адреса, блок управления и позволяющее в тех интервалах времени,- когда память отображения свободна от регенерации изображения/ осуществлять к ней поступ о-т микропроцессорами осуществлять обмен, адресуя содержимое памяти отображения посредством регистра адреса. При обращении к каждой ячейке памяти

микропроцессор предварительно выставляет ее адрес на регистре. Следовательно, учи- тывая соизмеримость времени установки .адреса и самого обращения, такая организация существенно уменьшает быстродействие устройства.

Известно также устройство по авт.св. № 1160409, G 06 F 9/36, 1985, содержащее кубы памяти объемом 64 кбайт каждый, шины адреса данных управления, дешифратор адреса, причем выход дешифратора подключен к синхровходу первого регистра, дешифратор команд с последовательно подключенной к нему цепочкой из элемента И, триггера, элемента задержки и второго элемента И, выход которого подключен к синхровходу второго регистра, последовательно соединенного с первым, причем второй регистр выбирает требуемый куб при

VI

00

Ј

00 Ч)

помощи коммутатора Номер требуемого куба памяти предварительно перезаписывается из аккумулятора процессора в первый регистр, а затем следует переход в требуемую ячейку заданного куба, адрес которого заносится во второй регистр. При этом устройствоне. позволяет осуществлять быструю пересылку информации из одного куба ,& другой пр и программном нахождении в одном и том же кубе памяти, что снижает быстродействие устройства.

Ближайшим к заявляемому по своей технической сущности является устройство по авт.св. СССР № 1238072, G 06 F 9/36, 1986 г. Оно осуществляет адресацию в микропроцессорных системах с большим объемом памяти и содержит шины информации, адреса и управления, дешифраторы команд и адреса, три регистра, два триггера, элемент задержки, формирователь и блоки памяти. Доступ к желаемому кубу памяти, как .к хранящимся в нем данным, так и к самой программе, осуществляется за счет предварительной установки номера куба на регистрах, азатем после аппаратной дешифрации заданного набора команд следует выборка- запись а заданный куб данных, либо переход программного счетчика в область данного куба. Такая структура позволяет осуществлять быструю пересылку информации из одного куба памяти в другой, сохраняя при . этом программное нахождение в одном и том же кубе памяти. ..

Недостатком известных устройств является их жесткая установка на стандартное время чтения-записи всех кубов памяти. Их организация не предусматривает возмож- ности согласования, например, цикла записи от микропроцессора, при запоминании памяти отображения, с ее циклами выборки для отобра кейИ5Гочёрёднь1х элементов разложения изображения (ПЭЛ). что, пpй:пoдo- . бном обмен ёГ преКятстеуе достижению 7 максимальной скорости заполнения памяти

отображения.

, Цель изобретения - расширение области применения устройства за счет обеспе- .. ченйя возможности разделения во времени J ре жйм6в записй и считывания памяти ото бражения. . ..:.

ПоставЛё ййай цень достигается тем, что в устройство, содержащее элементы И-НЕ и ИЛИ-НЕ, два дешифратора и три триггера, вход устройства дли подключения к выходу сброса ШйнУ уггр авпения микропроцессора Соединен с первым входом сброса первого триггера, инверсный выход которого соединен с первым входом элемента ИЛИ-НЕ, выход которого -выход устройства для подключения к входу признака блокировки шины управления, вход устройства для подключения к шине данных подключен ко вхэ- ду первого дешифратора, к первому разряду шины данных - к прямому входу элемента

И-НЕ, выход которого соединен с входам сброса второго триггера, выход которого с;о- . единен с информационным входом третьего, прямой выход которого соединен Со вводом установки второго, а вход синхронизаций подключен ко входу для подключения кТлетэвому выходу синхронизации шины управления, входы для подключения к выходам строба состояния и записи которой подключены соответственно к инверсному

входу элемента И-НЕ и к стробирующейу

входу второго дешифратора, информаций нный вход которого подключен ко входу уЈтройства, дли подключения к шине адреса,

- .вход устройства для подключения к выходу

записи шины управления подключен ко в|о- рому входу сброса первого триггера и второму входу элемента ИЛИ-НЕ, введены второй элемент И-НЕ и четвертый - восьмой триггеры, инверсный выход третьего триг|-ера Соединен с первым входом второго эЛе- мента И-НЕ, выход которого соединён) с информационным входом пятого триггера, выход которого соединен со входом ycjra- новки первого, выход сброса шины управрения соединен со входом сброса четвертого, .выход которого соединен со вторым вхофм второго элемента И-НЕ, выходы первогб и второго дешифраторов подключены со от- ветственно к третьему входу второго элемента Й-НЕ и синхровходу четв.ертбго

триггера, синхровход которого подключен

ко входу устройства для подключения ко

второму разряду шины данных, первый Јы ход синхронизации шины управления Соединен с синхровходом пятого, выход элемента ИЛИ-НЕ - со входом сброса Ыес- того триггера, прямой и инверсный выходы которого подключены соответственно к ры- ходу устройства для подключения к вхЬду

признака готовности шины управлениями к информационному входу седьмого трите- ра, выход которого подключен к Выходу устройства для подключения к входу разрешения записи памяти отображен и

к информационному входу и входу сброса восьмого, выход которого соединён со ихо- дом сброса седьмого и установки шестого триггера, второй выход синхронизации шины управления подключён к синхровходам

седьмого и восьмого триггеров...

Учитывая, что обеспечивающий загэуз- ку памяти отображения серийно выпуссае- мый графический контроллер цля микроЭВМ Электроника 60 и Элёктроника НЦ-80 не отвечает требованием должного максимального быстродействия обмена, а прочие известные устройства характеризуются отсутствием возможности согласования цикла записи с быстродействием конкретного куба памяти, что ведет, при стандартном выполнении чтения-записи, к недостижимости максимально возможного быстродействия, причем основным показателем обмена с памятью отображения является скорость выполнения этой операции, введение в устройство таких новых существенных признаков, как пять триггеров, второй элемент И-НЕ и новая организация взаимодействия между элементами устройства, позволяет расширить область применения устройства за счет обеспечения возможности разделения во времени режимов записи и чтения при организации циклической выборки очередного ПЭЛ, совмещенного с возможностью записи ПЭЛ от микропроцессора по адресу, указанному командой пересылки заданного ПЭЛ. Достижение максимальной скорости программного заполнения памяти без прерывания отображения состоит в организации тактированного построения выборки очередного ПЭЛ из памяти отображения первой фазе такта с возможностью записи ПЭЛ во второй фазе по адресу, выставляемому микропроцессором в команде пересылки заданного ПЭЛ. За счет такой организации учитывая при этом исключение предварительной записи адреса в буферный регистр, длительность обмена с памятью отображения сокращается почти вдвое.

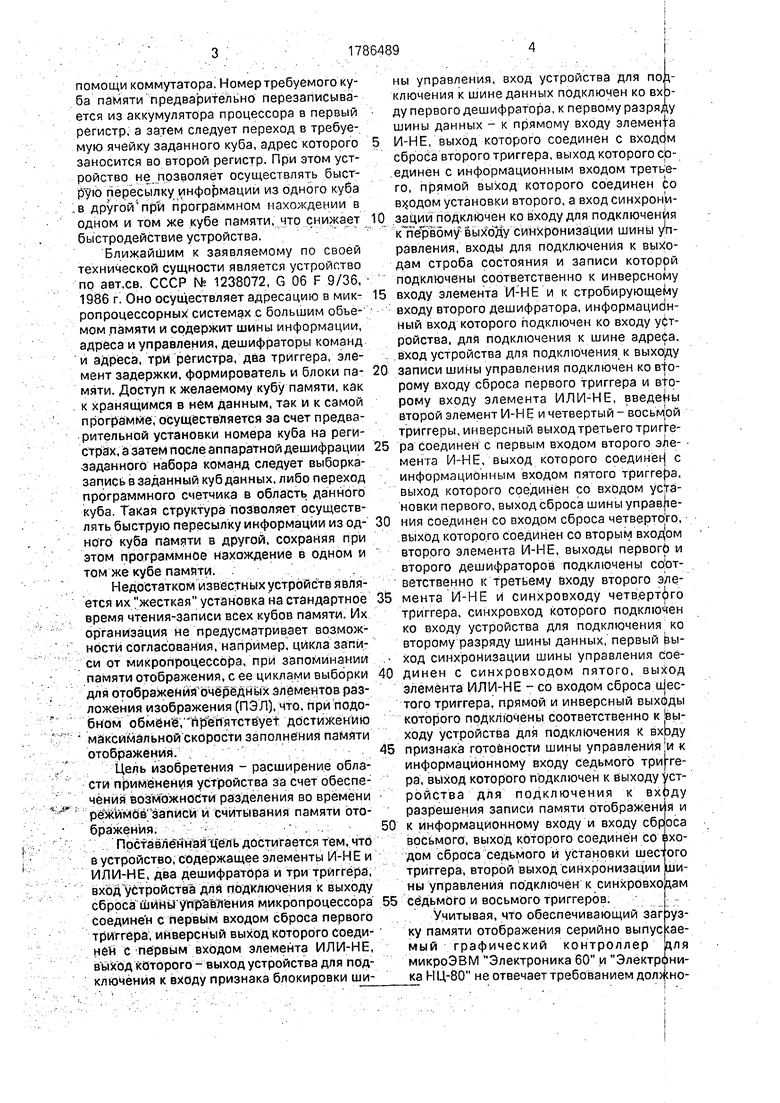

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 раскрыта функциональная схема памяти отображения; на фиг.З приведены временные диаграммы работы устройства.

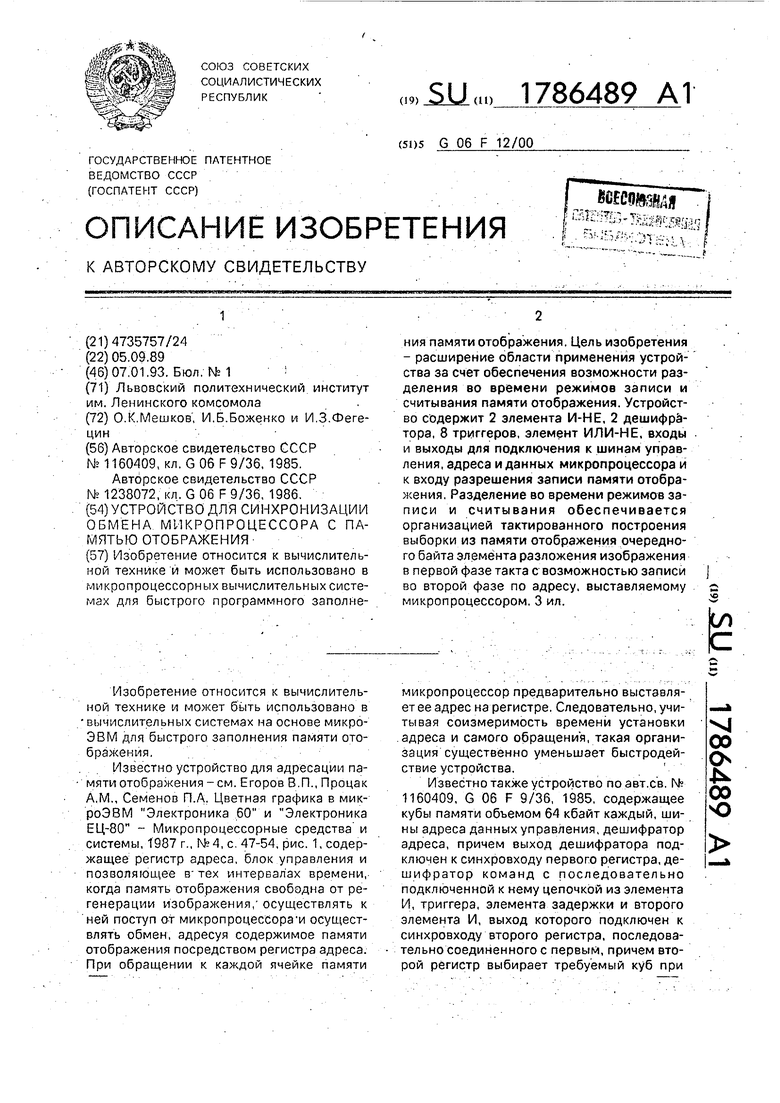

Устройство содержит (фиг.1) первый элемент И-НЕ 1, первый 2 и второй 3 дешиф- раторы, элемент ИЛИ-НЕ 4, первый-третий триггеры 5-7, второй элемент И-НЕ 8, чет- вертый-восьмой триггеры 9-13, вход 14 для подключения к выходу сброса шины управления микропроцессора (ШУ), входы 15, 16 для подключения к шинам, соответственно, данных (ШД) и адреса (ТА) микропроцессора, входы 17, 18 для подключения, соответственно, к первому и второму разрядам ШД, входы 19, 20 для подключения, соответственно, к выходам строба состояния и записи во внешнее устройство ШУ, входы 21,22 для подключения, соответственно, к первому и второму выходам синхронизации ШУ, вход 23 для подключения к выходу записи в память ШУ, выходы 24, 25 для подключения ко входам признаков соответственно блокировки и готовности ШУ. выход 26 для подключения ко входу разрешения записи памяти отображения и блок 27 памяти отображения.

Прямой выход первого элемента И-НЕ 1 подключен ко входу 17 устройства для подключения к первому разряду ШД, инверсный - ко входу 19 устройства для подключения к выходу строба состояния ШУ, а выход - ко входу сброса второго триггера 6. Информа0 ционные входы первого 2 и второго 3 дешифраторов подключены ко входам 15, 16 устройства для подключения, соответственно, к ШД, ША, а выходы - к третьему входу второго элемента И-НЕ 8 и синхровходу чет5 вертого триггера 9. Стробирующий вход дешифратора 3 подключен ко входу 20 устройства для подключения к выходу записи во внешнее устройство ШУ. Выход элемента ИЛИ-НЕ 4 подключен к выходу 24

0 устройства для подключения ко входу признака блокировки ШУ, и входу сброса шестого триггера 11, а входы, соответственно, первый - к выходу первого триггера 5, второй - ко входу 23 для подключения к выходу

5 записи в память ШУ и второму входу сброса триггера 5, первый вход сброса которого соединен со входом сброса триггера 9 и входом 14 устройства для подключения к выходу сброса ШУ, а вход установки - с

0 выходом пятого триггера 10. Вход установки и выход триггера 6 подключены, соответственно, к вы-ходу и информационному входу третьего триггера 7, синхровход которого подключен к синхровходу триггера 10 и вхо5 ду 21 устройства для подключения к первому выходу синхронизации ШУ, а выход - к первому входу элемента ИЛИ-НЕ 8, выход которого соединен с информационным входом триггера 10, а второй вход - с выходом

0 триггера 9, информационный вход которого подключен ко входу 18 устройства для под- ключения ко второму разряду ШД. Прямой выход триггера 11 подключен к выходу 25 устройства для подключения ко входу при5 знака готовности ШУ, вход установки - ко входу сброса-седьмого 12 и выходу восьмого 13 триггера, а инверсный выход - к информационному входу триггера 12, синхровход которого подключен ксинхровходамтригге0 ра 13, блока 27 памяти отображения и входу 22 устройства для подключения ко второму выходу синхронизации ШУ, а выход - к информационному входу и оходу сброса триггера 13 и к выходу 26 устройства для

5 подключения ко входу разрешения записи в блок 27. ..--.--.

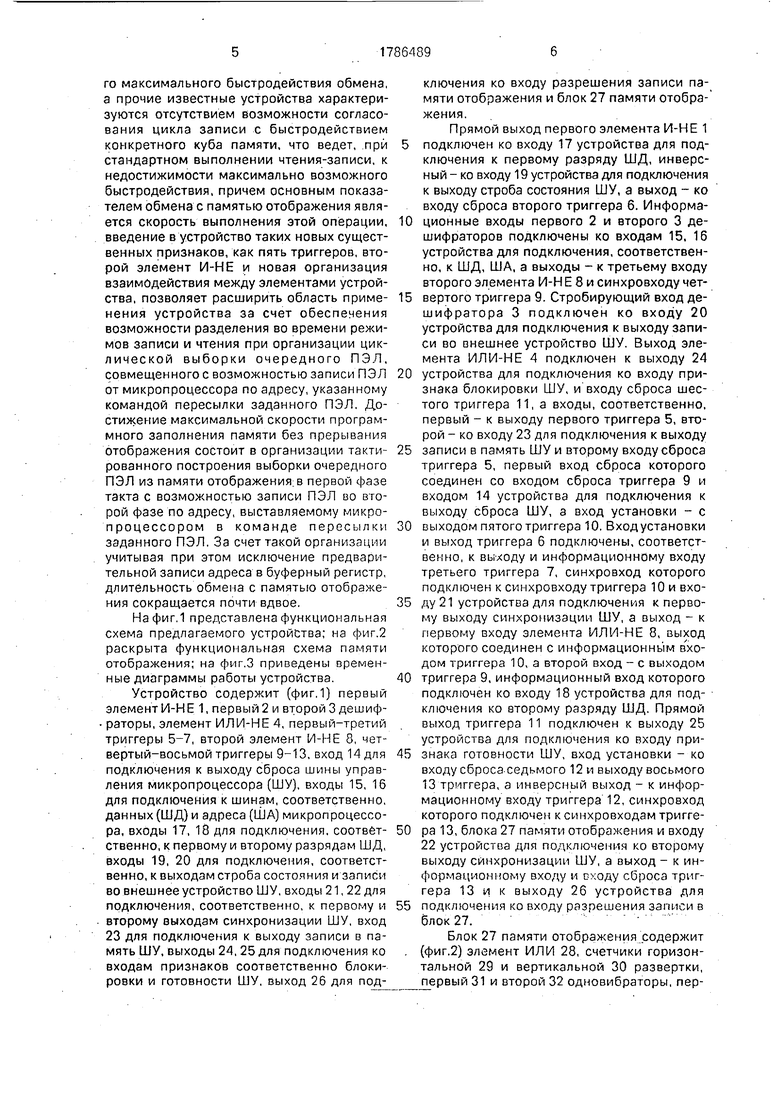

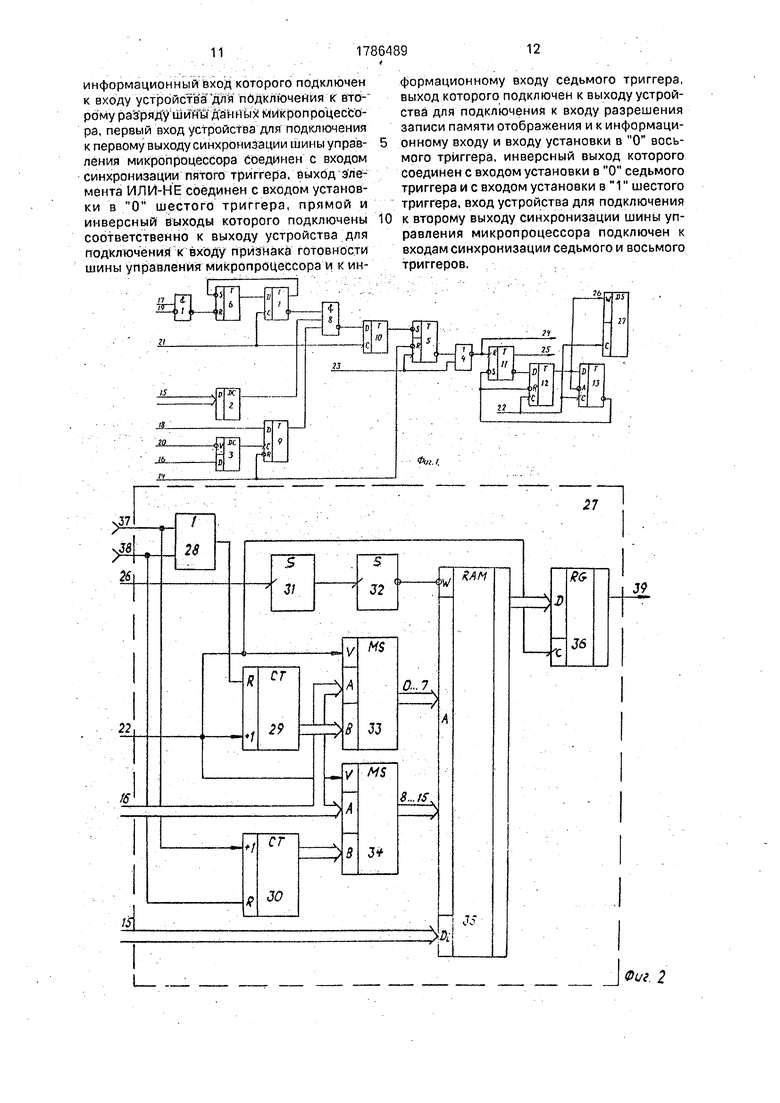

Блок 27 памяти отображения содержит . (фиг.2) элемент ИЛИ 28, счетчики горизонтальной 29 и вертикальной 30 развертки, первый 31 и второй 32 одновибраторы, первый 33 и второй 34 адресные коммутаторы, накопитель 35, сдвиговый регистр 36, входы строчного 37 и кадрового 38 гашения, выход 39. Информационный вход накопителя 35 подключен к ШД 15, первые информационные входы коммутаторов 34, 35 - к ША 16, управляющие входы коммутаторов объединены и подключены к суммирующему входу счетчика 25, синхровходу регистра 36 и второму выходу 22 синхронизации ШУ, а вход одновибратора31 -квыходу 26 разрешения записи устройства..

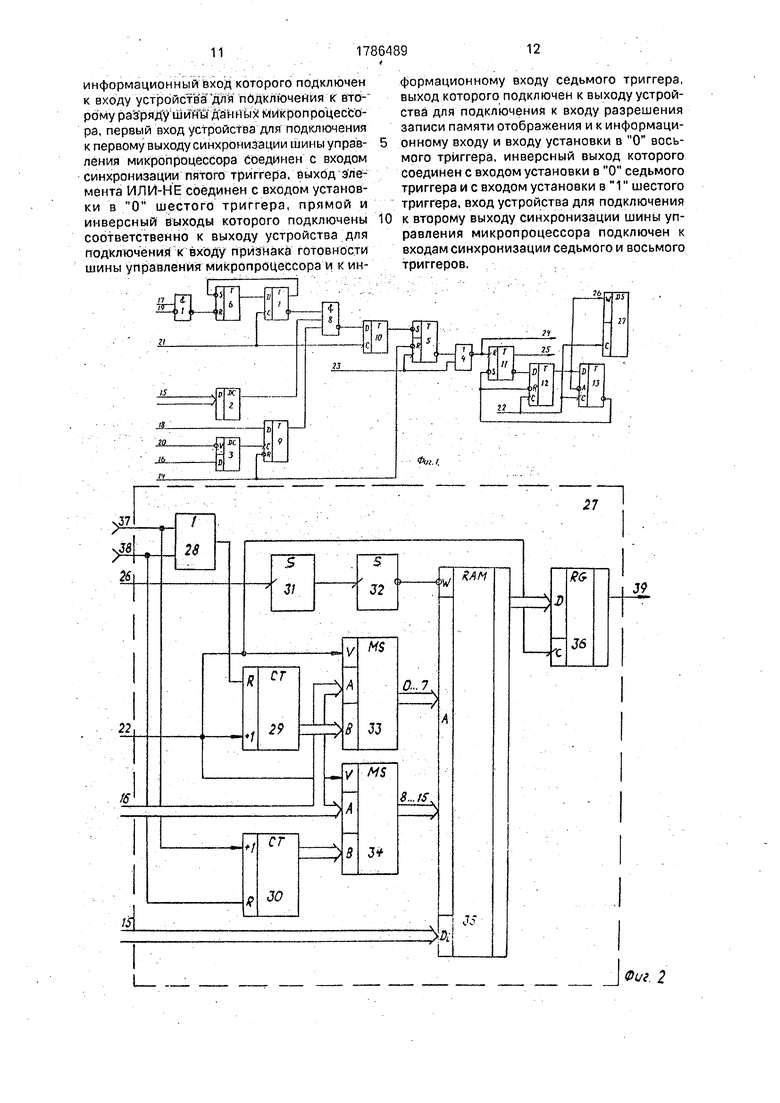

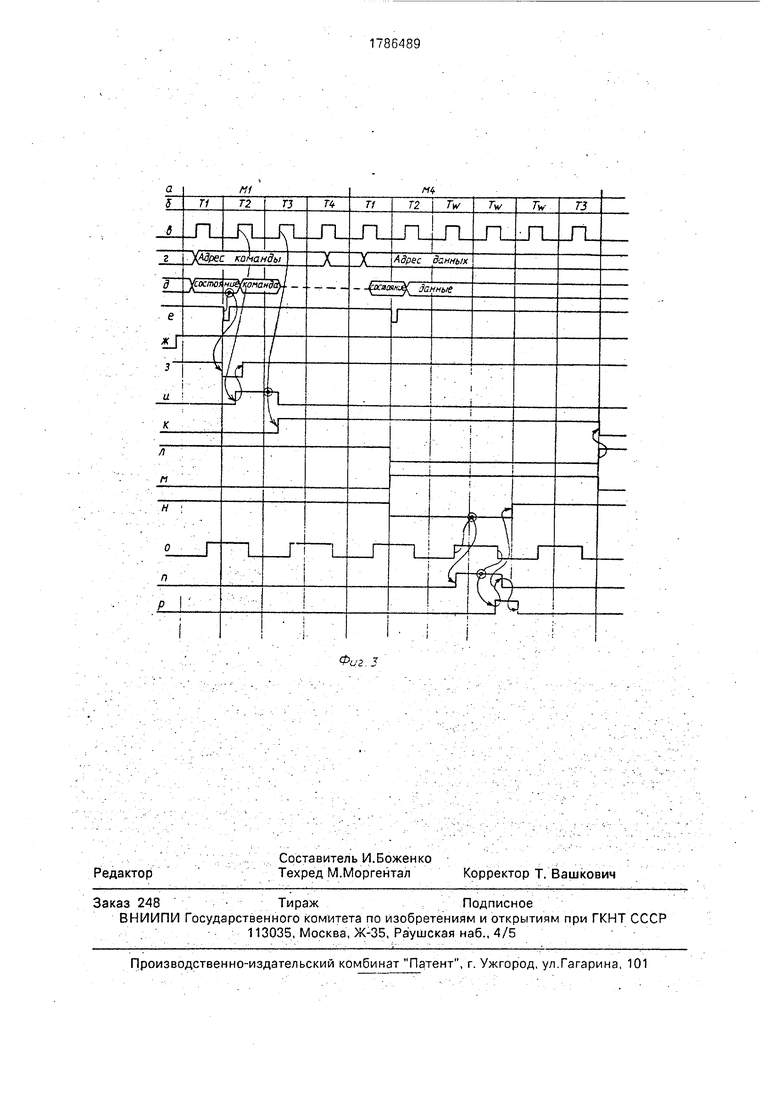

На фиг.З обозначены: а - машинные циклы: б-такты операций; в-сигналы такта Ф2 на входе 21 устройства; г - адреса А15- АО, поступающие по ША 16;. д - данные, поступающие по разрядам D7-DO ШД 15; е

- сигнал строба состояния на входе 19; ж - выход триггера 9; з - выход триггера 6; и - инверсный выход триггера и7; к - выход триггера 5; л - сигнал записи на входе 23; м

- сигнал блокировки системной памяти на выходе 24; н - сигнал готовности на выходе 25: о - синхросигнал на входе 22; и - сигнал разрешения записи на выходе 26; р - прямой выход триггера 13.

Состояние 1 на входе 22 соответствует участку возможности записи в память отображения и подключение к адресным входам этой памяти шины адреса процессора. Состояние О - участку выборки из памяти отображения, к адресным входам этой памяти подключен выход ее счетчика регенерации изображения,.

Реализованный вариант заявляемого устройства предназначен для организации загрузки памяти отображения объемом 256x256 ПЭЛ по программе процессора. В ШД и ШУ используются по 8 разрядов. Микропроцессор (на фиг. 1 не показан) содержит синхрогенератор КР580ГФ24, центральный процессорный элемент КР580ВМ80А и контроллер системной шины KP58QBK28. Про-чие элементы устройства выполнены на основе серии К555.

Устройство работает следующим образом,-.; .;.. .,,....-...

При включении микропроцессора производится системный сброс, поступающий по входу 14, в результате чего микропроцессор адресует исключительно свою системную память. Триггер 9 блокирует прохождение сигнала через элемент И-НЕ 8 по совпадению состояний триггера 7 и дешифратора 2. При этом триггер 10 устанавливается в 1, и состояние О триггера 5 через элемент ИЛ И-НЕ 4 снимает блокировку системной памяти на выходе 24. Дешифратор 2 выде- ляет из данных, поступающих по ШУ 15, команды пересылки в память. Дешифратор

3 определяет адрес выборки, по которому микропроцессор обращается к памяти отображения, как к внешнему устройству. Для организации записи очередногр

файла в память отображения микропроце0сор предварительно устанавливает триггер

9, чем устройство взводится в режим запо/jнения памяти отображения.. ;

В цикле М1 (фиг.З а) процессора устрой0 ством при помощи элементов И-НЕ 18, дешифратора 2 и триггера 5-7, 10 выявляется наличие этого цикла и запускается процес с записи в память. По сигналу с элемента сбрасывается триггер 6 (фиг.З з). Затем по

5 переднему фронту фазы Ф2 (фиг.З в) триггер 7 устанавливается в 1 (фиг.З и) и разрешЈ- ет, в момент выделения дешифратором 2 команды, формирование состояния О на выходе элемента И-НЕ 8, Это состояние з а0 носится по переднему фронту фазы Ф2.в триггер 10. Затем устанавливается триггер 5 (фиг.З к) и на выходе элемента ИЛИ-НЕ| 4 формируется сигнал записи в память от процессора, блокируя обращение к системной

5 памяти процессора. Одновременно по no/jo- жительному фронту этого сигнала сбрасывается триггер 11 (фиг.З н) и по выходу 25 процессору выдается сигнал его перевода в состояние ожидания и пропуска тактов

0 (фиг.З б), что необходимо для согласования быстродействия процессора и элементов системы. По истечении времени, выделенного для записи в память отображения, устройству по входу 22 поступает сигнал такта

5 записи в память (фиг.2 а). В результате триггер 12 формирует на выходе 26 сигнал раз- : решения записи в память отображения (фиг.2 п). По сбросу такта устанавливается триггер 13, после чего происходит сброс

0 триггеров 11 и 12, и по последующему такту сбрасывается триггер 13. В результате заданный процессором ПЭЛ записывается в память отображения. Состояние 1 на выходе триггера 11 указывает процессору на

5 выход из такта записи и завершение коман- ды. ..

По завершении пересылок всех требуемых ПЭЛ триггер 9 сбрасывается и память отображения становится недоступной про0 цессору.

Доступ к памяти отображения осуществляется следующим образом.

На первые информационные входы коммутаторов 33, 34 блока 27 с ША 16 поступа5 ют, соответственно, младший и старший байты адреса. Цепочка одновибраторов 31, 32 формирует сигнал записи в накопитель 35 из сигнала разрешения записи на выходе 26 устройства. Организация памяти отображения - двухпортовая: ко вторым информационным входам коммутаторов 33, 34 подключены выходы счетчиков 29, 30. Счетчики обнуляются по сигналам, соответственно, строчного и кадрового гашения на входах 37, 38 и инкрементируются по сигналам тактов записи в память на выходе 22 ШУ. Указанные такты задают периодические кванты времени, соизмеримые с машинным тактом процессора и отводящиеся ему для обращения к памяти отображения. Время, отводимое для отображения содержимого одной ячейки накопителя 35, соответствует периоду сигналов такта, нулевое значение которых соответствует выборке очередной ячейки, а единичное - возможности процессору обращаться к памяти отображения. В соответствии с этим управляются и коммутаторы 33, 34, Информация, считываемая из ячеек накопителя 35, поступает на выход 39, через сдвиговый регистр 36.

Таким образом осуществляется оперативное программное заполнение памяти отображения без прерывания отображения за счет тактированного построения выборки из памяти очередного ПЭЛ в первой фазе такта и записи во второй фазе по адресу, выставляемому процессором.

Такая организация позволяет достигнуть оптимального соотношения времени заполнения памяти и объема оборудования.

Организация прототипа не позволяет осуществлять состояние ожидания готовности памяти отображения для заполнения от процессора. Поэтому для выполнения прототипом этой задачи следует л ибо загружать память отображения во времени кадрового гашения, что заведомо увеличивает длительность обмена,либо увеличить время обращения к системной памяти до времени обращения к памяти отображения, что влечет за собой снижение производительности. Например, при организации памяти отображения на К565РУ5, учитывая буферизацию информации и время захвата, для адресации ПЭЛ требуется, как минимум, 1600 не при минимальном времени обращения к ячейке памяти 640 не.

В заявляемом же устройстве, благодаря двухпортовой организации памяти отображения, процессор способен работать с системной памятью с минимально возможным временем выборки, а с памятью отображения - со временем, ограниченным лишь минимальной длительностью выборки ПЭЛ в указанные 640 не, что и составляет выигрыш в быстродействии более чем в два раза.

Формула изобретения Устройство для синхронизации обмена микропроцессора с памятью отображения,

содержащее первый элемент И-НЕ, первый и второй дешифраторы, элемент ИЛИ-НЕ. с первого по третий триггеры, причем вход устройства для подключения к выходу сбро- са шины управления микропроцессора соединен с первым входом установки в О первого триггера, инверсный выход которого соединен с первым входом элемента УШИ-HE, выход которого является выходом

0 устройства для подключения к входу признака блокировки шины управления микропроцессора, вход устройства для подключения к шине данных микропроцессора подключен к входу первого дешифра5 тора, вход устройства для подключения к первому разряду шины данных микропроцессора подключен к прямому входу первого элемента И-НЕ, выход которого соединен с входом установки в О второго триггера,

0 выход которого соединен с информационным входом третьего триггера, прямой выход которого соединен с входом установки в 1 второго триггера, вход устройства для подключения к первому выходу синхрониза5 ции шины управления микропроцессора подключен к входу синхронизации третьего триггера, входы устройства для подключения к выходам строба состояния и записи во внешнее устройство шины управления мик0 ропроцессора подключены соответственно к инверсному входу первого элемента И-НЕ и к стробирующему входу второго дешифратора, информационный вход которого подключен к входу устройства для подключения

5 к шине адреса микропроцессора, вход устройства для подключения к выходу записи в память шины управления микропроцессора подключен к второму входу установки в О первого триггера и к второму входу элемен0 та ИЛИ-НЕ, о тли чающееся тем, что, с целью расширения области применения за счет обеспечения возможности разделения во времени режимов записи и считывания памяти отображения, устройство

5 дополнительно содержит второй элемент И- НЕ, с четвертого по восьмой триггеры, причем, инверсный выход третьего триггера соединен с первым входом второго элемента И-НЕ, выход которого соединен с инфор0 мационным входом пятого триггера, выход которого соединен с входом установки в 1 первого триггера, вход устройства для подключения к выходу сброса шины управления микропроцессора соединен с входом уста5 новки в О четвертого триггера, выход которого соединен с вторым входом второго элемента И-НЕ, выходы первого и второго . дешифраторов соединены соответственно с третьим входом второго элемента И-НЕ и с входом синхронизации четвертого триггера.

информационный вход которого подключен к входу устройсте а д7гя подключения к его- рому tfflti данных микропроцессо- ра, первый вход устройства для подключения к первому выходу синхронизации шины управления микропроцессора Соединен с входом синхронизации пятого триггера, выход элемента ИЛЙ-НЕ соединен с входом установки в О шестого триггера, прямой и инверсный выходы которого подключены соответственно к выходу устройства для подключения к входу признака готовности шины управления микропроцессора и к ин0

формационному входу седьмого триггера, выход которого подключен к выходу устройства для подключения к входу разрешения записи памяти отображения и к информационному входу и входу установки в О восьмого триггера, инверсный выход которого соединен с входом установки в О седьмого триггера и с входом установки в 1 шестого триггера, вход устройства для подключения к второму выходу синхронизации шины управления микропроцессора подключен к входам синхронизации седьмого и восьмого триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации памяти | 1990 |

|

SU1741142A1 |

| Устройство для отладки микропроцессорных систем | 1985 |

|

SU1285482A1 |

| Устройство для контроля микропроцессора | 1988 |

|

SU1599862A1 |

| Устройство для ввода информации | 1987 |

|

SU1531082A1 |

| Устройство для управления энергопитанием микропроцессорной системы | 1983 |

|

SU1201829A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1817096A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

Изобретение относится к вычислительной технике и может быть использовано в микропроцессорных вычислительных системах для быстрого программного заполнения памяти отображения. Цель изобретения - расширение области применения устройства за счет обеспечения возможности разделения во времени режимов записи и считывания памяти отображения. Устройство содержит 2 элемента И-НЕ, 2 дешифратора, 8 триггеров, элемент ИЛИ-НЕ, входы и выходы для подключения к шинам управления, адреса и данных микропроцессора и к входу разрешения записи памяти отображения. Разделение во времени режимов записи и считывания обеспечивается организацией тактированного построения выборки из памяти отображения очередного байта элемента разложения изображения в первой фазе такта с возможностью записи во второй фазе по адресу, выставляемому микропроцессором,3 ил. -г Ё

J

Фиг. 2

| Устройство для адресации памяти | 1984 |

|

SU1160409A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство адресации памяти | 1984 |

|

SU1238072A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-07—Публикация

1989-09-05—Подача