Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных систем.

Цель изобретения - повышение точности синхронизации нескольких ЦВМ,

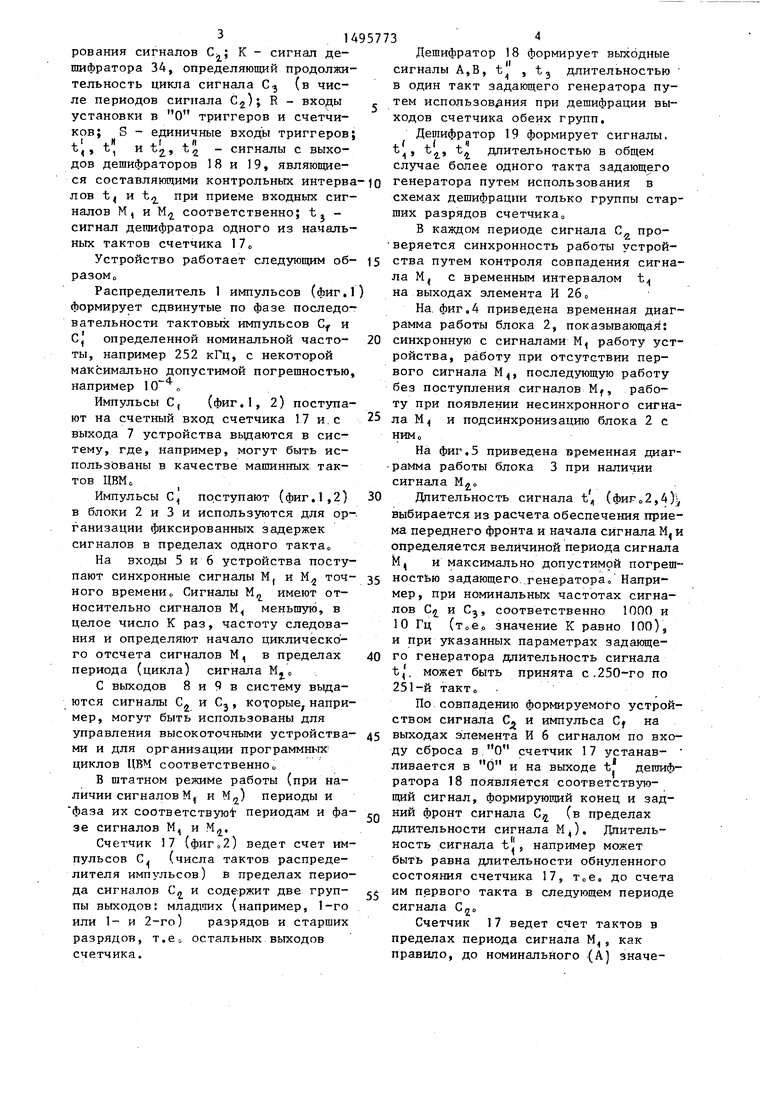

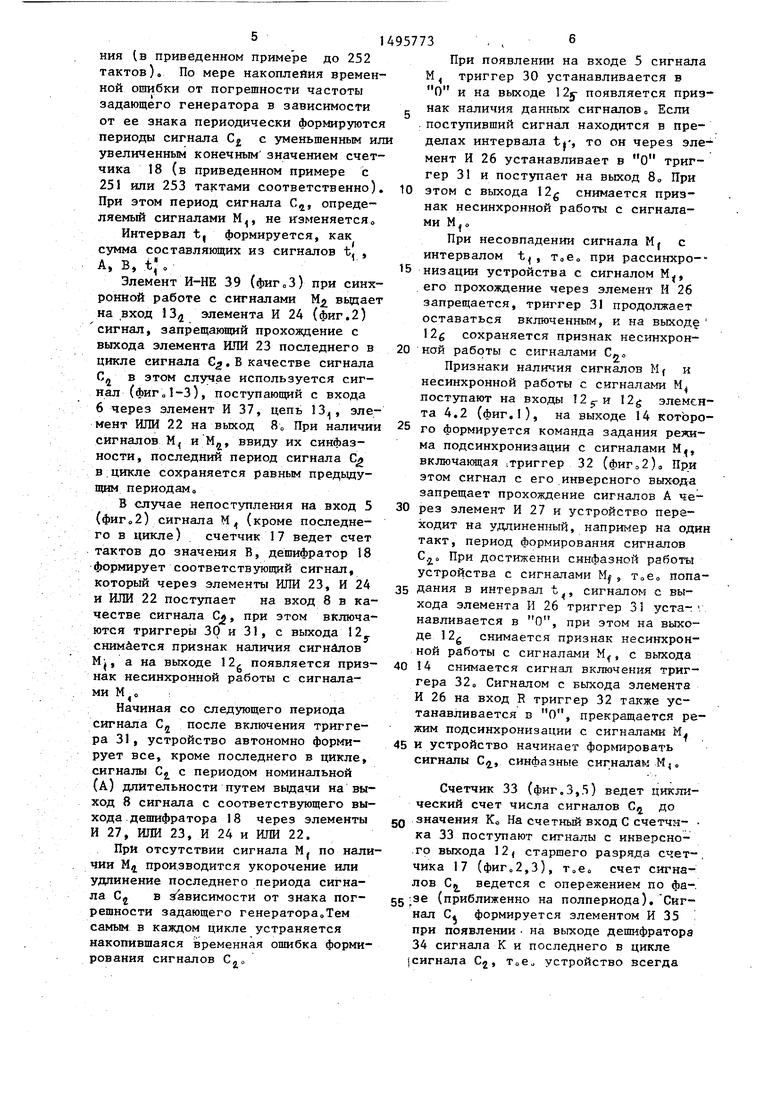

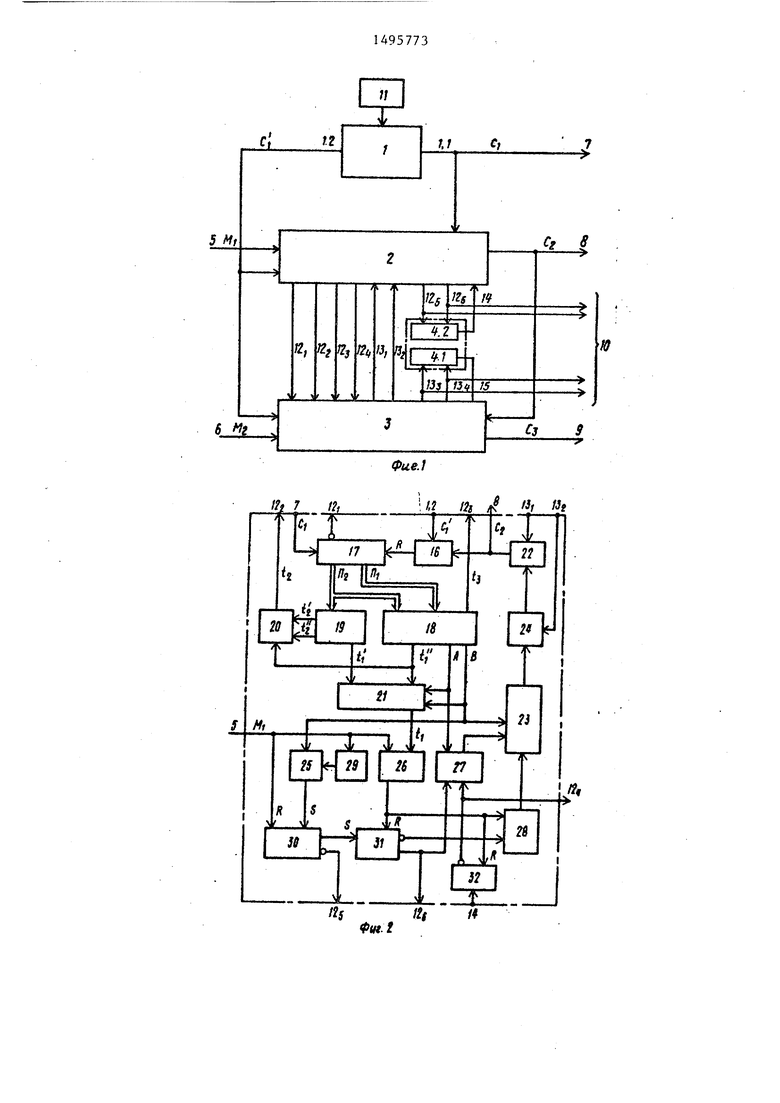

На фиго приведена структурная схема устройства; на фиго 2 - схема первого блока синхронизации с сигналами точного времени; на фиг,3 - схема второго блока синхронизации с сигналами точного времени; на фиг, 4 и 5 - временные диаграммы ра- боты первого и второго блоков синхронизации.

Устройство содержит распределитель 1 импульсов, первый 2 и второй 3 блоки синхронизации, группу элементов И 4 из первого и второго эле- . ментов 4,1 и 4.2, вход 5 сигналов точного времени, вход 6 запуска сигналов точного времени, первый 7,второй 8 и третий 9 тактовые выходы устройства, группу 10 выходов сбоя устройства, задающий генератор 11, выходы 2 - 12g первого блока 2, выходы 3 ,-13(j второго блока 3 синхронизации, вьпсоды 14 и 15 элементов И группы

llOJo

Блок 2 содержит элемент И 16,счетчик 17, дешифраторы 18 и 19} элементы ИЛИ 20 - 23, элементы И 24 - 28, элемент НЕ 29, триггеры 30 - 32о

Блок 3 содержит счетчик 33, дешифратор 34, элементы И 35-38, элемент И-НЕ 39, элемент ИЛИ 40, триггеры 41-43, триггер 44, элемент И 45.

На фиг о 1-5 приведены следующие обозначения сигналов и входов (выходов) элементов: С - синхронизирующие входы триггеров; С , - С - выходные сигналы устройства; А,В - сигналы дешифратора 18, определяющие соответственно номинальную и удлиненную продолжительность периодов формиX

сл -л

vl

31495773

рования сигналов К - сигнал дешифратора 34, определяющий продолжительность цикла сигнала С (в числе периодов сигнала С); R - входы установки в О триггеров и счетчи- S - единичные входы триггеров;

I . л

Дешифратор 18 формирует выходны II

ков;

t t 1

г

- сигналы с выхосигналы А,В, t , t длительность в один такт задающего генератора п тем использовдния при дешифрации в ходов счетчика обеих групп.

Дешифратор 19 формирует сигналы 1 1 1 длительностью в общем случае более одного такта задающег

дов дещифраторов 18 и 19, являющиеся составляющими контрольных интерва-10 генератора путем использования в

Дешифратор 18 формирует выходные II

сигналы А,В, t , t длительностью в один такт задающего генератора путем использовдния при дешифрации выходов счетчика обеих групп.

Дешифратор 19 формирует сигналы. 1 1 1 длительностью в общем случае более одного такта задающего

генератора путем использования в

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1985 |

|

SU1291953A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1149235A1 |

| Устройство для синхронизации вычислительной системы | 1988 |

|

SU1529205A1 |

| Устройство для синхронизации вычислительной системы | 1986 |

|

SU1363172A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1226428A1 |

| Устройство для регистрации сигналов неисправности | 1982 |

|

SU1132291A1 |

| Устройство для отладки программ | 1980 |

|

SU922753A1 |

| Устройство для синхронизации вычислительной системы | 1991 |

|

SU1830527A1 |

| Устройство для контроля @ -разрядных схем сравнения | 1984 |

|

SU1187171A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных систем. Отличительной особенностью устройства является то, что оно обеспечивает подсинхронизацию различных ЦВМ к единой шкале отсчета времени, исправление сбоев сигналов точного времени. Кроме того, оно использует двухуровневую шкалу. Целью изобретения является повышение точности синхронизации нескольких ЦВМ. Поставленная цель достигается введением блока синхронизации с сигналами точного времени. 5 ил.

лов t( и t при приеме входных сигналов М, и М соответственно; tj - сигнал дещифратора одного из начальных тактов счетчика 17о

Устройство работает следующим об- 15 разомо

Распределитель 1 импульсов (фиг,1) формирует сдвинутые по фазе последо25

вательности тактовых импульсов С и С, определенной номинальной частоты, например 252 кГц, с некоторой максимально допустимой погрешностью, например 10 о

Импульсы С, (фиг.1, 2) поступают на счетный вход счетчика 17 и.с выхода 7 устройства выдаются в систему, где, например, могут быть использованы в качестве машинных тактов ЦВМо

Импульсы С поступают (фиг,1,2) в блоки 2 и 3 и используются для ор-. ганизации фиксированных задержек сигналов в пределах одного такта

На входы 5 и 6 устройства поступают синхронные сигналы М, и М точ- 35 ностью задающего.,генератора, Напри- ного времени о Сигналы М имеют относительно сигналов М меньшую, в целое число К раз, частоту следования и определяют начало циклического отсчета сигналов М, в пределах периода (цикла) сигнала

С выходов 8 и 9 в систему выдамер, при номинальных частотах сигналов С и Cj, соответственно 1000 и 10 Гц (тое. значение К равно ЮО), и при указанных параметрах задающе40 го генератора длительность сигнала t,. может быть принята с.250-го по 251-й такто

ются сигналы Cj и Cj, которые например, могут быть использованы для управления высокоточными устройствами и для организации программных циклов ЦВМ соответственно

В штатном режиме работы (при наличии сигналов М, и М,2) периоды и фаза их соответствуют периодам и фазе сигналов М, и М,

Счетчик 17 (фиго2) ведет счет импульсов С, (числа тактов распредев пределах периоС, ( лителя импульсов)

да сигналов С и содержит две группы выходов; младгчих (например, 1-го или 1- и )

разрядов, счетчика.

разрядов и старших т.е, остальных выходов

5

схемах дешифрации только группы старших разрядов счетчика

В каждом периоде сигнала С про- веряется синхронность работы устройства путем контроля совпадения сигнала М с временным интервалом t

0

на выходах элемента И 26

На. фиг.4 приведена временная диаграмма работы блока 2, показывающая: синхронную с сигналами М, работу устройства, работу при отсутстврш первого сигнала М /, последующую работу без поступления сигналов М, работу при появлении несинхронного сигна- 5 ла М и подсинхронизацию блока 2 с ним о

На фиг,5 приведена временная диаг- -рамма работы блока 3 при наличии сигнала Мл

t f.

Дпительность сигнала t, (фиго2,4) выбирается из расчета обеспечения приема переднего фронта и начала сигнала М и определяется величиной периода сигнала

0

М

, и максимально допустимой погрешностью задающего.,генератора, Напри-

мер, при номинальных частотах сигналов С и Cj, соответственно 1000 и 10 Гц (тое. значение К равно ЮО), и при указанных параметрах задающего генератора длительность сигнала t,. может быть принята с.250-го по 251-й такто

По совпадению формируемого устройством сигнала G, и импульса Cf на

выходах элемента И 6 сигналом по входу сброса в о счетчик 17 устанав- ливается в О и на выходе t дешифратора 18 появляется соответствующий сигнал, формирующий конец и задНИИ фронт сигнала С; (в пределах длительности сигнала М), Длительность сигнала t . , например может быть равна длительности обнуленного состояния счетчика 17, Тое. до счета

им первого такта в следующем периоде сигнала Cjo

Счетчик 17 ведет счет тактов в пределах периода сигнала М, как правило, до номинального (А) знача51495773

(в приведенном примере до 252 ов). По мере накоплейия временМн по д ме ге

ной ошибки от погрешности частоты задающего генератора в зависимости от ее знака периодически формируются периоды сигнала С с уменьшенным ил увеличенньпм конечным значением счетчика 18 (в приведенном примере с 251 или 253 тактами соответственно). При этом период сигнала С,, определяемый сигналами М, не и зменяетсЯо

Интервал t| формируется, как составляющих из сигналов t ,

А В, t;.

Элемент И-НЕ 39 (фиГоЗ) при синхронной работе с сигналами М вьздает на вход 13 элемента И 24 (фиг.2) сигнал, запрещающий прохождение с выхода элемента ИЛИ 23 последнего в цикле сигнала G.В качестве сигнала С в этом случае используется сигнал (фиг „1-3 ), поступающий с входа 6 через элемент И 37, цепь 13, элемент ИЛИ 22 на выход 8о При наличии сигналов М и М., ввиду их синфаз- ности, последний период сигнала С в;цикле сохраняется равным предьзду- щим периодамо

В случае непоступления на вход 5 (фиго2) сигнала М (кроме последнего в цикле) счетчик I7 ведет счет тактов до значения В, дешифратор 18 формирует соответствующий сигнал, который через элементы ИЛИ 23, И 24 и ИЛИ 22 поступает на вход 8 в качестве сигнала С, при этом включаются триггеры 30 и 31, с выхода 12 снимается признак наличия сигналов

35 Дания в интервал t, сигналом с выхода элемента И 26 триггер 31 уста- . навливается в О, при этом на выходе 12g снимается признак несинхронной работы с сигналами М, с выхода

М, а на выходе 12 появляется приз- 40 4 снимается сигнал включения триггера 32о Сигналом с выхода элемента И 26 на вход R триггер 32 также устанавливается в О, прекращается режим подсинхронизации с сигналами М 45 и устройство начинает фop rapoвaть сигналы С, синфазные сигналам Mj

Счетчик 33 (фиг,3,5) ведет циклический счет числа сигналов С до

gg значения Ко На счетный вход С счетчя- ка 33 поступают сигналы с инверсно- .го выхода 12 старшего разряда счет-, чика 17 (фиг.2,3), т„ео счет сигналов С ведется с опережением по фа-.

55 ;9е (приближенно на полпернода), Сигнал С формируется элементом И 35 при появлении . на выходе дешифратора 34 сигнала К и последнего в цикле |сигнала Cj, Тое устройство всегда

нак несинхронной работы с сигналами

Начиная со следующего периода сигнала С после включения триггера 31, устройство автономно формирует все, кроме последнего в цикле, сигналы С с периодом номинальной (А) длительности путем вьщачи на выход 8 сигнала с соответствующего выхода дешифратора 18 через элементы И 27, ИЛИ 23, И 24 и ИЛИ 22.

При отсутствии сигнала Mj по наличии М прои.зводится укорочение или удлинение последнего периода сигнала Cj в зависимости от знака погрешности задающего генератора,Тем самым в каждом цикле устраняется накопившаяся временная ошибка формирования сигналов С,о

При появлении на входе 5 сигнала М, триггер 30 устанавливается в О и на выходе 12 появляется признак наличия данных сигналов о Если поступивший сигнал находится в пределах интервала tj-, то он через элемент И 26 устанавливает в О триггер 31 и поступает на выход 8,, При

0 этом с выхода 12 снимается признак несинхронной работы с сигналами М

При несовпадении сигнала М, с интервалом t, Тое при рассинхро-5 низации устройства с сигналом М, его прохождение через элемент И 26 запрещается, триггер 31 продолжает оставаться включенным, и на выходе 12g сохраняется признак несинхрон0 ной работы с сигналами

Признаки наличия сигналов М( и несинхронной работы с сигналами М лоступают на входы 125-и 12g элемента 4.2 (фиг.1), на выходе 14 которо5 го формируется команда задания режима подсинхронизации с сигналами М, включакщая ,триггер 32 (фиг,2), При этом сигнал с его инверсного выхода запрещает прохождение сигналов А че0 рез элемент И 27 н устройство переходит на удлиненный, например на один такт, период формирования сигналов С. При достижении синфазной работы устройства с сигналами М, попа5 Дания в интервал t, сигналом с выхода элемента И 26 триггер 31 уста- . навливается в О, при этом на выходе 12g снимается признак несинхронной работы с сигналами М, с выхода

0 4 снимается сигнал включения триггера 32о Сигналом с выхода элемента И 26 на вход R триггер 32 также устанавливается в О, прекращается режим подсинхронизации с сигналами М 5 и устройство начинает фop rapoвaть сигналы С, синфазные сигналам Mj

обеспечивает взаимную синфазность сигналов Cj, и Cj

Сигналы К с выхода дешифратора 34 и С с выхода II включают триггеры 41 и 42. Триггер 41 в последующем устанавливается в О любым сигналом М с выхода 6, а триггер 42.- толь- ко синхронным сигналом М (т,ео совпадающим с интервалом t при значении счетчика 33, равном К) с выхода элемента И 37„ Интервал t, формируется при помощи элемента ИЛИ 20 (фиг„2), как слагаемое трех сигналов:

f

слагаемое

и til. Назначение сигнала .1

г.

t

.2 и t Назначение сигнала t. рассмотрено, ti и tn - соответстсигналами М (при включении триггера 44) любым сигналом М, при условии завершения режима подсинхрони зацни по сигналу М, т.е. при выключении триггера 32 и снятии при этом запрета на прохождение сигнала Ми через элемент И 38

Задание режим а; под синхронизации

to с сигналами Mg производится выдачей команды на включение триггера 44 с выхода 15 элемента 4о1 (фиГо 1,3) после несинхронного появления сигналов М, на входе 6, Тое. при вьпслю15 чении триггера 41 и при сохраняющемся включении триггера 43,

Элементы И 4 вырабатывают указанные команды на задание режимов под- синхронизации с сигналами М , и М, й

венно отрицательный и положительньй .допуски-от номинальной длительности цикла сигнала Величины допусков

tl и t l определяются максимально воз-20 кроме того, здесь формируются два ножным отклонением в счете тактов сигнала 10 и Ю., объединяющих вы- счетчиком 17 за цикл сигнала М при ходы 12g-, 13 и 12g, 13. блоков 2 и отсутствии сигналов М|. Для приведен- 3, обеспечивающие соответственно ных параметров задающего генератора и сигнала М допуски t и t могут составить четыре такта

При непоступлении сигнала Н триггеры 41 и 42 (фиг„3) продолжают сохранять свое единичное состояние и по сигналу tj включается триггер 30 43, при этом на выходе 13 отсутствует признак наличия сигналов Mj,, а на выходе 13j появляется признак

25

несинхронной работы с сигналами М При наличии сигналов Mj устройство продолжает формировать сигналы С. и С с прежними точностными парамет- рамИо

При отказе обоих сигналов М

3j обеспечивающие контроль наличия сигналов М , М точного времени и контроль режимов работы устройства. Отсутствие сигналов на выходе 10 свидетельствует о синхронной работе устройства. Наличие сигналов на выходах 12 g и 13 означает отсутствие синхронной работы с сигналами М.) и М и автономное формирование устройством выход- : ных управляющих сигналов С или С соответственно

35

Формула изобретения

Устройство для синхронизации вычислительной системы, содержащее

М„ устройство переходит на полностью40 задающий генератор, распределитель

автонрмный режим формирования сигналов Cij, и Сз с погрешностью частоты задающего генератора

Установка в О счетчика 33,Тое. подготовка нового цикла, всегда про- изводится при совпадении на входах элемента И 45 обнуляющего сигнала с выхода элемента ИЛИ 40 с синхроим- пульсом С, (по концу сигнала С)

Обнуляющий сигнал формируется при помощи элементов ИЛИ 40, И 36 - 38: в синхронном режиме работы по поступлению сигнала Mj с вход,а 6 через элемент И 37; при отсутствии синхронного сигнала М сигналом tj в „ начале следующего цикла, при сохраняющемся состоянии К на счетчике 33 и на дешифраторе 34 через элемент И 36; в режиме подсинхронизации с

50

сигналами М (при включении триггера 44) любым сигналом М, при условии завершения режима подсинхронизацни по сигналу М, т.е. при выключении триггера 32 и снятии при этом запрета на прохождение сигнала Ми через элемент И 38

Задание режим а; под синхронизации

с сигналами Mg производится выдачей команды на включение триггера 44 с выхода 15 элемента 4о1 (фиГо 1,3) после несинхронного появления сигналов М, на входе 6, Тое. при вьпслючении триггера 41 и при сохраняющемся включении триггера 43,

Элементы И 4 вырабатывают указанные команды на задание режимов под- синхронизации с сигналами М , и М, й

кроме того, здесь формируются два сигнала 10 и Ю., объединяющих вы- ходы 12g-, 13 и 12g, 13. блоков 2 и 3, обеспечивающие соответственно

кроме того, здесь формируются два сигнала 10 и Ю., объединяющих вы- ходы 12g-, 13 и 12g, 13. блоков 2 и 3, обеспечивающие соответственно

3j обеспечивающие контроль наличия сигналов М , М точного времени и контроль режимов работы устройства. Отсутствие сигналов на выходе 10 свидетельствует о синхронной работе устройства. Наличие сигналов на выходах 12 g и 13 означает отсутствие синхронной работы с сигналами М.) и М и автономное формирование устройством выход- : ных управляющих сигналов С или С соответственно

35

Формула изобретения

Устройство для синхронизации вычислительной системы, содержащее

0

импульсов, первый блок синхронизации с .сигналами точного времени, причем первый выход распределителя импульсов соединен с первым тактовым входом первого блока синхронизации с сигналами точного времени, вход запуска которого является входом сигналов точного времени устройства,первый тактовый выход первого блока синхронизации с сигналами точного времени является первым тактовым выходом устройства, о т л и ч а ю - щ е е с я тем, что, с целью повьш е- ния точности синхронизации нескольких ЦВМ, в устройство введен второй блок синхронизации с сигналами точного времени и группа элементов И, причем первый выход распределителя импульсов является вторым тактовым

выходом устройства, второй выход распределителя импульсов соединен с вторым тактовым входом первого блока синх юнизации с сигналами точного времени и с первым тактовым входом второго блока синхронизации с сигналами точного времени, вход запуска которого является входом запуска сигналов точного времени устройства, второй тактовый вход второго блока синхронизации с сигналами точного времени соединен с первым тактовым выходом первого блока синхронизации с сигналами точного времени третий, четвертый, пятый и шестой тактовые входы второго блока синхронизации с сигналами точного времени соединены соответственно с вторым, третьим, четвертым и пятым тактовыми выхода- ми первого блока синхронизации с сигналами точного времени, вход начальной установки второго блока синхронизации с сигналами точного времени соединен с выходом первого элемента И группы, первый тактовый выход второго блока синхронизации с сигналами точного времени является тактовым выходом устройства, первый и второй выходы разрешения блокировки второго блока синхронизации с сигналами точного времени соединены соответственно с первым и вторым входами разрешения блокировки первого блока синхронизации с сигналами точного времени, первый и второй выходы признака сбоя первого блока синхронизации с сигналами точного времени соединены соответственно с первым и вторым входами Btoporo элемента И группы и являют- ся первым и вторым выходами группы выходов сбоя устройства, входы первого элемента И группы соединены соот- .ветственно с первым и вторым выходами признака сбоя второго блока синх- ронизац5-ш с сигналами точного времени и являются соответственно тр-етьим и четвертым выходами группы выходов сбоя устройства, выход второго элемента И группы соединён с входом на- чальной установки первого блока синхронизации с сигналами точного времени, причем первый блок синхронизации с сигналами точного времени содержит счетчик, два дешифратора, шесть элементов И, элемент НЕ, четыре элемента ИЛИ, три -триггера, причем счетный вход счетчика является первым тактовым входом блока, первый вход

первого элемента И является вторым тактовым входом блока, выход первого элемента И.соединен с входом сброса в О счетчика, первый вход первого элемента ИЛИ является первым входом резрешения блокировки блока, выход первого элемента ИЛИ соединен с вторым входом первого элемента И и является первым тактовым выходом блока, первый вход второго элемента И является вторым входом разрешения блокировки блока, выход второго элемента И соединен с вторым входом первого элемента ИЛИ, группа выходов младших разрядов счетчика соединена с первой группой -входов первого дешифратора, группа выходов старших разрядов счетчика соединена с второ й группой входов первого дешифратора и с группой входов второго дешифратора, первый выход которого соединен с первым входом второго элемента ИЛИ инверсный выход старшего разряда счетчика является вторым тактовым выходом блока, выход третьего элемента ИЛИ является третьим тактовым выходом блока, первый выход первого дешифратора соединен с вторым входом второго элемента И.ПИ, с первым входом четвертого элемента ИЛИ и с первым входом третьего элемента И, выход которого сое.динен с входом триггера, вход сброса в О которого соединен с входом элемента НЕ, с первым входом четвертого элемента И и является входом запуска блока, второй выход первого дешифратора соединен с третьш 5 входом второго элемента ИЛИ и с первым входом пятого элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, третий выход первого дешифратора соединен с четвертым входом второго элемента ИЛИ, с первым входом третьего элемента ИЛИ, второй и третий входы которого соединены соответственно с вторым и третьим выходами второго дешифратора, выход второго элемента ИЛИ соединен с вторым входом четвертого элемента И, выход которого соединен с входом сброса в О второго триггера, с первым входом шестого элемента И и входом сброса в О третьего триггера, вход установки в 1 которого является входом начальной установки блока, инверсный выход

n

третьего триггера соединен с первым входом пятого элемента И и является пятым тактовым выходом блока, инверсный выход второго триггера соединен с вторым входом шестого элемента И, выход которого соединен с третьим входом четвертого элемента ИЛИ,ин версный выход первого является первым выходом признака сбоя блока, прямой выход первого триггера соединен с входом установки в 1 второго триггера, прямой выход кото„рого соединен с вторым входом пято- элемента И и является вторым выходом признака сбоя блока, четвертый выход первого дешифратора является четвертым тактовым выходом

первого блока синхронизации с сигналами точного времени, второй блок синхронизации с сигналами точного времени содержит счетчик, дешифратор, пять элементов И, элемент ИЛИ,четыре триггера и И-НЕ, причем первый вход первого элемента И соединен с синхровходом первого триггера, с синхровходом второго триггера и является первым тактовым входом блока, первый вход второго элемента И является вторым тактовым входом блока, счетный вход счетчика является третьим тактовым входом блока, первый вход третьего элемента И является четвертым тактовым входом

14

блока, группа разрядных выходов счет- И-НЕ, выход четвертого элемента И чика соединена с группой входов дешифратора, выход которого соединен с J-вxoд(э первого триггера, с вторым входом третьего элемента И, с первым входом элемента И-КЕ, с вто- 40 рым входом втЪрого элемента И, с первым входом четвертого элемента И и С чТ-входом второго триггера, вход

соединен с вторым входом элемента ИЛИ, выход пятого элемента И соединен с третьим входом элемента ИЛИ, выход второго элемента И является третьим тактовые выходом блока, выход второго триггера -соединен с J - входом третьего триггера.

,

49577312

сброса в о счетчика соединен с вы- i ходом первого элемента И, второй вход которого соединен с выходом

элемента ИЛИ, синхровход третьего триггера соединен с вторым входом четвертого элемента И и является пятым тактовым выходом блока, инверсный выход первого триггера является

fQ первым выходом признака сбоя блока, прямой выход третьего триггера является вторым выходом признака сбоя блока, вход установки в 1 четвертого триггера является входом чальной установки блока, первый вход пятого элемента И является шестым тактовым входом блока, прямой выход четвертого триггера соединен с вторым входом пятого элемента И,тре20 тий вход третьего элемента И соединен с третьим входом пятого элемента И, с входом сброса в О первого триггера и является входом запуска блока, выход третьего элемента И сое25 динен с первым входом элемента ИЛИ, с входом сброса в О второго триггера, с входом сброса в О третьего триггера, с входом сброса в О четвертого триггера и является первым

30 выходом разрешения блокировки блока, выход элемента И-НЕ является вторым выходом разрешения блокировки блока, инверсный выход третьего триггера соединен с вторым входом элемента

И-НЕ, выход четвертого элемента И

соединен с вторым входом элемента ИЛИ, выход пятого элемента И соединен с третьим входом элемента ИЛИ, выход второго элемента И является третьим тактовые выходом блока, выход второго триггера -соединен с J - входом третьего триггера.

Ifffit ff

Фиг f

ISj

Ф«.

/J«

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-23—Публикация

1987-03-23—Подача