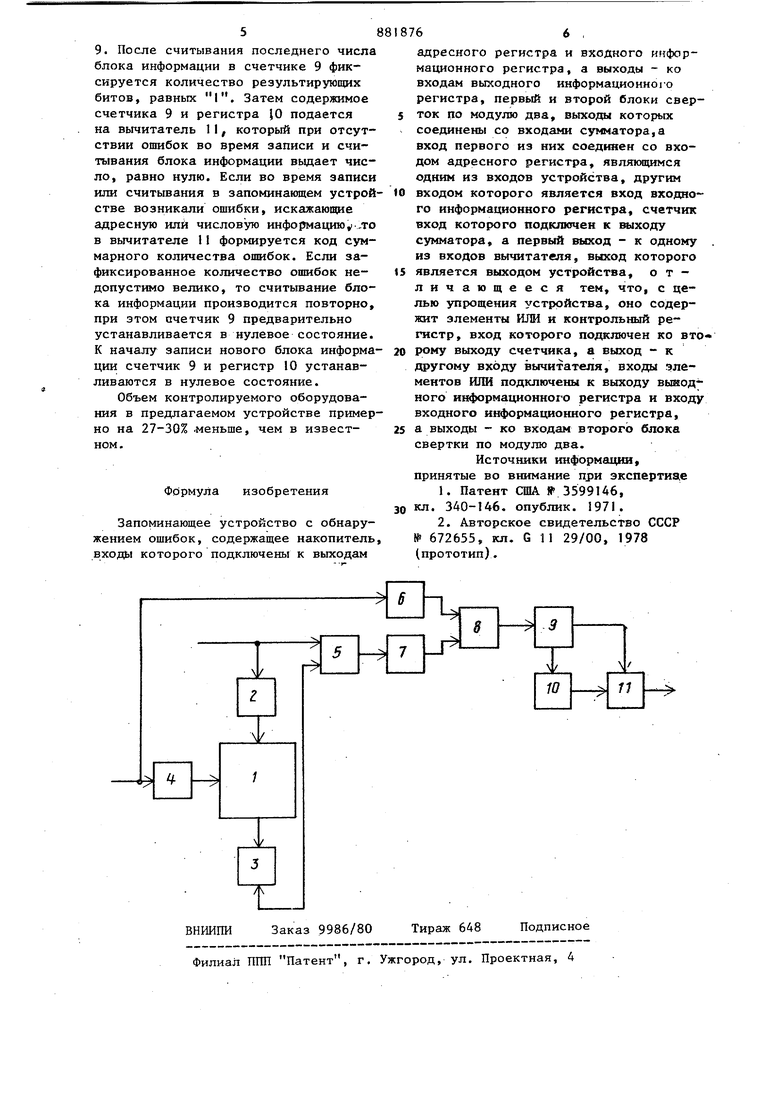

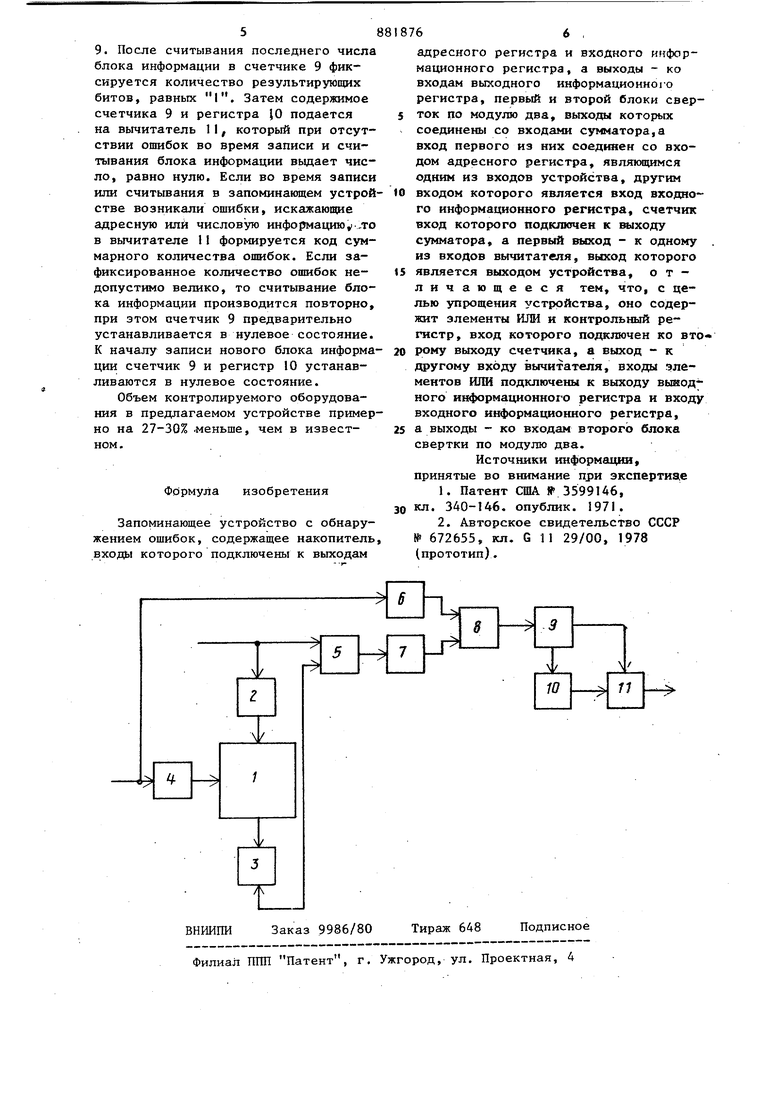

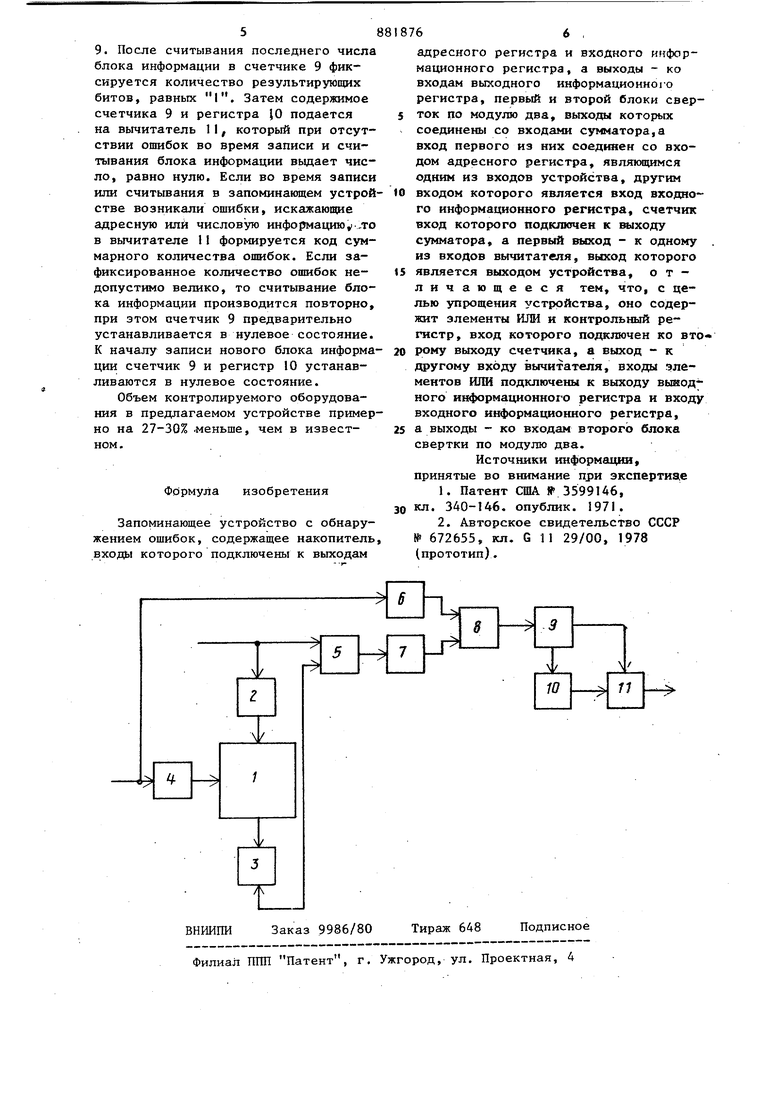

Изобретение относится к запоминающим устройствам. Известно запоминающее устройство с обнаружением ошибок, содержащее накопитель, входной и выходной регистры, адресный блок и блоки сверток по модулю два. Обнаружение ошибок в нем основано на запоминании контрольных битов записываемой информации в элементах памяти накопителя, специально отведенных для этих целей,, и сравнении их.с контрольными битами, сформированными при считывании информации. Это приводит к большой аппарат турной избыточности l, Наиболее близким техническим реше нием к изобретению является запоминающее устройство с обнаружением ошибок содержащее накопитель, соединенный с входным, выходным и сщресным регист рами, первый и второй блоки сверток по модулю два, входы которых подключены соответственно ко входам адресно го и входного регистров, а выходы входам первого сумматора, третий и четвертый блоки сверток по модулю два, входы которых соединены соответственно со входом адресного и с выходом выходного регистров, а выходы - со входами второго сумматора, причем выход каждого сумматора соединен со входом соответствующего счётчика, а выходы счетчиков подключены ко входам вычитателя. В этом устройстве в режиме записи при каждом обг ращении к накопителю код адреса и код записываемого слова подаются соответственно на входы адресного и входного регистров и производится запись слова в соответствующую ячейку накопителя. Одновременно код. адреса и код записываемого слова подаются соответственно на первый и второй блоки сверток, которые вырабатывают биты четности адреса и записываемого слова. Биты четности объединяются пер вым сумматором в результирующий бит, который записывается в первый счет3. чик. к концу записи в накопитель все го блока информации счетчик фиксирует суммарное количество результирующих битов, равных 1. В режиме считывания с помощью третьего и четвертого блоков сверток по модулю два второго сумматора и второго счетчика аналогично как и при записи, фиксиру ется суммарное количество результирующих битов, равных I, Затем содержимое счетчиков подается на вычитатель. При отсутствии ошибок разность кодов равна нулю. При наличии ошибок в вычитателе формируется разность кодов, равная общему количеству ошибок 2 . Недостатком этого устройства является большое количество оборудрвания Цель изобретения - упрощение устройства за счет сокращения количества оборудования в нем. Поставленная цель достигается тем что в запоминающее устройство с обнаружением ошибок, содержащее накопитель, входы которого подключены к выходам адресного регистра и входного информационного регистра, а выходы - ко входам выходного информацион ного регистра, первый и второй блоки сверток по модулю два, выходы которы соединены со входами сумматора, а вход первого из них соединен со вхо Дом адресного регистра, являющимся одним из входов устройства, другим входом которого является вход входного информацихзнного регистра, счетчик, вход которого подключен к выход сумматора, а первЬй выход - к одному из входов вычитателя, выход которого является выходом устройства, введещл элементы ИЛИ и контрольный-регист вход которого подключен ко второму выходу счетчика, а выход - к другому входу вычитателя, входы элементов ИЛ подключены к выходу выходного информационного регистра и входу входного информахщонного регистра, а выходы - ко входам второго блока свертки по модулю два. На чертеже представлена структурная схема предложенного устройства. Устройство содержит накопитель 1, соединенный с входным информационгшм 2, выходным информационным 3 и адрес ным 4 регистрами, элементы ИЛИ 5, первый 6 и второй 7 блоки сверток по модулю два, сумматор 8, счетчик 9, контрольный регистр 10 и вычитатель 11. Первые входы элементов ИЛИ 3 подключены к выходу регистра 3, вторые входы - ко входу регистра 2, а выходы - ко входу второго блока сверток по модулю два 7. Вход первого блока сверток по модулю два 6 соег, динен со входом адресного регистра 4, а выходы первого 6 и второго 7 блбков сверток по модулю два подключены ко входам сумматора 8. Вход счетчика 9 соединен с выходом сумматора 8, первый выход подключен к одному из входов вычитателя 11, второй выход - ко входу регистра 10, выход.которого соединен с другим входом вычитателя 11. Устройство работает следующим об-разом. В режиме записи код адреса и код записываемого слова подаются соответственно на входы адресного 4 и входного 2 регистров и производится запись слова в соответствующую ячейку накопителя 1. Одновременно код адреса и код записываемого слова подаются соответственно на первый 6 и через элементы. ,ИПИ 5 на второй 7 блоки, которые вырабатывают биты четности адреса и записываемого слова. При этом во всех разрядах выходного регистра 3 хранится код О. Виты четности объединяются сумматором 8 в результирующий бит, который в случае его единичного значения поступает в счетчик 9 и увеличивает содерясимое счетчика на единицу. Таким образом, к концу записи всего блока информации в накопитель 1 счетчик 9 фиксирует количество результирующих одиночных битов, равных 1. Зафиксированное счетчиком 9 число передается в регистр 10 и сохраняется там до тех пор, пока .соответствующий блок информации находится в накопителе 1. В режиме считывания в каждом такте обращения соответствующее коду адреса число извлекается из накопителя 1 и поступает через регистр 3 на выход устройства. Одновременно код адреса и код считанного слова подаются соответственно на первый 6 и через элементы ИЛИ 5 на второй 7 блоки, которые как и при записи вырабатывают биты четности адреса и записываемого слова. При этом во всех разрядах входного регистра 2 хранится код О. Биты четности объединяются сумматором 8 в результирующий бит, который записывается в счетчик

9. После считывания последнего числа блока информации в счетчике 9 фиксируется количество результирующих битов, равных I. Затем содержимое счетчика 9 и регистра JO подается на вычитатель 1I который при отсутствии ошибок во время записи и считывания блока информации выдает число, равно нулю. Если во время записи или считывания в запоминающем устройстве возникали ошибки, искажающие адресную или числовую информацию, .то в вычитателе 11 формируется код суммарного количества ошибок. Если зафиксированное количество ошибок недопустимо велико, то считьшание блока информации производится повторно, при этом очетчик 9 предварительно устанавливается в нулевое состояние. К началу записи нового блока информации счетчик 9 и регистр 10 устанавливаются в нулевое состояние.

Объем контролируемого оборудования в предлагаемом устройстве примерно на 27-30% .меньше, чем в известном.

Формула изобретения

Запоминающее устройство с обнаружением ошибок, содержащее накопитель, входы которого подключены к выходам

адресного регистра и входного икформационного регистра, а выходы - ко входам выходного информационного регистра, первый и второй блоки сверток по модулю два, выходы которъсх соединены со входами сумматора,а вход первого из них соединен со входом адресного регистра, являкмцимся одним из входов устройства, другим

входом которого является вход входного информационного регистра, счетчик вход которого подключен к выходу сумматора, а первый выход - к одному из входов вычитателя, выход которого

является выходом устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит элементы ИЛИ и контрольный регистр, вход которого подключен ко второму выходу счетчика, а выход - к другому входу вычитателя, входы элементов ШШ подключены к выходу выкодного информационного регистра и входу входного информационного регистра,

а выходы - ко входам второго блока свертки по модулю два.

Источники информации, принятые во внимание при экспертиэ е

1.Патент США if 3599146, кл. 340-146. опублик. 1971.

2.Авторское свидетельство СССР № 672655, кл. G 11 29/00, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1977 |

|

SU672655A1 |

| Запоминающее устройство с обнаружением ошибок | 1981 |

|

SU955197A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1129655A1 |

| Запоминающее устройство с обнаружением ошибок | 1982 |

|

SU1034070A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1088073A2 |

| Запоминающее устройство с обнаружением ошибок | 1985 |

|

SU1277215A1 |

| Запоминающее устройство с обнаружением ошибок | 1984 |

|

SU1164791A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1130897A2 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

Авторы

Даты

1981-11-15—Публикация

1980-01-28—Подача