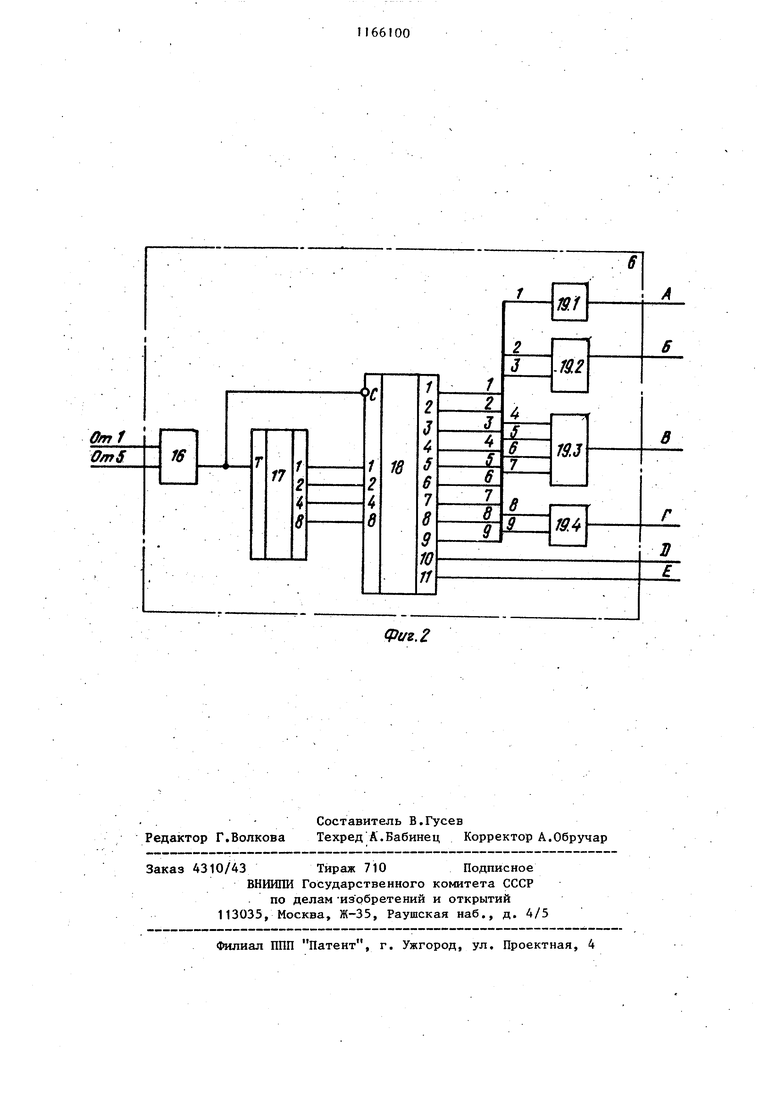

Изобретение относится к вычислительной технике и может быть исполь зовано для обработки результатов измерений в составе автоматических систем управления и контроля. Известно устройство для деления, содержащее коммутатор, счетчик делимого,, блок задания кода делителя, буферный счетик, блок фиксации окон чания деления, блок сравнения и счетчик частного Ш . Наиболее близким к изобретению по технической сущности является устройствр для деления, содержащее коммутатор импульсов, счетчик делим го, счетчик частного, бло1 задания кода делителя, блок сравнения, СОСТОЯ1ЦИЙ из п поразрядных узлов сравнения (п - число разрядов делителя) , блок фиксации окончания деления, первый и второй,элементы ИЛИ элемент задержки, счетчик и п элементов памяти, причем информационны вход коммутатора импульсов соединен с тактовым входом устройства, а выходы соединены с соответствующими . разрядными входами счетчика делимого и входами первого элемента ИЛИ, выход счетчика делимого соединен с входом блока фиксации окончания деления, входы первой группы блока сравнения соединены с соответствующими разрядными вьЬсодами блока задания кода делителя, выход первого элемента ИЛИ соединен со счетным входом счетчика, вход установки в ноль которого соединен с выходом второго элемента ИЛИ, разрядные выходы счетчика сответственно соединены с входами второй группы блока сравнения, выходы которого соединен соответственно с первыми входами элементов памяти, вторые входы кото рых объединены .и соединены с выходом элемента задержки, вь1ход i-ro элемента памяти (, 2, ...,п) соединен с входо (i + разряда, третьей группы блока сравнения, i-M входом второго элемента ИЛИ и с i-M управляющим входом коммутатора импульсов, выход п-го элемента памя ти соединен с входом счетчика частн го и входом элемента задержки Недостатком известных устройств является их невысокое быстродейств Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее блок задания кода делителя,счетчик делимого, счетчик .частного,, триггер, установочный вход которого соединен с выходом счетчика делимого, введены по числу разрядов делителя преобразователи параллельного кода в .последовательный и кодовый распределитель импульсов, содерж.ащий элемент И, три элемента ИЛИ, счетчик и дешифратор, информационные входы которого подключены к соответствукяцим информационным выходам счетчика, а стробирующий вход - к счетному входу счетчика и к выходу элемента И, первый вход которого является информационным входом кодового распределителя импульсов,.а-второй его вход управляющим, первый выход дешифратора является первым выходом Кодового распределителя игшульсов, второй и третий .выходы дешифратора соединены с входами первого элемента ИЛИ, четвертый, пятый, шестой и Седьмой выходы дешифратора подключены к входам второго элемента ШШ, выходы дешифратора с второго по девятьй соединены с входами третьего элемента ИЛИ, выходы элементов ИЛИ являются соответственно вторым, третьим и четвертым выходами кодового распределителя импульсов, десятый и одиннадцатый выходы дешифратора являются соответ-, ственно пятым и шестым выходами рас...пределителя импульсов, причем информационный вход распределителя импульсов подключен к тактовому входу устройства, управлякядий вход - к выходу триггера, первые четыре выхода кодового распределителя импульсов соединены с информационными входами всех преобразователей параллельного кода в последовательный, управлякшще входы которых соединены с соответствующими разрядными выходами блока задания кода делителя, выходы преобразователей параллельного кода в последовательный соединены с соответствующими входами счетчика делимого, управляющий вход которого соединен с пятым выходом кодового распределителя импульсов и со счетным входом счетчика частного, выход которого является выходом устройства, установочный вход счетчика делимого подключен к шестому выходу кодового распределителя импульсов, счетный вход триггера соединен с пусковым входом устройства. На фиг. 1 изображена структурная схема устройства для деления А-разрядного д,есятичного числа на 3-разрядноеJ на фиг. 2 - пример выполнен кодового распределителя импульсов. Устройство для деления (фиг. 1) содержит тактовый вход 1, пусковой вход 2, блок 3 задания кода делителя, преобразователи 4.1, 4.2 и 4,3 параллельного кода в последовательный соответственно для каждого разряди делителя, триггер 5, кодовый распределитель 6 импульсов, счетчик 7частного, счетчик 8 делимого. Блок 3 содержит счетчики9, счетчик 8содержит элементы ИЛИ 10, счетчик 11, триггеры 12, элементы И 13. Выходы блока 3 задания делителя соединены с управляющими входами преобразователей 4 параллельного кода в последовательный, информационные входы которьк соединены с выходами кодового распределителя 6 импульсов, информационный вход последнего подключен к тактовому входу 1устройства, управляющий вход к выходу триггера 5, счетный вход которого подключен к пусковому вход 2устройства, установочный вход триггера 5 соединен с выходом счетч ка 8 делимого, управлякщий вход которого подключен к п ятому выходу кодового распределителя 6 импульсов и счетному входу счетчика 7 частног установочный вход - к шестому выходу кодового распределителя 6 импуль сов, выходы преобразователей 4 параллельного кода в последовательный подключены к соответствующим входам счетчика 8 делимого, два входа 14 и 15 блока 3 задания делителя являются информацион)Ш1ми входами устрой ства (для записи значения-делителя в последовательном коде по входу 14 и в параллельном коде с информацион ных шин.15 по сигналу Запись), выход счетчика 7 частного является выходом устройства. Блок 3 задания кода делителя может быть выполнен, например, в виде счетчиков 9.1, ..., 9.3 .(фиг.1 Счетный вход.счетчика 9.1 соединен с входом 14, на который информация о значении делителя вносится в последовательном коде, поразрядные входы счетчиков 9.1, ..., 9.3 подключены к входу. 15 устройства на которьй информа1и1я поступает в параллельном коде и записьгоается сигналом по входу Запись, выход счетчика 9.1 соединен с счетным входом счетчика 9.2, выход счетчика 9.2 подключен к счетному входу счетчика 9.3. Преобразователи 4.1, ... 4.3 параллельного кода в последовательный служат для поразрядного преобразования параллельного двоично-десятично о кода делителя в последовательный и представляют собой для каждого двоично-десятичного разряда делителя четыре 2-входовых элемента И, выходы которых объединены по схеме ИЛИ. Кодовый распределитель 6 импульсов предназначен для вьфаботки распределенных во времени последовательностей импульсов для организации записи значения делителя в счетчик В делимого в соответствии с заданными весами кода делителя и, состоит (фиг. 2) из элемента И 16, счетчика 17, дешифратора 18 и элементов КПИ 19. 1 Первый и второй входы элемента И 16 являются сигнальными и управляющими входами кодового распределителя 6 импульсов соответственно, выход элемента И 16 соединен с счетным входом счетчика 17 и стробирующим входом дешифратора 18, информационные входы которого подключены к соответствунлцим выходам счетчика, первый выход дешифратора 18 является первым выходом кодового распределителя 6 импульсов, выходы дешифрагора 18 соединены с соответствующими входами элементов ИЛИ 19, выходы элементов ИЛИ 19 являются соответственно вторым, третьим и четвертым выходами распределителя 6 импульсов, десятый и одиннсщцатый выходы дешифратора 18 являются пятым и шестым выходами распределителя 6 импульсов соответственно i Счетчик 8 делимого (фиг. 1) предназначен для записи значения делимого в последовательном или параллельном (не показано) коде и организации процесса деления. Счетчик 8 содержит элементы ИЛИ 10, декадные счетчики 11, триггеры 12, элементы И 13. Устройство работает следумчим образом. Поступающий по входу 2 сигнал (Пуск деления) устанавливает триг гер 5 в единичное состояние, сигнал с выхода которого запускает в рабо ту кодовый распределитель 6 импульс .При этом тактовые импульсы с вхо да 1 через элемент И 16 (фиг. 2) поступают на вход счетчика 17. Импульсные последовательности с выход распределителя 6 поступают на инфор мационные входы преобразователей 4 кода, на других входах которых присутствуют управляющие сигналы (разрешающие или запрещающие) с блока 3 задания кода делителя. Преобразованный за один цикл работы распределителя 6 импульсов блоками параллельный код в последовательный для каждого разряда делителя с выхода преобразователей 4 поступает на вычитающие входы соответствующих разрядов счетчика 8 делимого. За девять первых тактовых импульсов, поступающих на вход кодо вого распределителя 6 импульсов, из значения делимого в счетчике 8 вычтется значение делителя. При переходе цикла вычитания в одном из . разрядов (или обоих) счетчика 8 (в счётчиках 11.1 и 11.2) значения через О, соответствующий триггер 12.1 и 12.2 запомнит этот переход, а импульсом с распределителя 6 по шине Выход 5 на элементы И 13.1 и 13.2 на их выходах сформируется счетный импульс заема из соответствующего следующего старшего разря да счетчика 8, импульсом по шине Выход 6 триггеры 12.1 и 12.2 уста новятся в исходное нулевое состояние. Таким образом, производится 0 .6 одноразовое вычитание значения делителя, хранящегося в блоке 3 из значения делимого в счетчике 8 за цикл работы распределителя 6 импульсов, и один импульс по шине Выход 5 поступает на счетный вход счетчика 7 частного. Далее распределитель 6отрабатьшает второй цикл, третий и т.д. Процесс вычитания производится до тех пор, пока не произойдет переход значения через О в счетчике 11.4,по сигналу с выхода которого триггер 5 установится в состояние О и запретит работу кодового распределителя 6. На этом процесс деления закончится и в счетчике 7 частного зафиксируется значение результата деления двух чисел. При необходимости увеличения точности или уменьшения дискретности результата деления, нужно значение делимого в счетчике 8 записать с сдвигом на соответствующее количество разрядов в сторону старшине разрядов. Весь процесс деления производится за га циклов работы распределителя 6, независимо от значений (разрядности) делимого и делителя, т.е. за 12.m тактов, где m - результат деления. Таким образом, введение в предлагаемое устройство кодового распределителя импульсов и поразрядных преобразователей параллельного кода в последовательньй позволяет повысить быстродействие работы предлагаемого устройства по сравнению с известным )iK раз (К - количество разрядов делителя), например для 4-разрядного делителя в 3 раза.

тч

fpuz.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для деления | 1980 |

|

SU903867A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Делительное устройство | 1973 |

|

SU470805A1 |

| Устройство для деления | 1979 |

|

SU809176A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1283753A1 |

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ, содержащее блок задания кода делителя, счетчик делимого, счетчик частного, триггер, установочный вход которого соединен с выходом счетчика делимого, отличающееся тем, ч.то, с целью повышения быстродействия, в него введены по числу разрядов делителя преобразователи параллельного кода в последовательный и кодовый распределитель импульсов, содержащий элемент И, триэлемента ИЛИ, счетчик и дешифратор, информационные входы которого соединены с соответствующими выходами счетчика, а стробирующий вход - со счетным входом счетчика и с выходом элемента И, первый вход которого является информационным входом кодового распределителя импульсов, а второй его вход - управляющим, первый выход дешифратора является первым выходом кодоззого распределителя импульсов, второй и третий выходы дешифратора соединены с входами первого элемента ИЛИ, четвертый, пятый, шестой и седьмой выходы дешифратора соединены с входами второго элемента ИЛИ, выходы дешифратора с второго по девятый соединены с входами третьего элемента ИЛИ, выходы элементов ИЛИ являются соответственно вторым, третьим, и четвертым выходами кодового распределителя импульсов, десятый и одиннадцатый выходы дешифратора являются соответственно пятым и шестым выходами кодового распределителя импульсов, причем информационный вход кодового распределителя импульсов соединен с тактовым входом уст(Л ройства, управляющий вход - с выходом триггера, первые четыре вькода кодового распределителя импульсов соединены с информационными входами преобразователей параллельного кода L в последовательный, управляющие входы которых соединены с соответствующими разрядными выходами блока заО) дания кода делителя, выходы преобра-. зователей параллельного кода в посО ледовательный соединены с соответ.ствующими входами счетчика делимого, управлякиций вход которого соединен с пятым выходом кодового распределителя импульсов и со счетным входом счетчика частного, выход которого является выходом устройства, установочный вход счетчика делимого соединен с шестым выходом кодового распределителя импульсов,, счетный вход триггера соединен с пусковым входом устройства. .

Авторы

Даты

1985-07-07—Публикация

1983-05-20—Подача