Изобретение относится к вычислительной технике, в частности к электронным цифровым вычислительным машинам.

Цель изобретения - повышение быст родействия устройства.

Пусть D - значение делителя, а В - значение делимого (или очередного остатка), тогда частное (или младшая часть частного) В

В X D

D (1)

выражение (1) значе- 5

6

имеют граничные

значения остатка:

X D

II

X D

Если текущий остато.к лютной величине меньще,

/В;/ I D,Г2)

ТО в очередном цикле необходимо выполнить только сдвиг.

Если текущий остаток В- по абсо- лютной величине больше, чем в, т,е.

/В;/ I D,

(3)

то необходимо выполнить цикл, содержащий сложение и сдвиг.

Если выполняется неравенство

I D /В; I D,

(4)

процессе деления текупщй значениями В и в и выто можно производить как сложение со сдвигом, так и только сдвиг. Сравнивая в остаток со бирая тип очередного цикла в соответствии с условиями (2), (3) и (4) можно обеспечить минимально возможное количество суммирований дпя любых значений частного.

Весь диапазон изменения делителя

ji:D 1 может быть разбит на несколько поддиапазонов, для каждого из которых можно указать значение остатка малой разрядности, начиная с которого выполняются циклы того иного типа,

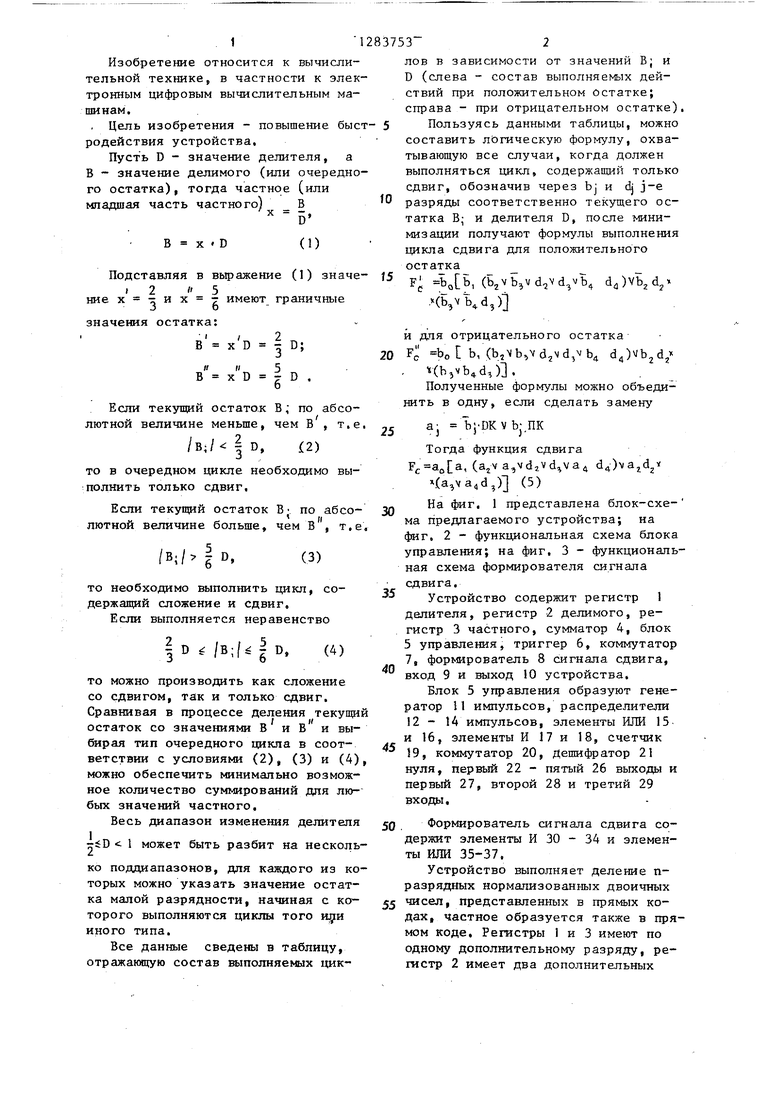

Все данные сведены в таблицу, отражающую состав выполняеьых цик5

лов в зависимости от значений В; и D (слева - состав выполняег ых действий при положительном остатке; справа - при отрицательном остатке). Пользуясь данными таблицы, можно составить лЬгическую формулу, охватывающую все случаи, когда должен выполняться цикл, содержащий только

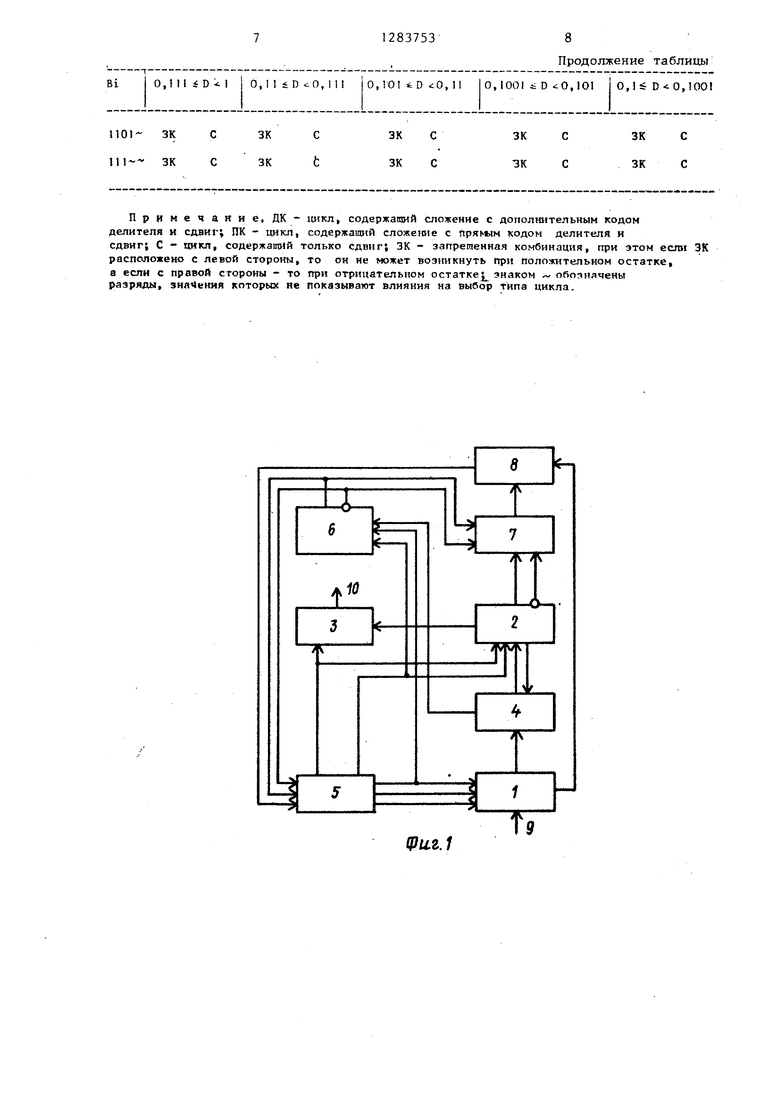

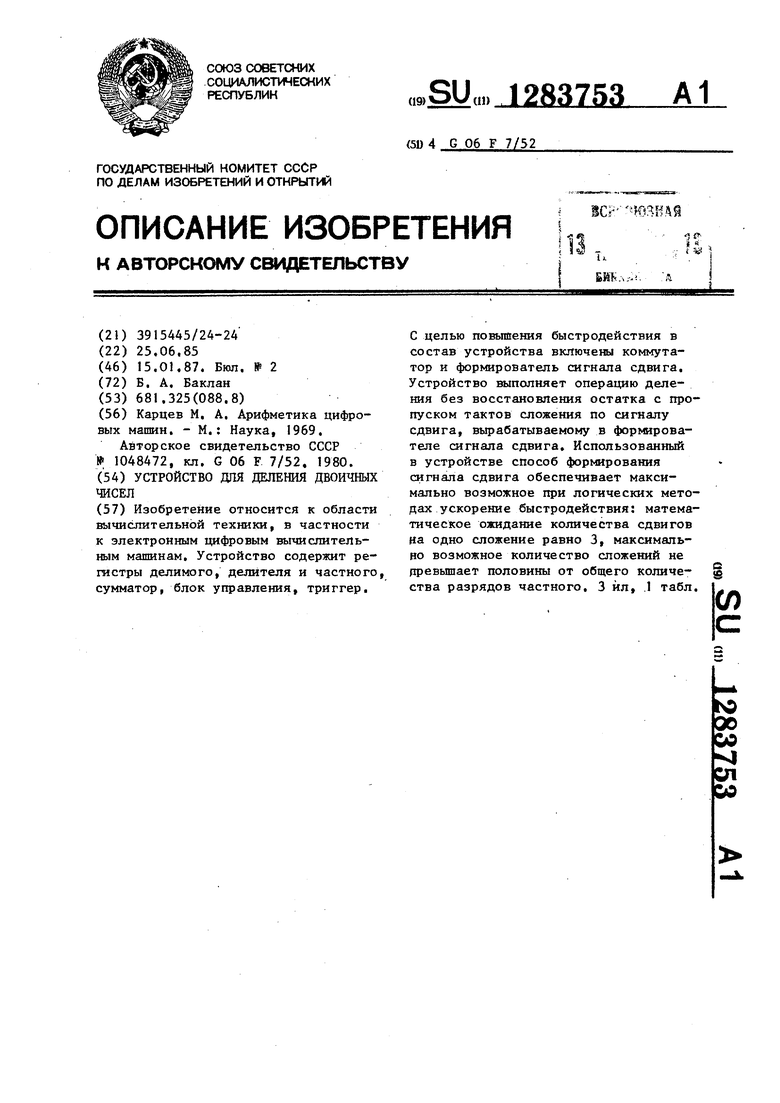

сдвиг, обозначив через bj и dj j-e разряды соответственно текущего остатка В; и делителя D, после минимизации получают формулы выполнения цикла сдвига для положительного остатка FX , (bjVb,,vb, d)Vb,

.4b,,)

и дпя отрицательного остатка 20 F bo b, (b,Nb,vd,,vd,vb4

. v(b,,).

Полученные формулы можно объединить в одну, если сделать замену

25

а;

bj DK V bj.OK

0

5

0

5

0

5

Тогда функция сдвига , (a,jV a,vdjVd va4 (a,va4d,) (5)

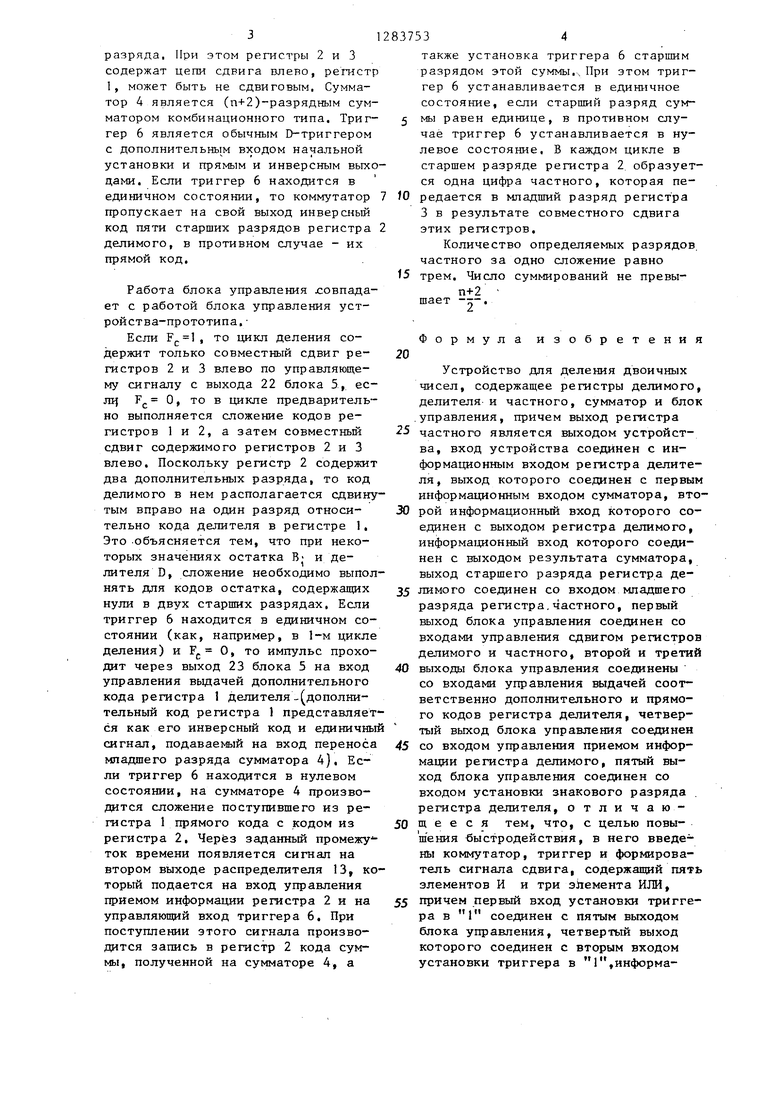

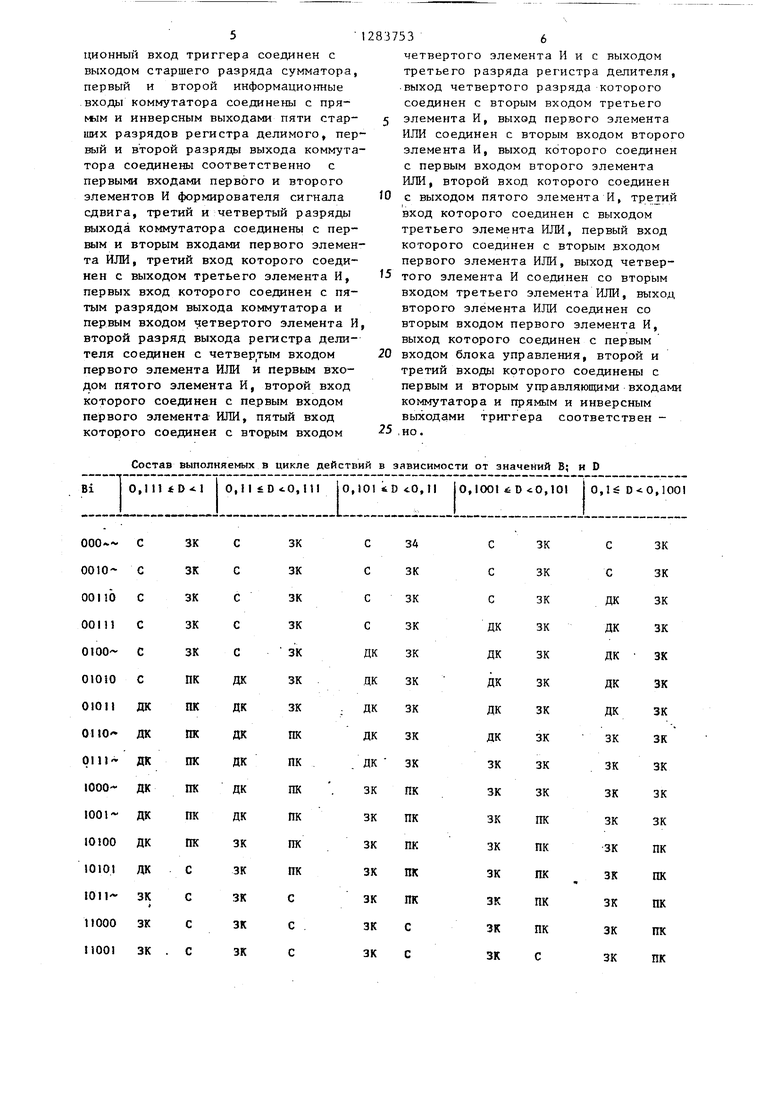

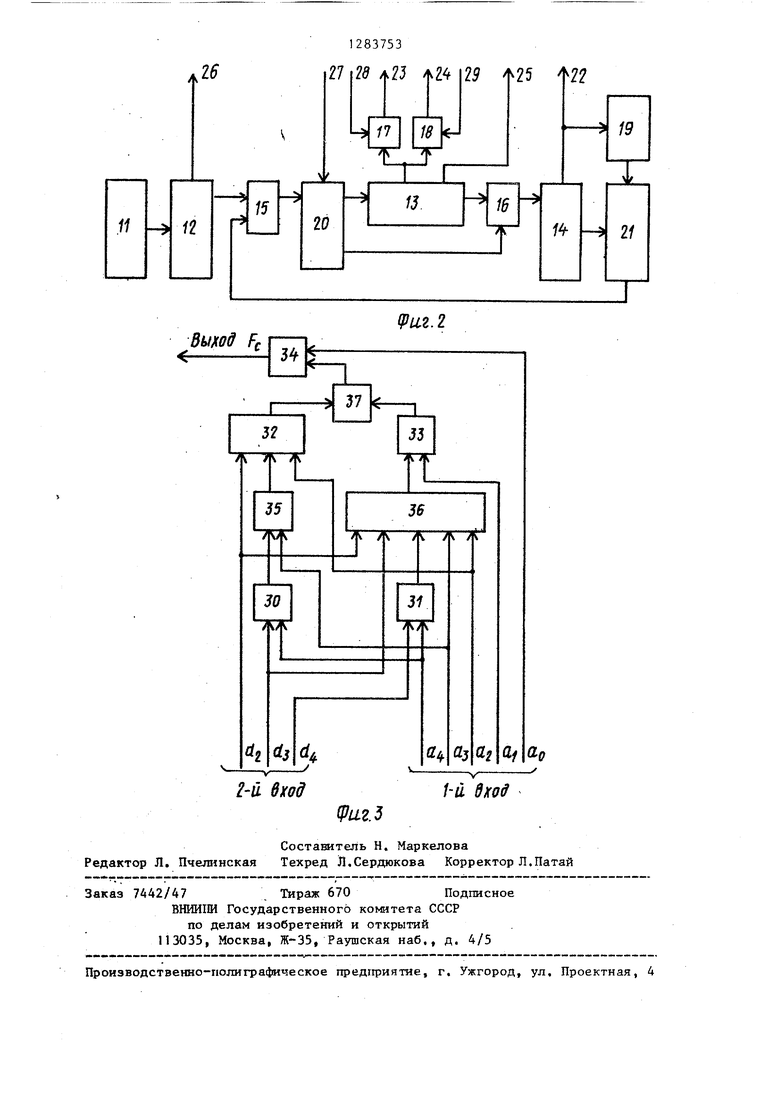

Ha фиг. 1 представлена блок-схе- ма предлагаемого устройства; на фиг, 2 - функциональная схема блока управления; на фиг, 3 - функциональная схема формирователя сигнала сдвига.

Устройство содержит регистр 1 делителя, регистр 2 делимого, регистр 3 частного, сумматор 4, блок 5 управления, триггер 6, коммутатор 7, формирователь 8 сигнала сдвига, вход 9 и выход 10 устройства.

Блок 5 управления образуют генератор П импульсов, распределители 12 - 14 импульсов, элементы ИЛИ 15- и 16, элементы И 17 и 18, счетчик 19, коммутатор 20, Дешифратор 21 нуля, первый 22 - пятый 26 выходы и первый 27, второй 28 и третий 29 входы.

Формирователь сигнала сдвига содержит элементы И 30 - 34 и элементы ИЛИ 35-37.

Устройство выполняет деление п- разрядных нормализованных двоичных чисел, представленных в прямых кодах, частное образуется также в прямом коде. Регистры 1 и 3 имеют по одному дополнительному разряду, регистр 2 имеет два дополнительных

разряда. При этом регистры 2 и 3 содержат цепи сдвига влево, 1, может быть не сдвиговым. Сумматор 4 является (п+2)-разрядным сумматором комбинационного типа. Три г- гер 6 является обычным D-триггером с дополнительным входом начальной установки и прямым и инверсным выходами. Если триггер 6 находится в единичном состоянии, то коммутатор 7 пропускает на свой выход инверсный код пяти старших разрядов регистра 2 делимого, в противном случае - их прямой код.

Работа блока управления совпадает с работой блока управления устройства-прототипа.

Если Fj.l , то цикл деления содержит только совместный сдвиг регистров 2 и 3 влево по управляющему сигналу с выхода 22 блока 5, ес- ш F О, то в цикле предварительно выполняется сложение кодов регистров 1 и 2, а затем совместньш сдвиг содержимого регистров 2 и 3 влево. Поскольку регистр 2 содержит два дополнительных разряда, то код делимого в нем располагается сдвинутым вправо на один разряд относительно кода делителя в регистре 1, Это -объясняется тем, что при некоторых значениях остатка В- и делителя D, сложение необходимо выполнять для кодов остатка, содержащих нули в двух старших разрядах. Если триггер 6 находится в единичном состоянии (как, например, в 1-м цикле деления) и F О, то импульс проходит через выход 23 блока 5 на вход управления выдачей дополнительного кода регистра 1 делителя- дополнительный код регистра 1 представляется как его инверсный код и единичны сигнал, подаваемый на вход переноса младшего разряда сумматора 4), Если триггер 6 находится в нулевом состоянии, на сумматоре 4 производится сложение поступившего из регистра 1 прямого кода с кодом из регистра 2, Через заданный промежу ток времени появляется сигнал на втором выходе распределителя 13, который подается на вход управления приемом информации регистра 2 и на управляющий вход триггера 6, При поступлении этого сигнала производится запись в регистр 2 кода суммы, полученной на сумматоре 4, а

5 Ю

2837534

также установка триггера 6 старшим разрядом этой суммы.. При этом триггер 6 устанавливается в единичное

5

5

состояние, если старшин разряд суммы равен единице, в противном случае триггер 6 устанавливается в нулевое состояние. В каждом цикле в старшем разряде регистра 2 образуется одна цифра частного, которая передается в младший разряд регистра 3 в результате совместного сдвига этих регистров.

Количество определяемых разрядов частного за одно сложение равно трем. Число суммирований не превып+2шает -.

Формула изобретения

20

Устройство для деления двоичных чисел, содержащее регистры делимого, делителя и частного, сумматор и блок управления, причем выход регистра

частного является выходом устройства, вход устройства соединен с информационным входом регистра делителя, выход которого соединен с первым информационным входом сумматора, второй информационный вход которого соединен с выходом регистра делимого, информационный вход которого соединен с выходом результата сумматора, выход старшего разряда регистра делимого соединен со входом младшего разряда регистра.частного, первый выход блока управления соединен со входами управления сдвигом регистров делимого и частного, второй и третий

выходы блока управления соединены со входами управления выдачей соответственно дополнительного и прямого кодов регистра делителя, четвертый выход блока управления соединен

со входом управления приемом информации регистра делимого, пятый выход блока управления соединен со входом установки знакового разряда . регистра делителя, отличающ е е с я тем, что, с целью повышения быстродействия, в него введены коммутатор, триггер и формирователь сигнала сдвига, содержащий пять элементов И и три элемента ИЛИ,

причем первый вход установки триггера в 1 соединен с пятым выходом блока управления, четвертый выход которого соединен с вторым входом установки триггера в 1,информационнын вход триггера соединен с выходом старшего разряда сумматора, первый и второй информационные входы коммутатора соединены с прямым и инверсным выходами пяти старших разрядов регистра делимого, пер вый и второй разряды выхода коммута тора соединены соответственно с первыми входами первого и второго элементов И формирователя сигнала сдвига, третий и четвертый разрядь выхода коммутатора соединены с первым и вторым входами первого элемента ИЛИ, третий вход которого соединен с выходом третьего элемента И, первых вход которого соединен с пятым разрядом выхода коммутатора и первым входом четвертого элемента И второй разряд выхода регистра делителя соединен с четвертым входом первого элемента ИЛИ и первым входом пятого элемента И, второй вход которого соединен с первым входом первого элемента ИЛИ, пятый вход которого соединен с вторым входом

Состав выполняемых в цикле действий в зависимости от значений В; и D

837536

четвертого элемента И и с выходом третьего разряда регистра делителя, ВЫХОД четвертого разряда которого соединен с вторым входом третьего

5 элемента И, выход первого элемента ИЛИ соединен с вторым входом второго элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен

10 с выходом пятого элемента И, третий вход которого соединен с выходом третьего элемента ИЖ, первый вход которого соединен с вторым входом первого элемента ИЛИ, выход четвер15 того элемента И соединен со вторым входом третьего элемента ИЛИ, выход второго элемента ИЛИ соединен со вторым входом первого элемента И, выход которого соединен с первым

20 входом блока управления, второй и третий входы которого соединены с первым и вторым управляющими входами коммутатора и прямым и инверсным выходами триггера соответствен 25 ,но.

Примечание, ДК- цикл, содержащий сложение с дополнительным кодом делителя и сдвигу ПК - цикл, содержащий сложетше с Лрям,1м кодом делителя и сдвиг; С - цикл, содержащий только сдвиг; ЗК - запрещенная комбинация, при этом если ЗК расположено с левой стороны, то он не может возникнуть при положительном остатке, а если с правой стороны - то при отрицательном остатке} знаком обозначены разряды, энй1«екия которых не показывают влияния на вывор тнпа цикла.

1283753

8 Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления двоичных чисел | 1987 |

|

SU1497614A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| Устройство для деления | 1985 |

|

SU1283752A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для деления | 1988 |

|

SU1552174A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

Изобретение относится к области вычислительной техники, в частности к электронным цифровым вычислительным машинам. Устройство содержит регистры делимого, делителя и частного, сумматор, блок управления, триггер. С целью повышения быстродействия в состав устройства включены коммутатор и формирователь сигнала сдвига. Устройство выполняет операцию деления без восстановления остатка с пропуском тактов сложения по сигналу сдвига, вырабатываемому в формирователе сигнала сдвига. Использованный в устройстве способ формирования сигнала сдвига обеспечивает максимально возможное при логических методах ускорение быстродействия: математическое ожидание количества сдвигов на. одно сложение равно 3, максимально возможное количество сложений не древьш1ает половины от общего количества разрядов частного. 3 йл, .1 табл. i (Л

fpuz.l

(od FC

ipuz.2

uf Uff

2-й вход

(Риг. 5

Составитель Н. Маркелова Редактор Л. Пчелинская Техред Л.Сердюкова Корректор Л.Патай

Заказ 7А42/47Тираж 670Подписное

ВНИИ1Ш Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предгфиятие, г. Ужгород, ул. Проектная, 4

1-й дход

| Карцев М | |||

| А | |||

| Арифметика цифровых машин | |||

| - М.: Наука, 1969 | |||

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1987-01-15—Публикация

1985-06-25—Подача