(5) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1979 |

|

SU809176A1 |

| Устройство для деления | 1983 |

|

SU1130860A1 |

| Устройство для деления | 1983 |

|

SU1166100A1 |

| Устройство для прогнозирования состояния технических объектов | 1982 |

|

SU1104533A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для деления с самоконтролем | 1987 |

|

SU1559346A2 |

| Устройство для деления | 1980 |

|

SU928344A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

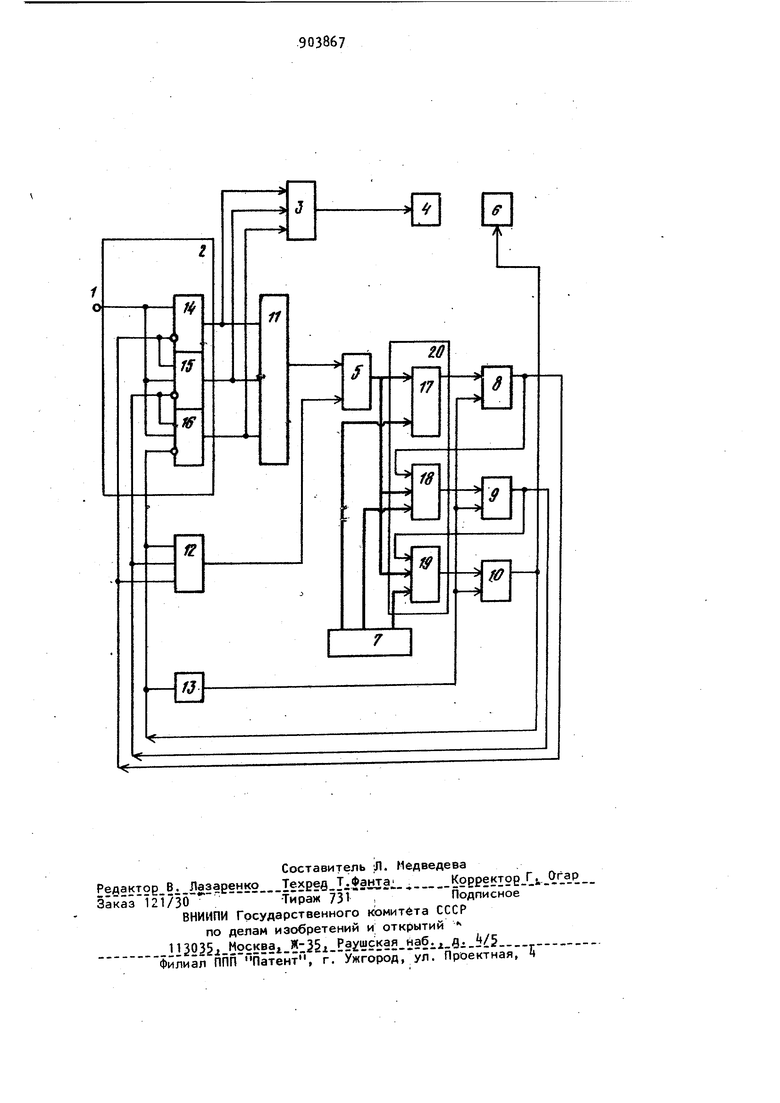

Изобретение относится к вычислительной технике и может быть исполь-; зовано Б автоматизированных цифровых системах обработки данных. Известно устройство для деления, содержащее регистр делимого, регистр делителя, буферный регистр, ключ, триггер, счетчик, блок фиксации окончания деления, распределитель импульсов, две группы элементов И и элемент ИЛИ l. Однако это устройство имеет низкую надежность и недостаточное быстродействие, избыточность оборудования и сложное конструктивное исполнение отдельных элементов. Кроме того, в устройстве для деления при наличии в делителе хотя бы двух находящихся рядом нулей в процессе деления возникает сбой, так как одновременно срабатывают два (или больше - по количеству рядом,стоящих нулей) соседних элемента И, а на вход распределителя через элемент ИЛИ поступит только один запускающий его сигнал, которой подключит выход распределителя на следующий очередной) разряд регистров делимого и делителя в то время, как необходи ю подключит выход к более. старшему ( ненулевомуу разряду. Этот сбой внесет погрешность в результат деления. При наличии нуля во всех разрядах делителя, т.е. когда делитель равен нулю, в этом устройстве все равно будет производиться деление и выдаваться какой-то результат..Кроме того, из-за отсутствия в устройстве управления всеми поразрядными элемеитам И возможен (в начальный момент счета) сигнал помехи от : элемента И 4ладшего разряда регистра, работающего в направлении сложения или вычитания. Наличие в составе устройства буферного регистра с группой поразрядных элементов И, триггера управления, а также конструктивное выполнение обоих регистров делителя реверсивным существенно усложняют кон3-90струкцию устройства и его функционал ные связи. Кроме того, в этом устройстве для выполнения только одного цикла вычитания необходимо 10п счетных импуль сов, где п - число десятичных разрядов регистра делителя (буферного регистра), а для выполнения всей опера ции деления, следовательно, необходи мо 10п-т, где m - значение частного от деления, т.е. количество циклов вычитания в процессе деления дву .чисел. ; Наиболее близким по технической, сущности к предлагаемому является устройство для деления, содержащее коммутатор импульсов, счетчик делимо го, счетчик частного, блок фиксации окончания деления, блок сравнения, блок задания делителя, причем информационный вход коммутатора импульсов подключен к тактовому входу устройст ва, а выходы соединены с соответству щими поразрядными входами счетчика делимого, выход которого соединен со входом блока фиксации окончания деле ния, блок сравнения, состоящий из И поразрядных узлов сравнения, где У( число разрядов делителя, первые входы которых соединены с соответствующими поразрядными выходами блока задания делителя 2J. Недостатком известного устройства является избыточность аппаратуры. Цель изобретения - сокращение количества оборудования. Поставленная цель достигается тем что в устройство введены два элемента ИЛИ, элемент задержки, счетчик и h элементов памяти, причем выходы коммутатора импульсов соединены со входами первого элемента ИЛИ, выход которого соединен ей счетным входом счетчика, вход установки в ноль кото рого соединен с выходом второго элемента ИЛИ, поразрядные выходы счетчика соответственно соединены со вто рыми входами поразрядных узлов сравнения, выходы которых под|а1Ючены к первым входам соответствующих элементов памяти, вторые входы которых объединены и подключены к выходу эле мента задержки, выход i-ro элемента памяти (i.1,2,...,п) соединен с тре тьим входом (i+l)-ro поразрядного уз ла сравнения, с 1-им входом второго элемента ИЛИ и i-им управляющим входом коммутатора импульсов, выход И-г элемента памяти соединен со входом счетчика частного, входом элемента задержки, с п-ым входом второго элемента ИЛИ и -п-ым управляющим входом коммутатора импульсов. На чертеже представлена структурная схема устройства. Устройство для деления содержит тактовый вход 1 , коммутатор 2 импульсов, счетчик 3 делимого, блок Ц фиксации окончания деления, счетчик 5, счетчик 6 частного, блок 7 задания кода делителя, элементы 8-10 памяти, элементы ИЛИ.11, 12, элемент 13 задержки, группа элементов И , поразрядные узлы 17-19 сравнения блока 20 сравнения. Блок 7 задания кода делителя может быть выполнен, например, в виде коммутатора, подключающего один из регистров, в которые записано в параллельном коде значение делителя, или в виде регистра. Тактовый вход устройства связан с поразрядными входами счетчика 3 делимого и элемента ИЛИ . 11 через коммутатор 2 импульсов, выход счетчика 3 делимого соединен с входом блока k фиксации окончания деления, выход счетчика 5 соединен с первыми входами поразрядных узлов 17-19 сравнения, вторые входы крторых соединены с соответствующими поразрядными выходами блока 7 задания кода-делителя, а выходы соединены соответственно с первыми входами элементов 8-10 памяти, вторые входы которых объединены и подключены к выходу элемента 13 задержки, вьЫод элемента 8 памяти соединен с третьим входом поразрядного узла 18 сравнения, с первым входом элемента ИЛИ 12 и первым управляющим входом коммутатора 2 импульсов, выход элемента 9 памяти соединен с третьим входом поразрядного узла 19 сравнения, вторым входом элемента ИЛИ 12 и вторым управляющим входом коммутатора 2 импульсов, выход элемента памяти 10 соединен с входом счетчика 6 частного, входом элемента 13 задержки, третьим входом элемента ИЛИ 12 и третьим управляющим входом коммутатора 2 импульсов, выход элемента ИЛИ 11 соединен со счетным входом счетчика 5 вход установки в ноль которого соединен с выходом элемента ИЛИ 12. Коммутатор 2 импульсов по сигналам с поразрядных узлов 17-19 сравнения обеспечивает коммутацию счетных цепей для прохождения счетных импульсов в счетчик 3 делимого и в счетчик 5, форми ование сигналов обнуления счетчика 5 и элементов памяти. Поступление тактовых импульсов в него осуществляется через тактовый вход 1 устройства по сигналам с блока Ц фиксации окончания деления например, с помощью элемента И (не показано). Коммутатор 2 импульсов содержит в представленном варианте группу эле ментов И (по количеству разрядов делителя), сигнальные входы кото рых соединены с тактовым входом, а выходы соединены с поразрядными входами счетчика 3 делимого и через эле мент ИЛИ 11 со счетным входом счетчи ка 5. В зависимости от управляющих сигналов с выходов поразрядных узлов 17 19 сравнения через элемен ты 8-10 памяти на соответствующие уп равляющие входы коммутатора 2 импуль сов (входы элементов И ) коммутатор 2 импульсов выдает на выход счетные импульсы. Сигналы с выходов элементов 8-10 памяти через второй элемент ИЛИ 12 подаются на вход установки в ноль счетчика 5. Элемент ИЛИ 12 и элемент 13 задержки могут быть выполнены, например, по резистивно-емкостной схеме, которая по перепаду напряжения на входной шине на выходе формирует импульс определенных длительности и амплитуды. Устройство работает следующим образом. После зёпуска устройства тактовые импульсы через тактовый вход 1 поступают по информационному входу ком мутатора 2 импульсов на сигнальные входы элементов И , на управляю щие входы которых поданы сигналы с элементов 8-10 памяти. Если код дели теля по первому ( младшему) выходу блока 7 задания кода делителя не равен нулю, элемент 8 нахбдится в состо янии О и сигнал с его выхода разре шает прохождение импульсов через эле мент И 14 по шине младшего разряда на вход счетчика 3 делимого и через элемент ИЛИ 11 на счетный вход счетчика 5. Эти импульсы подаются до тех пор, пока состояние счетчика 5 не ста нет равным коду младшего разряда делителя, подаваемого из блока 7 задания кода делителя. В момент равенства на входе поразрядного узла 17 676 сравнения кодов, лоступающих из счетI чика 5 и блока 7 задания кода делителя, он формирует выходной сигнал, ус1 элетанавливающий в состояние мент 8 памяти, выходной сигнал которого поступает в коммутатор 2 импульсов, и через элемент ИЛИ 12 устанавливает счетчик 5 в исходное (нулевое) состояние и переключает импульсы на шину следующего ( второго ) разряда счетчика 3 делимого (отключает элемент И 14 и подключает элемент И 15). Сигнал с выхода элемента 8 памяти поступает также на вход поразрядного УЗла 18 сравнения следующего разряда б качестве разрешения. Тактовые импульсы через элемент И 15 коммутатора 2 импульсов проходят теперь на счетный вход второго разряда счетчи 3 делимого и через элемент. ИЛИ 11. , на счетный вход счетчика 5, Состояние счетчика 5 сравнивается на поразрядном узле 18 сравнения с кодом второгоразряда делителя, поступающего из блока 7 задания делителя. В мо|Мент совпадения поступающих кодов на (выходе поразрядного узла 18 сравнения формируется сигнал, который устанав-. ливает элемент 9 памяти в состояние 1. Сигнал с последнего поступает на вход следующего поразрядного узла 19 сравнения и на следующий вход коммутатора 2 импульсов для переклю- чения разрядов . Этот сигнал снова переключает канал счета счетчика 3 делимого, отключает элемент И 15, включает элемент И 16 и через элемент ИЛИ 12 устанавливает счетчик 5 в исходное состояние. Работа ярюдолжается по вышеуказанному принципу. При совпадении кодов на входе последнего поразрядного узла 19 сравнения элемент 10 памяти устанавливается в состояние 1, записывая при этом Т счетчик 6 частного. Сигнал с выхода элемента 10 памяти поступает также в. коммутатор 2 импульсов, переключая каналы на выходе с на 1-ый (отключает элемент И 16 и включает элемент И 14), и устанавливает в исходное состояние через элемент ИЛИ 12 счетчик 5, через элемент задержки 13 элементы памяти 8-10. После этого начинается второй цикл вычитания кода делителя (поступающего из блока 7 задания кода делителя) из кода делимого, хранящегося в счетчике 3 делимого. Процесс будет продолжаться до момента перехода кода делимого через нуль, в результате чего сработает блок k фиксации окончания деления и операция деления на этом закончится. В счетчике 6 частного будет зафиксировано значение частного от деления двух чисел. Если в одном или нескольких разрядах делителя будут нулевые значения, то в процессе деления сработают одновременно один или несколько рядом стоящих групповых разрядных элемент О8 И и, соответственно, элементов памяти, и старший из них, включит коммутатор 2 импульсов на очередной Хза этими разрядами) канал счета счетчика 3 делимого - включится соответствующий ему элемент И коммутатора 2 импульсов. Поразрядные узлы 17 и 18 сравнени после первого срабатывания могут ерабатывать еще при сравнении кода счет чика 5 с кодом более старших разрядов (второго и третьего, однако это не повлияет на состояние находящегос в состоянии 1 элемента памяти В и и сбоев в работе устройства не произойдет . Если во всех разрядах делителя бу дут нули, т.е. делитель равен нулю, Деление не будет производиться, так kaK все элементы Б-10 памятей будут находиться в состоянии t - под-постоянным воздействием сигналов с выходов соответствующих поразрядных уз лов сравнения и, следовательно на управляющих входах элементов И l 16 коммутатора 2 импульсов будут запрещающие сигналы. Таким образом, введение в предлагаемое устройство счетчика 5 с использованием описанной выше организд цией связей между блоками позволяет получить возможность выполнения этим устройством тех же функций, что и известным, но при значительном сокра щении состава оборудования. Формула изобретений Устройство для деления, содержащее коммутатор импульсов, счетчик де лимого, счетчик частного, блок задания кода делителя, блок сравнения и блок фиксации окончания деления,причем информационный вход коммутатора импульсов подключен к тактовому входу устройства, а выходы соединены с соответствующими поразрядными входами счетчика делимого, выход которого соединен со входом блока фиксации окончания деления, блок сравнения, состоящий из И поразрядных узлов сравнения, где И - число разрядов делителя, первые входы которых соединены с соответствующими поразрядными выходами блока задания делителя, отличающееся тем, что, с целью сокращения количества оборудования, в него введены два элемента ИЛИ, элемент задержки, счетчик и И элементов памяти, причем выходы коммутатора импульсов соединены со входами первого элемента ИЛИ, выход которого соединен со счетным входом счетчика, вход установки в ноль которогхэ соединен с выходом второго элемента ИЛИ, поразрядные выходы счетчика соответственно соединены со вторыми входами поразрядных узлов сравнення, выходы которых подключены к первым входам соответсетвующих элементов памяти, вторые входы которых объединены и подключены к выходу элемента задержки, выход i-ro элемента (i 1,2,...,п) соединен с третьим входом (|+1)-го поразрядного узла сравнения, с 1-им щХодом второго элеMeHta ИЛИ и i-им управляющим входом коммутатора импульсов, выход п-го элемента памяти соединен со входом счетчика частного, входом элемента задержки, с И-ым входом второго эле (Мента ИЛИ и И-ым управляющим входом коммутатора импульсов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР tf , кл. G 06 F 7/39, 1977. 2.Авторское свидетельство СССР по заявке № 27867 Vl8-2, кл, G Об F 7/52, 1979 (прототип).

Авторы

Даты

1982-02-07—Публикация

1980-06-25—Подача