, 11

Изобретение относится к вычисли- тельной технике и может быть использовано в системах автоматики и ЭВМ, функционирующих в системе остаточiHbix классов (СОК). .

Известно устройство для .обнаружения и исправления ошибок в системе остаточных классов, содержащее входные регистры, преобразователь в позиционный код,блок сверткипо контрольным основаниям, схему сравнения, лок выделения ошибочного основания, сумматор, блок хранения поправок, . группу дешифра оров, группу элементов ИЛИ, группу схем сравнения lj .

Недостатками данного устройства являются большое количествЬ оборудования и низкое быстродействие.

Наиболее близким по технической сущности к изобретению является устройство для обнаружения ошибок в системе остаточных классов, содержащее группу входных регистров, первую группу сумматоров по модулю, вторую группу сумматоров по модулю, элемент ИЛИ, причем выходы входных регистров группы подключены к первым входам сумматоров по модулю первой группы, вторые входы которых являются -входами констакт устройства, а выходы подключены к первым входам сумматоров по модулю второй группы, вторые входы которых подключены к выходу первого входного регистра группы, а выходы соединены с соответствующими входами элемента ИЛИ, выход которого является выходом устройства 2J

Известное устройство позволяет обнаруживать ошибки в системе остато,ч ных классов.

Недостатком его являются низкие функциональные возможности, заключающиеся в неспособнс сти исправлять ошибки.

Цель изобретения- расширениефункциональных возможностей за счет исправления однократных ошибок.

Поставленная цель достигается тем, что устройство для контроля инфор мации в системе остаточных классов, содержащее входной регистр, первую группу сумматоров по модулю, вторую . группу сумматоров по модулю и элемент ИЛИ, причем выходы разрядов с второго по п-й (п - число основаНИИ) входного регистра соединены соответственно с первыми входами 1 сумматоров по модулю первой группы.

172

вторые входы которых соединены соответственно с входами е второго по п-й модулей устройства, выходы сумматоров по модулю первой группы соединены с первыми входами соответствующих сумматоров по модулю второй группы, выход первого разряда входного регистра соединен с вторым входом первого сумматора по модулю второй группы, содержит группу дешифраторов группу элементов памяти, группу шифраторов , третью группу сумматоров по модулю, два сумматора по модулю и коммутатор, причем выходы разрядов с второго по (п-1)-й входного регистра соединены с вторыми входами соответствующих сумматоров по модулю второй группы, первый и второй входы первого сумматора по модулю соединены соответственно с выходом первого входного регистра и с входом первого модуля устройства, первый и второй входы второго сумматора по модулю соединены соответственно с выходом первого сумматора по модулю и выходом п-го разряда входного регистра, выходы сумматоров по модулю второй группы и выход второго сумматора по модулю соединены соответственно с входами дешифраторов группы, выходы которых соединены с первыми адресными входами соответствующих элементов памяти группы и с вторыми адресными входами последующих элементов памяти группы, выходы элементов памяти группы соединены с входами соответствующих шифраторов группы, выходы которых соединены с соответствующими входами элемента ИЛИ и с перг выми входами соответствукидих сумматоров по модулю третьей группы, вторые входы которых, соединены с выходами соответствующих разрядов входного регистра и с первой группой информационных входов коммутатора, вторая группа информационных входов которого соединена с выходами сумматоров по модулю третьей группы, управляющий вход и выход коммутатора соединены соответственно с выходом элемента ИЛИ и выходом устройства.

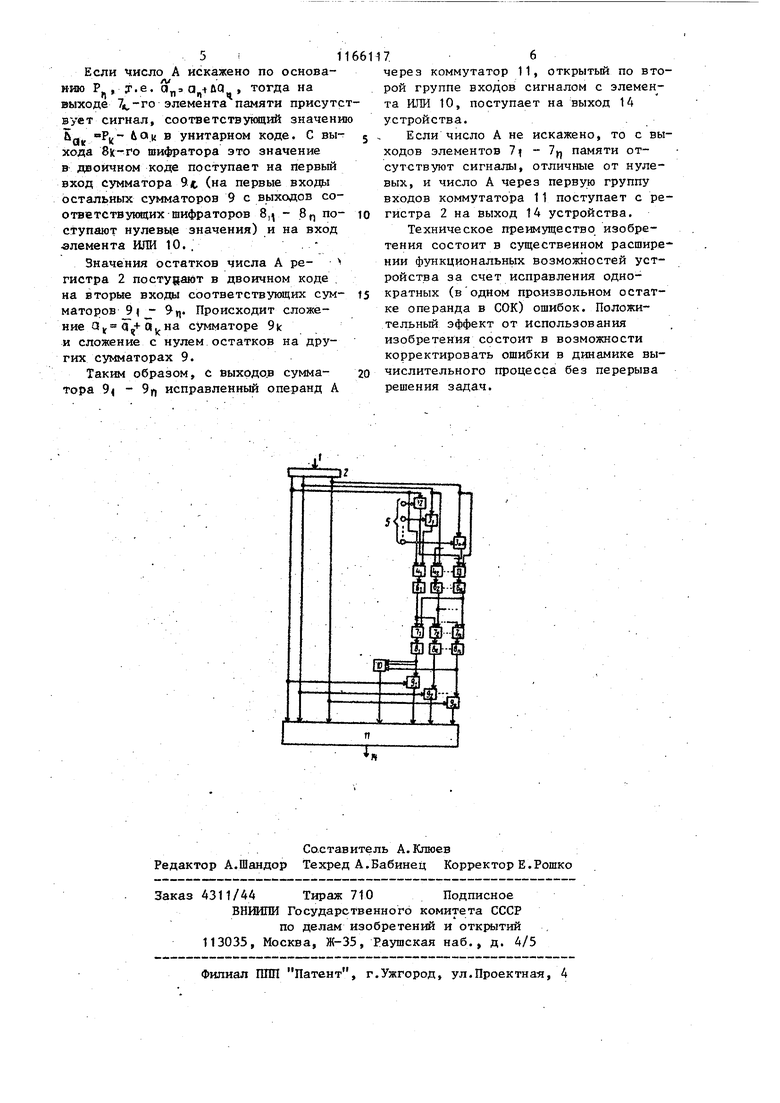

На чертеже представлена схема устройства для контроля информации в системе остаточных классов.

Устройство для контроля информации в системе остаточных классов содержит вход 1 устройства, входной регистр 2, первую группу суммато31

ров 3, - Зп-, по модулю, вторую Группу сумматоров А( - 4п- ° модулю, входы 5 модулей устройства, группу дешифраторов 6 - бу,, группу элементов 7, - 7„ памяти, группу 8 - 8yj шифраторов, третью группу сумматоров 9, - 9ц по модулю, элемент. ИЛИ 10, коммутатор 11, первый сумматор 12 по модулю, второй сумматор 13 по модулю, выход 14 устройства.

Сумматоры 12, 3, - 3.jпо модулю работают соответственно по модулям Р - Р . Сумматоры 4 , - 4n-ino модулю работают соответственно по модулям d, (, (РК, Pk4 наибольший общий делитель оснований Р,(, P,f4-i ( - n-1). Сумматор 13 по модулю работает по модулю d , . Сумматоры 9 - 9 работают соответственно по модулям Р - Р. Основания Р - Р попарно непростые.

Устройство для контроля информации в системе остаточных классов работает следующим образом.

По входу 1 устройства в регистр 2 заносится исходный операнд в СОК

Элемент 7 памяти

Lii

ая

ла, 1

74 .

А(а, aj, ..., а), представленный по основаниям Р,, Р, ..., Р. С выхода регистра 2 значение остатков в двоичном коде поступает на первые входы соответствующих сумматоров 3, - З.и 12 и вторые входы сумматоров 4. - 4„.,и 13. На вторые входы сумматоров 3 - 3„.и 12 по входам 5 в двоичном коде поступают соответствующие значения оснований, сумматоры 3 - 3., , 12 инвертируют по модулю Р)( значение остатков а|, т.е. . На первые входы сумматоров 4ц поступают значения а, , а на первый вход сумматора 13 поступает значение а.. С выходов сумматоров 4 значения (а,+а., )modd , х, через соответствующие дешифраторы 6 - 6., в унитарном коде поступают на соответствующие входы элементов 7 и 7|f., памяти. С выхода сумматора 13 через дешифратор 6, значение аг,,() mod dn.B унитарном коде поступЖё на соответствующие входы первого и п-го элементов памяти.

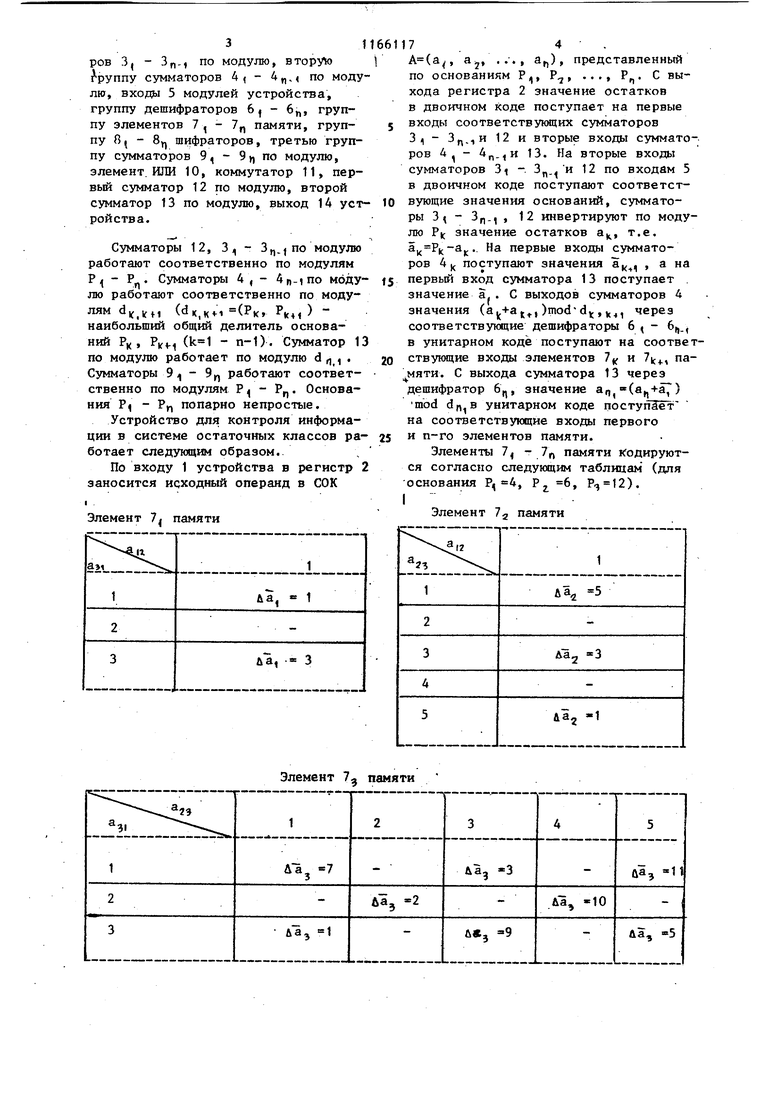

Элементы 7 - 7 памяти кодируются согласно следующим таблицам (для основания Р, 4, Р 6, Р, 12).

Элемент 7, памяти

42

П

Л а. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1989 |

|

SU1633497A1 |

| Устройство для умножения чисел по модулю | 1981 |

|

SU976440A2 |

| Преобразователь перемещения в код системы остаточных классов | 1984 |

|

SU1259487A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968813A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для обнаружения ошибок в слабоарифметическом коде системы остаточных классов | 1984 |

|

SU1166116A1 |

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1166098A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИНФОРМАЦИИ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ, содержащее входной регистр, первую группу сумматоров по модулю, вторую группу сумматоров по модулю и элемент ИЛИ, причем выхода разрядов с второго по п-и (и - число осг нований) входного регистра соединены соответственно с первыми входами . , сумматоров по модулю первой группы, вторые входы которых соединены соот- . ветственно с входами с второго по П-й модулей устройства, выходы сумматоров по модулю первой группы соединены с первь1ми входами соответствующих сумматоров по модулю второй группы, выход первого разряда входаого регистра .соединен с вторым входом первого сумматора по модугао второй . группы, отличающееся тем что, с целью расширения функциональных возмо жностей за счет исправления однократных ошибок, оно содержит группу дешифра;торов, группу элементов памяти, группу шифраторов, третью группу сумматоров по модулю, два сумматора по модулю и коммутатор, причем выходы разрядов с второго по (п-1)-й входного регистра соединены . с вторыми входами соответствующих сумматоров по модулю второй группы, первый и второй входы первого сумматора по модулю соединены соответственно с выходом первого разряда вход7 ного регистра и с входом первого модуля устройства, первый и втйрой входы второго сумматора по модулю соединены соответственно с выходом первого сумматора по модуле и выходом П- го разряда входного,регистра, выходы сумматоров по модулю второй группы и выход второго сумматора по модулю соединены соответственно с входами дешифраторов групсл пы, выходы которых соединены с первыми адресными входами соответствукмцих элементов памяти группы и с вторыми адресными входами по еледующих элементов памяти группы, выходы элементов памяти группы сое- , динены с входами соответствующих шифраторов группы, выходы которых Од соединены с соответствующими входаОд ми элемента ИЛИ и с первыми входами соответствующих сумматоров по модулю третьей группы, вторые входы которых соединены с выходами соответст- . вующих разрядов входного регистра и с первой группой информационных входов коммутатора, вторая группа информационных входов которого сое динена с выходами сумматоров по модул третьей группы, управляющий |вход и выход коммутатора соединены соответственно с выходом злемен:та ИЛИ и выходом устройства.

ul, 3

Элемент 7 памяти

Aaj 7

Ла, 1

ла 3

Ла, «3

П

Ла, «10

ба 2

Ла, 5

9 1 Если число А искажено по основа ию Р ,у.е. , тогда на выходе 7«,-го элемента памяти присутс вует сигнал, соответствующий значени Ь v в унитарном коде. С выхода 8tc-ro шифратора это значение в двоичном коде поступает на первый вход сумматора 9ч (на первые входы остальных сумматоров 9 с выходов соответствующих шифраторов 8, - 8f, поступают нулевые значения) и на вход элемента ИЛИ Ю. . Значения остатков числа А ре- гистра 2 поступают в двоичном коде на вторые входы соответствующих сумПроисходит сложематоров 9 ние а сумматоре 9k и сложение с нулем остатков на других сумматорах 9. Таким образом, с выходов сумматора 9( - 9п исправленный операнд А 76 через коммутатор 11, открытый по второй группе входов сигналом с элемен та ИЛИ 10, поступает на выход 14 устройства.. Если число А не искажено, то с выходов элементов 7| - 7 памяти отсутствуют сигналы, отличные от нулевых, и число А через первую группу входов коммутатора 11 поступает с регистра 2 на выход Н устройства. Техническое преимущество изобретения состоит в существенном расширении функциональных возможностей устройства за счет исправления однократных (водном произвольном остатке операнда в СОК) ошибок. Положительный эффект от использования изобретения состоит в возможности корректировать ошибки в динамике вычислительного процесса без перерыва решения задач.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1980 |

|

SU960823A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для обнаружения одиночных ошибок кода в системе остаточных классов | 1981 |

|

SU964645A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-07—Публикация

1984-01-27—Подача