(5) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1059573A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1015383A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Процессор | 1985 |

|

SU1280378A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

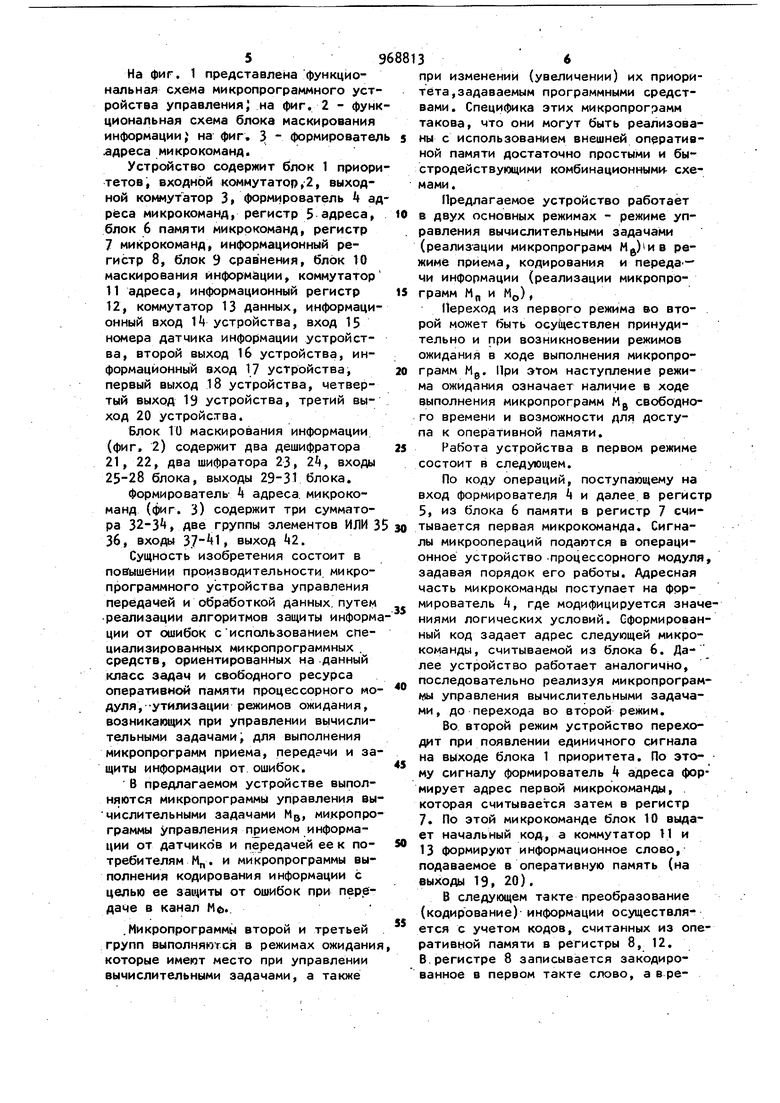

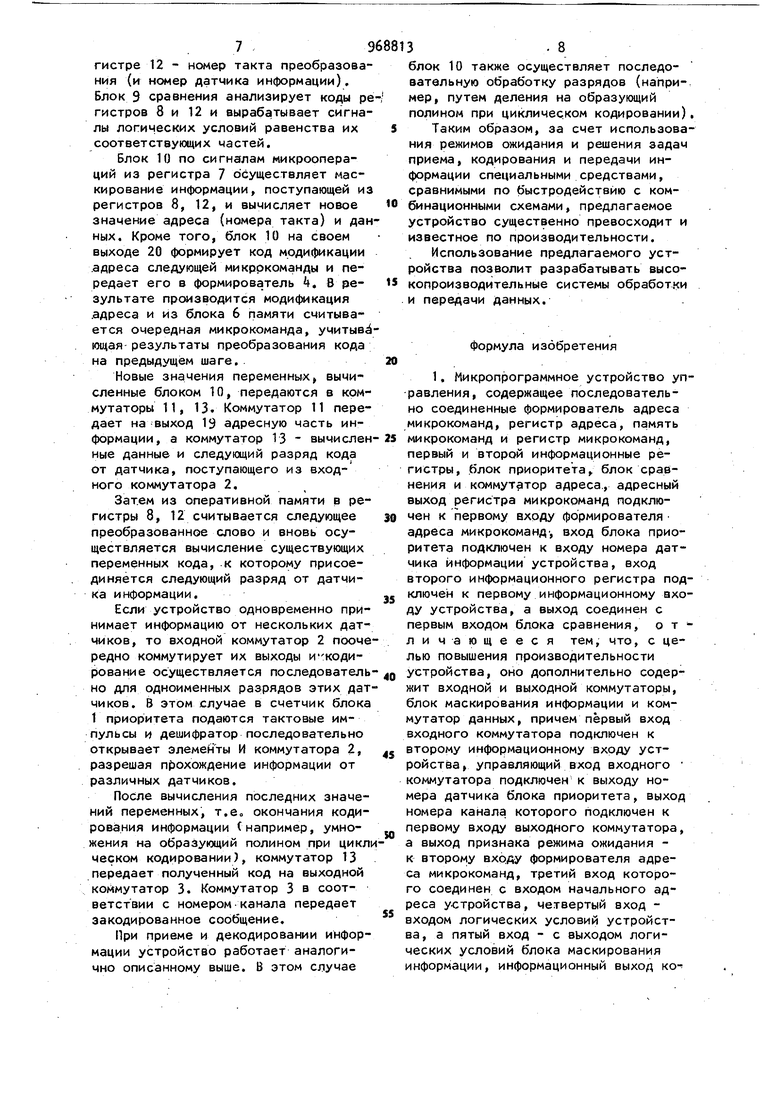

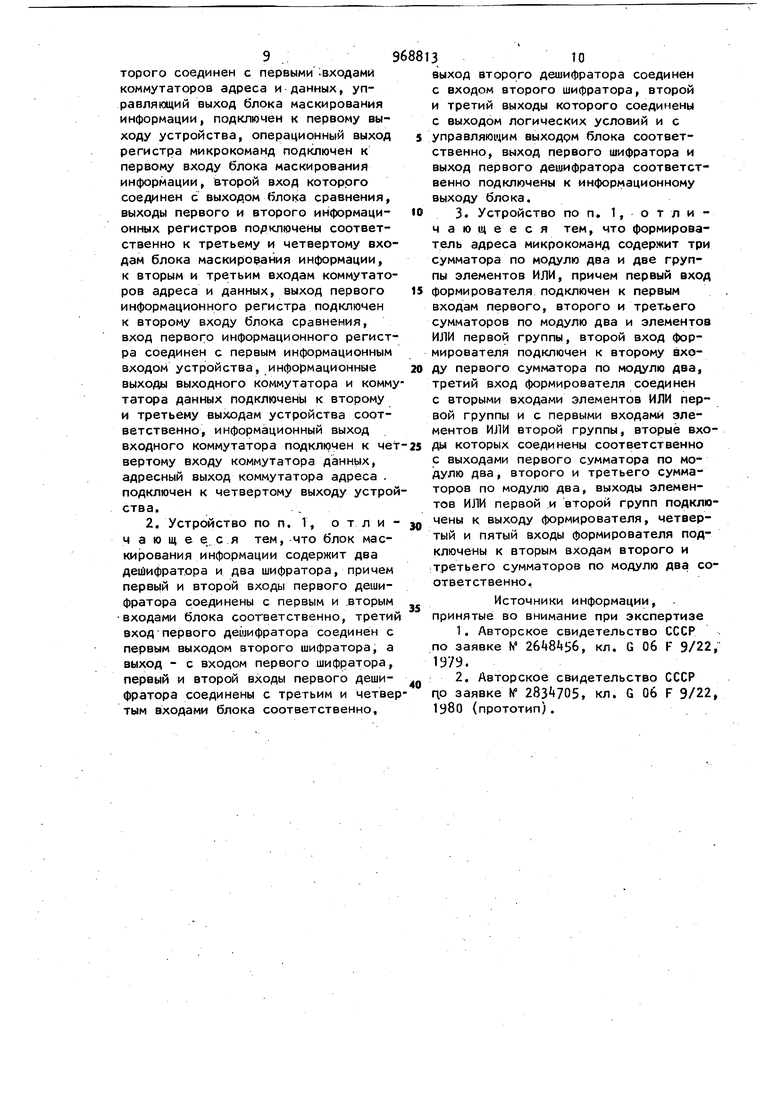

Изобретение относится к цифровой вычислительной технике и может быть использбвано при разработке распределенных вычислительных и управляющих систем а качестве микропрограммного устройства управления обработкой данных в процессорных мо дулях и передачей информации между модулями с защитой от ошибок. Известно микропрограммное устройство управления, содержащее коммутатор, регистры адреса и микрокоманд, блок памяти микрокоманд, ре гистр данных (l3. Недостатком устройства является низкая производительность, обусловленная сложностью реализации алгоритмов защиты от ошибок и отсутстви ем средств, обеспечивающих непосред ственный прием и передачу данных. Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому изобретению является устройство,.содерж щее коммутатор адреса, первый информационный регистр, последовательно соединенные формирователь адреса микрокоманд, регистр адреса, регистр микрокоманд, блок памяти микрокоманд, регистр микрокоманд, первый выход которого соединен с первым входом формиpoвateля адреса микрокоманд, блок приоритета, вход которого является первым входом устройства, второй информационный регистр, вход которого является вторым входом устройства, а выход - соединен с первым входом блока сравнения C2J. Недостатком устройства является низкая производительность, обусловленная отсутствием специальных средств реализации алгоритмов защиты информации от ошибок и использованием для этого внешних операционных устройств, не ориентированных на данный класс задач, невозможностью использования режимов ожидания, возникающих при /правлении выполнением вычислительных задач, для управления решением задач приема, передачи информации и защиты её от ошибок и перераспредел ния вычислительных мощностей процес сорного модуля. Целью изобретения является повышение производительности микропрограммного устройства управления передачей и обработки данных. Поставленная цель достигается тем, что в устройство, содержащее последовательно соединенные формирователь адреса микрокоманд, регистр адреса, память микрокоманд и регистр микрокоманд, первый и второй информационные регистры, блок приоритс та, блок сравнения и коммутатор адреса, адресный выход регистра микрокоманд подключен к первому входу фор мирователя адреса микрокоманд, вход блока приоритета подключен к входу, номера датчика информации устройства , вход второго информационного регистра подключен к первому Информационному входуустррйства, а выХ.ОД соединен с перйым входом блока сравнения, дополнительно введены вхр ной и выходной коммутаторы, блок мас кирования информации и коммутатор данных, причем первый вход входного коммутатора подключен к второму информационному входу устройства, управляющий вход входногр коммутатора ,подключен к выходу номера датчика бл ка приоритета, выход номера канала которого подключен к первому входу выходного коммутатора, а выход признака режима ожидания - к второму входу формирователя адреса микрокоманд, третий вход которого соединен с входом начального адреса устройства, четвертый вход - с входом логических условий устройства, а пятый вход - с выходом логических условий блока маскирования информации, инфор мационный выход которого соединен с первыми входами коммутаторов адреса и данных, управляющий выход блока ма кирования информации подключен к пер вому выходу .устройства, операционный выход регистра микрокоманд подключен к первому - входу блока маскирования информаци, второй вход которого соединен с выходом блока срав нения, выходы первого и второго информационных регистров подключены соответственно к третьему и четвертому входам блока маскирования инфор мации, к вторым и третьим входам ком мутатора адреса и данных, выход первого информационного регистра подключен к вторрму входу блока сравнения, вход первого информационного регистра соединен с первым информационным входом устройства, информационные выходы выходного коммутатора и коммутатора данных подключены к второму и третьему выходам устройства соответственно, информационный выход входного коммутатора подключен к четвертому входу коммутатора данных, адресный выход коммутатора адреса подключен к четвертому выходу устройства. При этом блок маскирования информации содержит два дешифратора и два шифратора, причем первый и второй входы первого дешифратора соединены с первым и вторым входами блока соответственно, третий вход первого дешифратора соединен с первым выходом второго шифратора, а выход - с входом первого шифратора, первый и второй входы первого дешифратора соединены с третьим и четвертым входами блока соответственно, выход второго дешифратора соединен с входом втРрого шифратора, второй и третий выходы которого соединены с выходом логических условий и с управляющим выходом блока соответственно, выход первого шифратора и выход первого дешифратора сортветственно подключены к информационному выходу блока. Кроме трго, формирователь адреса микрокоманд содержит три сумматора по модулю два и две группы элементов, ИЛИ, причем первый вход формирова- г теля подключен к первым входам первого, второго и третьего сумматоров ; по модулю два и элементов ИЛИ первой группы, второй вход формирователя подключен к второму входу первого сумматора по модулю два, третий вход формирователя соединен с вторыми входами элементов ЙШ первой группы и с первыми входами элементов ИЛИ второй группы, вторые входы которых соединены соответственно с выходами первого, сумматора по модулю два, второго и третьего сумматоров nd модулю два, выходы элементов ИЛИ первой и второй групп подключены к выходу формирователя, четвертый и пятый входы формирователя подключены к вторым входам второго и третьего сумматоров по модулю два соответственно. 5 На фиг. 1 представлена функциональная схема микропрограммного уст ройства управления на фиг. 2 - фун циональная схема блока маскирования информации; на фиг, 3 формировате адреса микрокоманд. Устройство содержит блок 1 приор тетов, входной коммутатор,2, выходной коммутатор 3 формирователь 4 а реса микрокоманд, регистр 5 адреса, блок 6 памяти микрокоманд, регистр 7 микрокоманд, информационный регистр 8, блок 9 сравнения, блок 10 маскирования информации, коммутатор 11 адреса, информационный регистр 12, коммутатор 13 данных, информаци онный вход Ш устройства, вход 15 номера датчика информации устройства, второй выход 16 устройства, информационный вход 17 устройства, первый выход 18 устройства, четвертый выход 19 устройства, третий выход 20 устройства. Блок 10 маскирования информации (фиг, 2) содержит два дешифратора 21, 22, два шифратора 23, 2, входы 25-28 блока, выходы 29-31 блока. формирователь 4 адреса, микрокоманд (фиг. З) содержит три сумматора 32-3, две группы элементов ИЛИ 3 36, входы выход 42. Сущность изобретения состоит в пов ышении производительности микропрограммного устройства управления передачей и обработкой данных.путем реализации алгоритмов защиты информ ции от ошибок с использованием специализированных микропрограммных . средств, ориентированных на данный класс задач и свободного ресурса оперативной памяти процессорного мо дуля, -утилизации режимов ожидания, возникающих при управлении вычислительными задачами для выполнения микропрограмм приема, передачи и за щиты информации от ошибок. В предлагаемом устройстве выполняются микропрограммы управления вы числительными задачами MB, микропро граммы управления приемом информации от датчиков и передачей ее к потребителям М„. и микропрограммы выполнения кодирования информации с целью ее защиты от ошибок при передаче в канал М«.. .Микропрограммы второй и третьей групп выполняются в режимах ожидани которые имеют место при управлении вычислительными задачами, а также 36 при изменений (увеличении) их приоритета, задаваемым программными средствами. Специфика этих микропрограмм такова, что они могут быть реализованы с использованием внешней оперативной памяти достаточно простыми и быстродействующими комбинационными- схемами . Предлагаемое устройство работает в двух основных режимах - режиме управления вычислительными задачами (реализации микропрограмм М)|ив режиме приема, кодирования и переда чи информации (реализации микропрограмм Мп и Ир), Переход из перврго режима во второй может быть осу(цествлен принудительно и при возникновении режимов ожидания в ходе выполнения микропрограмм М0. При этом наступление режима ожидания означает наличие в ходе выполнения микропрограмм Mg свободного времени и возможности для доступа к оперативной памяти. Работа устройства в первом режиме состоит в следующем. По коду операций, поступающему на вход формирователя k и далее в регистр 5, из блока 6 памяти в регистр 7 считывается первая микрокоманда. Сигналы микроопераций подаются в операционное устройство процессорного модуля, задавая порядок его работы. Адресная часть микрокоманды поступает на фррмирователь Ц, где модифицируется значениями логических условий. Сформированный код задает адрес следующей микрокоманды, считываемой из блока 6. Далее устройство работает аналогично, последовательно реализуя микропрограмf(W управления вычислительными задачами, до перехода во второй режим. Во второй режим устройство переходит при появлении единичного сигнала на выходе блока 1 приоритета. По этому сигналу формирователь k адреса формирует адрес первой микрокоманды, которая считывается затем в регистр 7. По этой микрокоманде блок 10 выдает начальный код, а коммутатор 11 и 13 формируют информационное слово, подаваемое в оперативную память (на выходы 19, 20). В следующем такте преобразование (кодирование) информации осуществляется с учетом кодов, считанных из оперативной памяти в регистры 8, 12. В,регистре 8 записывается закодированное в первом такте слово, а в регистре 12 - номер такта преобразования (и номер датчика информации). Блок 9 сравнения анализирует коды р гистров 8 и 12 и вырабатывает сигналы логических условий равенства их соответствующих частей. Блок К) по сигналам микроопераций из регистра 7 осуществляет маскирование информации, поступающей из регистров 8, 12, и вычисляет новое значение адреса (номера такта) и дан ных. Кроме того, блок 10 на своем выходе 20 формирует код мрдисИкации .адреса следующей микрокоманды и передает его в формирователь k, В результате производится модификация .адреса и из блока 6 памяти считывается очередная микрокоманда, учитывё ющая результаты преобразования кода на предыдущем шаге. Новые значения переменных, вычисленные блоком 10, передаются в коммутаторы 11, 13. Коммутатор 11 передает на выход 19 адресную часть информации, а коммутатор 13 вычислен ные данные и следующий разряд кода от датчика, поступающего из входного коммутатора 2, Затем из оперативной памяти в регистры 8, 12 считывается следующее преобразованное слово и вновь осуществляется вычисление существующих переменных кода, к которому присоединяется следующий разряд от датчика информации. Если устройство одновременно принимает информацию от нескольких датчиков, то входной коммутатор 2 пооче редно коммутирует их выходы и кодирование осуществляется последователь но для одноименных разрядов этих дат чиков. В этом случае в счетчик блока 1 приор итета подаются тактовые импульсы и дешифратор последовательно открывает элементы И коммутатора 2, разрешая прохождение информации от различных датчиков. После вычисления последних значений переменных, т.е окончания кодирования информации (например, умножения на образующий полином при цикл ческом кодировании), коммутатор 13 передает полученный код на выходной коммутатор 3. Коммутатор 3 в соответствии с номером канала передает закодированное сообщение. При приеме и декодировании информации устройство работает аналогично описанному выше. В этом случае блок 10 также осуществляет последовательную обработку разрядов (например, путем деления на образующий полином при циклическом кодировании), Таким образом, за счет использования режимов ожидания и решения задач приема, кодирования и передачи информации специальными средствами, сравнимыми по быстродействию с комбинационными схемами, предлагаемое устройство существенно превосходит и известное по производительности. Использование предлагаемого устройства позволит разрабатывать высокопроизводительные системы обработки и передачи данных. Формула изобретения 1. Микропрограммное устройство управления, содержащее последовательно соединенные формирователь адреса микрокоманд, регистр адреса, память микрокоманд и регистр микрокоманд, первый и второй информационные регистры, блок приоритета, блок сравнения и коммутатор адреса., адресный выход регистра микрокоманд подключен к первому входу формирователя адреса микрокоманд, вход блока приоритета подключен к входу номера датчика информации устройства, вход второго информационного регистра подключен к первому информационному входу устройства, а выход соединен с первым входом блока сравнения, отличающееся тем, что, с целью повышения производительности устройства, оно дополнительно содержит входной и выходной коммутаторы, блок маскирования информации и коммутатор данных, причем первый вход входного коммутатора подключен к второму информационному входу устройства, управляющий вход входного коммутатора подключен к выходу номера датчика блока приоритета, выход номера канала которого подключен к первому входу выходного коммутатора, а выход признака режима ожидания к второму входу формирователя адреса микрокоманд, третий вход которого соединен с входом начального адреса устройства, четвертый вход входом логических условий устройства, а пятый вход - с выходом логических условий блока маскирования информации, информационный выход которого соединен с первыми входами коммутаторов адреса и данных, управляющий выход блока маскирования информации, подключен к первому выходу устройства, операционный выход регистра микрокоманд подключен к первому входу блока маскирования информации, второй вход которого соединен с выходом блока сравнения, выходы первого и второго информационных регистров подключены соответственно к третьему и четвертому вхо дам блока маскирования информации, к вторым и третьим входам коммутато ров адреса и данных, выход первого информационного регистра подключен к второму входу блока сравнения, вход первого информационного регист ра соединен с первым информационным входом устройства, информационные выходы выходного коммутатора и комм татора данных подключены к второму и третьему выходам устройства соответственно, информационный выход входного коммутатора подключен к че вертому входу коммутатора данных, адресный выход коммутатора адреса . подключен к четвертому выходу устро ства., 2, Устройство по п, 1, о т л и ч а ю щ е е. с я тем, что блок маскирования информации содержит два дешифратора и два шифратора, причем первый и второй входы первого дешифратора соединены с первым и .вторым входами блока соответственно, трети входпервого дешифратора соединен с первым выходом второго шифратора, а выход - с входом первого шифратора, первый и второй входы первого дешифратора соединены с третьим и четве тым входами блока соответственно. 310 выход второго дешифратора соединен с входом второго шифратора, второй и третий выходы которого соединены с выходом логических условий и с управляющим выходом блока соответственно, выход первого шифратора и выход первого дешифратора соответственно подключены к информационному выходу блока. 3. Устройство по п, 1, о Т л и чающееся тем, что формирователь адреса микрокоманд содержит три сумматора по модулю два и две группы элементов ИЛИ, причем первый вход формирователя подключен к первым входам первого, второго и третьего сумматоров по модулю два и элементов ИЛИ первой группы, второй вход формирователя подключен к второму входу первого сумматора по модулю два, третий вход формирователя соединен с вторыми входами элементов ИЛИ первой группы и с первыми входами элементов ИЛИ второй группы, вторые входы которых соединены соответственно с выходами первого сумматора по модулю два, второго и третьего сумматоров по модулю два, выходы элементов ИЛИ первой и второй групп подключены к выходу формирователя, четвертый и пятый входы формирователя подключены к вторым входам второго и третьего сумматоров по модулю два соответственно. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке N 26k8kS6, кл. G Об F 9/22, 1979. 2.Авторское свидетельство СССР заявке W , кл. G Об F 9/22, 1980 (прототип).

15 o17 о12

968813 «f

I MiMHMHHH

w

11

;i

/

Авторы

Даты

1982-10-23—Публикация

1981-05-19—Подача