1

Изобретение относится к вычислительной технике и может быть использовано, например, для ввода в ЭВМ, функционирующей в системе остаточных классов (СОК), информации, представленной перемещением.

Целью изобретения является повьппе ние точности преобразователя.

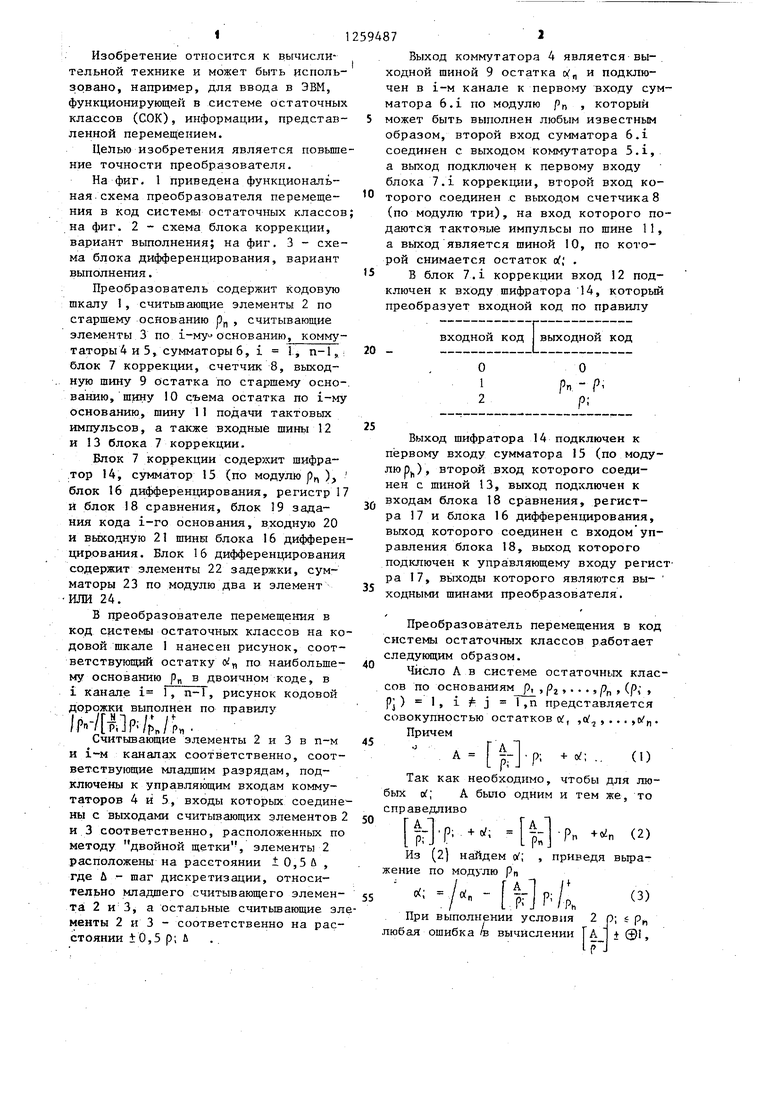

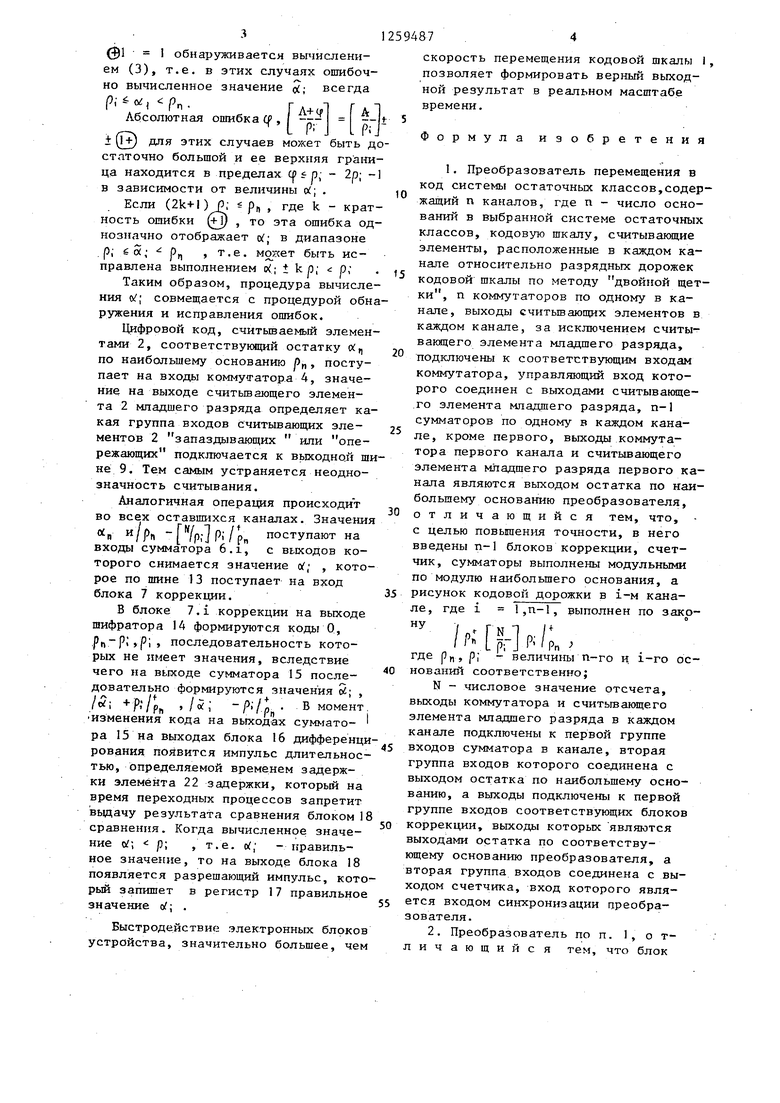

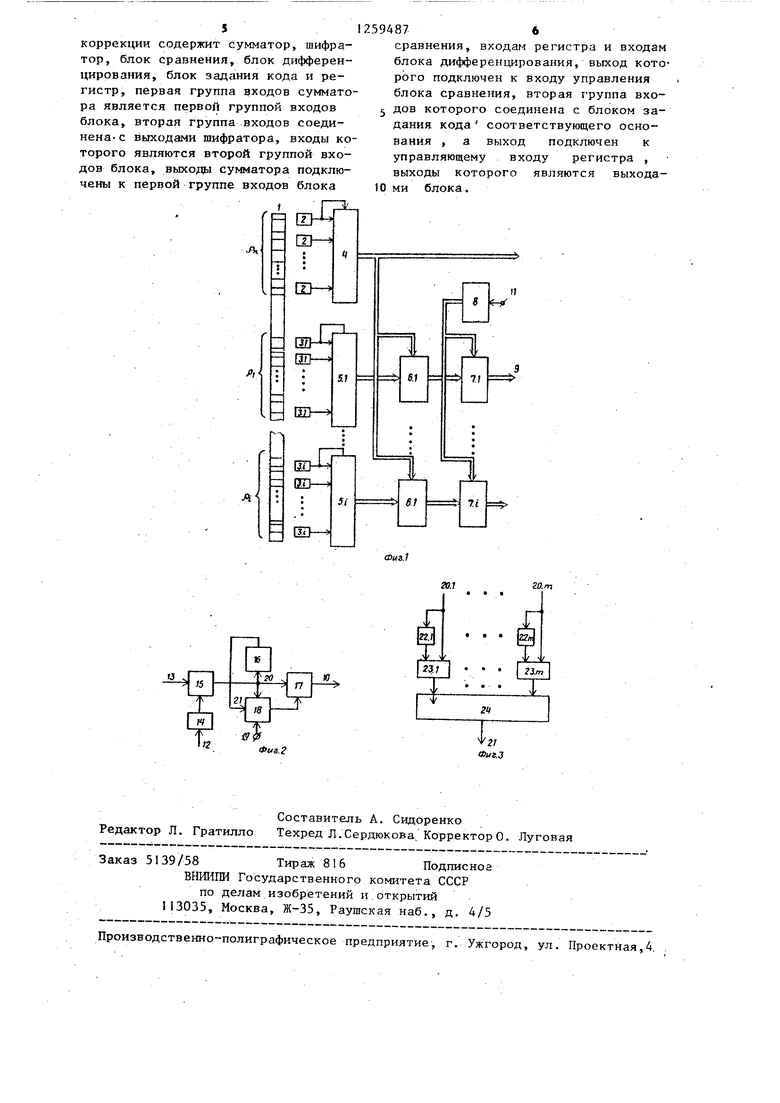

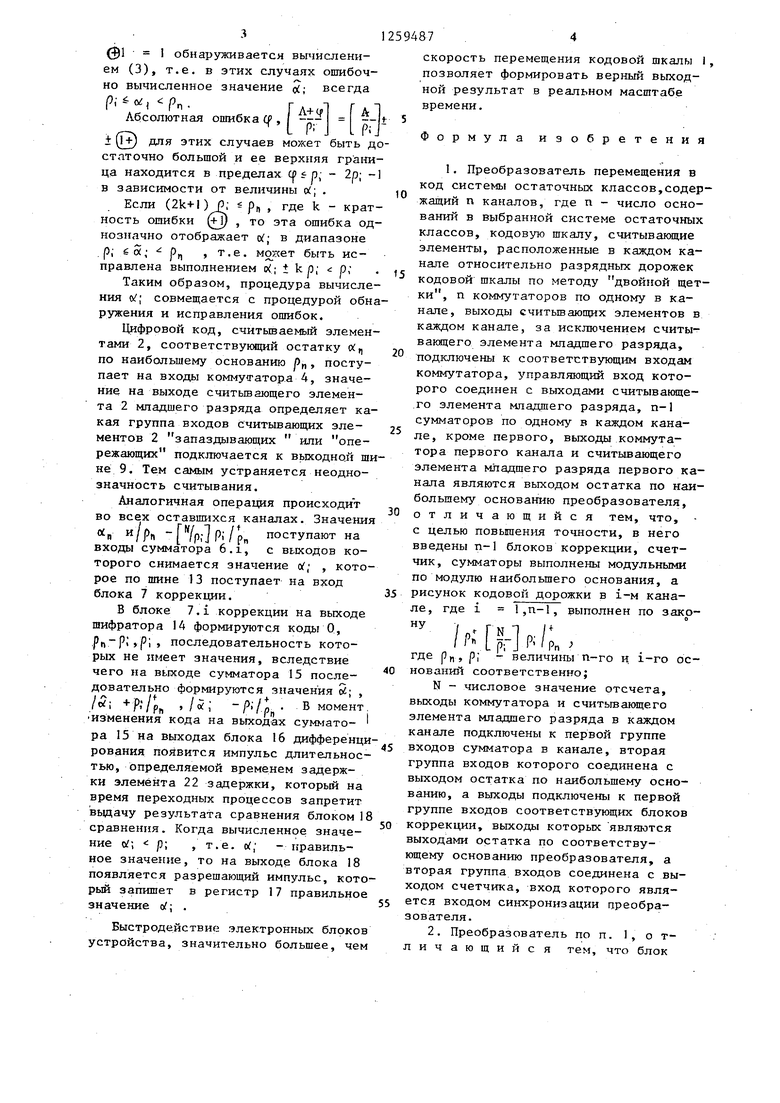

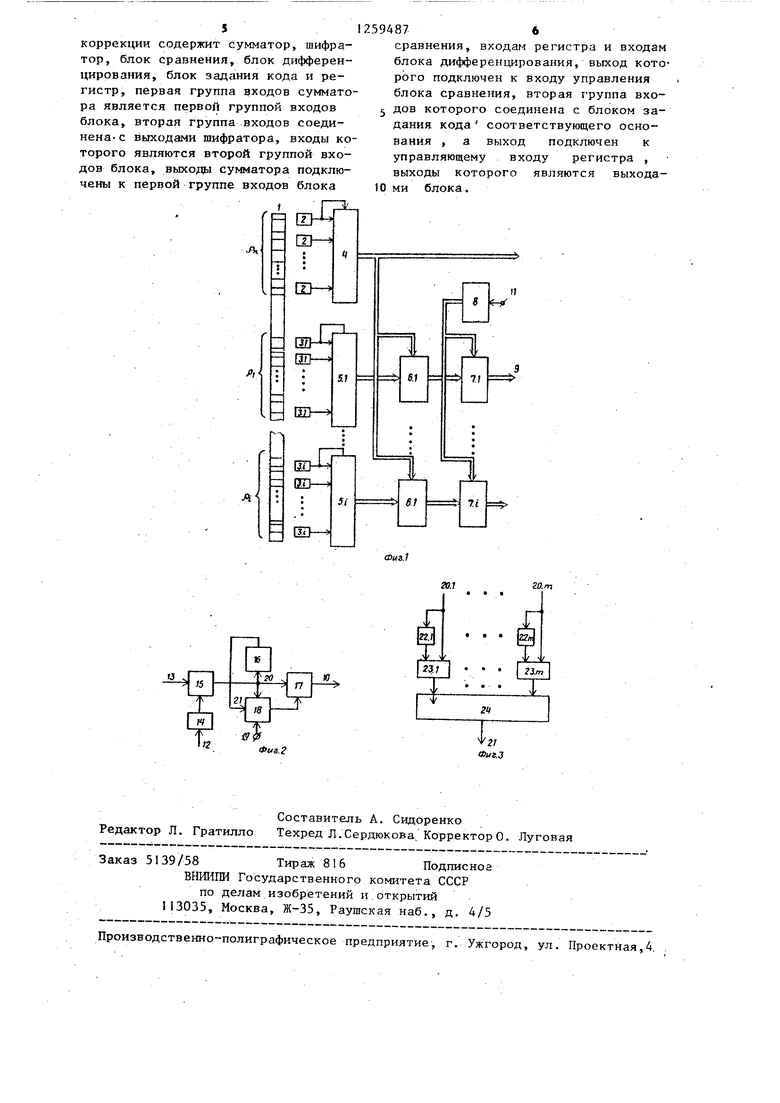

На фиг, 1 приведена функциональная, схема преобразователя перемещения в код системы остаточных классов на фиг. 2 - схема блока коррекции, вариант выполнения; на фиг, 3 - ма блока дифференцирования, вариант выполнения.

Преобразователь содержит кодовую шкалу 1, считьшающие элементы 2 по старшему основанию р , считывающие элементы 3 по i-My основанию, комму- таторы4 и 5, сумматоры б, i I, п-1„ блок 7 коррекции, счетчик 8, выходную шину 9 Остатка по старшему основанию, шину 10 съема остатка по i-му основанию, шину 11 подачи тактовых импульсов, а также входные шинь 12 и 13 блока 7 коррекции.

Блок 7 коррекции содержит шифратор 14, сумматор 15 (по модулю р )., блок 16 дифференцирования, регистр 1 И блок 18 сравнения, блок 19 зада- ния кода i-ro основания, входную 20 и вькодную 21 шины блока 16 дифференцирования. Блок 16 дифференцирования содержит элементы 22 задержки, сумматоры 23 по модулю два и элемент ИЛИ 24,

В преобразователе перемещения в код системы остаточных классов на кодовой шкале I нанесен рисунок, соответствующий остатку (xin по наибольше- му основанию р в двоичном коде, в i канале i 1, п-1, рисунок кодовой дорожки выполнен по правилу

lK/№lp /N/k.

Считывающие элементы 2 и 3 в п-м и i-M каналах соответственно, соответствующие младшим разрядам, подключены к управляющим входам коммутаторов 4 И 5, входы KOTOjpbJX соедине ны с выходами считывающих элементов и 3 соответственно, расположенных по методу двойной щетки, элементы 2 расположены на расстоянии t 0,5 U , где U - шаг дискретизации, относительно младшего считывающего элемен- та 2 и 3, а остальные считьшающие элменты 2 и 3 - соответственно на расстоянии iO,5 Р; Д

10

IS

20 -

Выход коммутатора 4 является выходной шиной 9 остатка с)„ и подключен в i-M канале к первому входу сумматора 6,1 по модулю fn который может быть выполнен любым известным образом, второй вход сумматора 6.1 соединен с выходом коммутатора 5,1, а выход подключен к первому входу блока 7,i коррекции, второй вход которого соединен с выходом счетчика 8 (по модулю три), на вход которого подаются тактовые импульсы по шине 11, а выход является шиной 10, по которой снимается остаток о(, ,

В блок 7,1 коррекции вход 12 подключен к входу шифратора 14, который преобразует входной код по правилу

входной код выходной код

О

Рп. - Г

р:

-

Выход шифратора 14 подключен к первому входу сумматора 15 (по моду- люр|), второй вход которого соединен с шиной 13, выход подключен к входам блока 18 сравнения, регистра 17 и блока 16 дифференцирования, выход которого соединен с входом управления блока 18, выход которого подключен к управляющему входу регистра 17, выходы которого являются вы- ходными шинами преобразователя.

Преобразователь перемещения в код системы остаточных классов работает следующим образом.

Число Л в системе остаточных классов по основаниям р, , р ,,, ,, /7„ , (р, , р) 1, 1 1,п представляется совокупностью остатков а;, о1 ,, .

Причем

rtrl P

+ сх ;

(О

Так как необходимо, чтобы для любых (/; А было одним и тем же, то справедливо

Из (2) найдем о/ , приведя выражение по модулю РП

-/«--ШР /Р.

При выполнении условия 2 О; s р

любая ошибка в вычислении

А. i I / J

31259487

@1 1 обнаруживается вычислением (3), т.е. в этих случаях ошибочно вычисленное значение oi; всегда

Гл+cfl ГА

Абсолютная ошибка СР , ( --- г- t 5 L ( J L PiJ

± (Ьу для этих случаев может быть достаточно большой и ее верхняя граница находится в пределах tf Р; 2р; -1 в зависимости от величины . Q

Если (2k+l) Р; «р где k - кратность ошибки j) , то эта ошибка однозначно отображает of; в диапазоне Р; eS; р , т.е. монет быть исправлена выполнением oi; 1 ko; р; .

Таким образом, процедура вычисления совмещается с процедурой обнаружения и исправления ошибок.

Цифровой код, считьшаемый элементами 2, соответствующий остатку (Х 2о по наибольшему основанию р„, поступает на входы коммутатора 4, значение на выходе считьшающего элемента 2 младшего разряда определяет какая группа входов Считывающих эле- 25

ментов 2 запаздывающих или опережающих подключается к вькодной шине 9. Тем самым устраняется неоднозначность считывания.

Аналогичная операция происходит во всех оставшихся каналах. Значения

п И/РП - Wpi/pn поступают на входы сумматора 6.1, с выходов которого снимается значение оС; , которое по шине 13 поступает на вход блока 7 коррекции.

В блоке 7.1 коррекции на выходе шифратора 14 формируются коды О, , последовательность которых не имеет значения, вследствие чего на выходе сумматора 15 последовательно формируются значения Ы; ,

Р /Рп l fpn изменения кода на выходах суммато-

ра 15 на выходах блока 16 дифференцирования появится импульс длительностью, определяемой временем задержки элемента 22 задержки, который на время переходных процессов запретит выдачу результата сравнения блоком 18 сравнения. Когда вычисленное значение : Р; , т.е. - правильное значение, то на выходе блока 18 появляется разрешающий импульс, который запишет в регистр 17 правильное значение .

Быстродействие электронных блоков

30

35

40

45

50

55

скорость перемещения кодовой шкал позволяет формировать верный выхо ной результат в реальном масштабе времени.

Формула изобретен

1. Преобразователь перемещения код системы остаточных классов,со жащий п каналов, где п - число ос ваний в выбранной системе остаточ классов, кодовую шкалу, считывающи элементы, расположенные в каждом к нале относительно разрядных дорож кодовой шкапы по методу двойной щ ки, п коммутаторов по одному в ка нале, выходы считьшающих элементов каждом канале, за исключением счит вакщего элемента младшего разряда подключены к соответствующим входа коммутатора, управляющий вход кото рого соединен с выходами считывающ го элемента младшего разряда, п-1 сумматоров по одному в каждом кана ле, кроме первого, выходы коммутатора первого канала и считьшающего элемента младшего разряда первого нала являются выходом остатка по н большему основанию преобразователя отличающийся тем, что, с целью повышения точности, в него введены п-1 блоков коррекции, счет чик, сумматоры выполнены модульным по модулю наибольшего основания, а рисунок кодовой дорожки в i-M кана ле , где i ну

1,п-1, выполнен по за

.

где РП, р; - величины п-го и 1-го нований соответственно;

N - числовое значение отсчета, выходы коммутатора и считьгеающего элемента младшего разряда в каждом канале подключены к первой группе входов сумматора в канале, вторая группа входов которого соединена с выходом остатка по наибольшему осн ванию, а выходы подключены к перво группе входов соответствующих блок коррекции, выходы которых являоотся выходами остатка по соответствующему основанию преобразователя, а вторая группа входов соединена с в ходом счетчика, вход которого явля ется входом синхронизации преобразователя.

2. Преобразователь по п. 1, о т

устройства, значительно большее, чем личающийся тем, что блок

скорость перемещения кодовой шкалы I позволяет формировать верный выходной результат в реальном масштабе времени.

Формула изобретения

Q

о 5

0

5

0

5

5

1. Преобразователь перемещения в код системы остаточных классов,содержащий п каналов, где п - число оснований в выбранной системе остаточных классов, кодовую шкалу, считывающие элементы, расположенные в каждом канале относительно разрядных дорожек кодовой шкапы по методу двойной щетки, п коммутаторов по одному в канале, выходы считьшающих элементов в каждом канале, за исключением считы- вакщего элемента младшего разряда, подключены к соответствующим входам коммутатора, управляющий вход которого соединен с выходами считывающего элемента младшего разряда, п-1 сумматоров по одному в каждом канале, кроме первого, выходы коммутатора первого канала и считьшающего элемента младшего разряда первого канала являются выходом остатка по наибольшему основанию преобразователя, отличающийся тем, что, с целью повышения точности, в него введены п-1 блоков коррекции, счетчик, сумматоры выполнены модульными по модулю наибольшего основания, а рисунок кодовой дорожки в i-M канале , где i ну

1,п-1, выполнен по зако/ ШР /;.

где РП, р; - величины п-го и 1-го оснований соответственно;

N - числовое значение отсчета, выходы коммутатора и считьгеающего элемента младшего разряда в каждом канале подключены к первой группе входов сумматора в канале, вторая группа входов которого соединена с выходом остатка по наибольшему основанию, а выходы подключены к первой группе входов соответствующих блоков коррекции, выходы которых являоотся выходами остатка по соответствующему основанию преобразователя, а вторая группа входов соединена с выходом счетчика, вход которого является входом синхронизации преобразователя.

2. Преобразователь по п. 1, о ткоррекции содержит сумматор, шифратор, блок сравнения, блок дифференцирования, блок задания кода и регистр, первая группа входов сумматора является первой группой входов блока, вторая группа входов соединена- с выкодами шифратора, входы которого являются второй группой входов блока, выходы сумматора подключены к первой группе входав блока

594876

сравнения, входам регистра и входам блока дифференцирования, выход которого подключен к входу управления блока сравнения, вторая группа вхо- 5 дов которого соединена с блоком задания кода соответствующего основания , а выход подключен к управляющему входу регистра , выходы которого являются выхода- 10 ми блока.

20.1

го. т

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1984 |

|

SU1167733A1 |

| Преобразователь чисел из модулярного кода в позиционный код | 1987 |

|

SU1481898A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1989 |

|

SU1698991A1 |

| Устройство для обработки информации, представленной в системе остаточных классов | 1990 |

|

SU1743002A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1986 |

|

SU1368989A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1983 |

|

SU1181141A1 |

Изобретение относится к области вычислительной техники и может быть использовано, например, для ввода в ЭВ11, функционирующей в системе остаточных классов, информации, представленной перемещением. Целью изобретения является повьшение точности преобразователя. Для этого в преобразователь перемещения в код системы остаточных классов, содержащий кодовую шкалу, считывагацие элементы, коммутаторы, сумматоры, введены блоки коррекции и счетчик, а сумматоры выполнены модульными по модулю наибольшего основания. Поставленная цель достигается выполнением рисунка кодо- вой дорожки в i-M канале i 1,п-1 по правилу .p;/p, где /)„, . р; - величины п-го и i-ro оснований соответственно, N - числовое значение отсчета, обработкой кодов в сумматорах и коррекцией полученных результатов, исключающих ошибки преобразования. 1 з.п. ф-лы, 3 ил. i (Л С

Фчг.г

гдд ±

гч

Т

21 Фиг.3

Составитель Л. Сидоренко

Редактор Л. Гратилло Техред Л.Сердюкова, Корректор О. Луговая

--------- ..-,

Заказ 5139/58 Тираж 816 Подписног ВНИНПИ Государственного комитета СССР

по делам изобретений и.открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4.

| 0 |

|

SU312289A1 | |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ — КОД | 1971 |

|

SU429446A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1986-09-23—Публикация

1984-12-26—Подача