Изобретение относится к игмери- тельной и вычислительной технике и может быть использовано в системах обработки и передачи информации, а также в измерительной технике в качестве формирователя равномерной сетки частот. Известен преобразователь код-час тота, содержащий триггер, вертиль, генератор эталонной частоты, элементы И, элементы ИЛИ, сумматор, элемент задержки и датчик кода lj . Точность преобразования этого устройства обусловлена методической погрешностью дискретности. Методическую погрешность можно свести к миним5/му подбором частоты эталонного генератора, но исключить ее не возможно. Необходимость подбора час тоты эталонного генератора является недостатком, так как вынуждает имет большой набор кварцевых резонаторов (или других высокостабильных источников частоты), что осуществить невозможно. Наиболее близким- по технической сзтцности к предлагаемому является преобразователь код-частота которы содержит сумматор, первые п входов которого подключены к соответствуютцш выходам регистра, тактируемый вход которого соединен с шиной тактирования и такТируемьм входом выходного формирователя импульсов, выход которого соединен с выходной шиной, при этом информационные вход регистра подключены к соответствующим выходам мультиплексора, первые п входов которого подключены к соо ветствующим шинйм установки фазы, вторые п входы - к соответствующим выходам сумматора, а вход управления - к шине управления, причем выход переноса сумматора подключен к информационныму входу выходного формирователя импульсов 21 Выходная частота преобразователя равна f k -tbif 2 где fр - частота эталонного генератор а п - разрядность регистра и су матора F - входной код преобразователя, Из выражения (1) видно, что диск ретность установки частоты определя ется выражением При разработке преобразователей код-частота задаются требования к следующим параметрам частотный диапазон и дискретность частоты (частотный шаг). Эти параметры могут иметь различные значения в зависимости от поставленной задачи. Возможны также случаи, когда, используя выражения (t), соответствующее выходной частоте данного преобразователя кодчастота, невозможно точно подобрать значения f и п, чтобы удовлетворить заданной дискретности установки частоту и количеству установочных частот. Такое обстоятельство вызьгаает необходимость так подобрать значения fg и п, чтобы полученная дискретность установки частоты как можно меньше отличалась от заданной. Это приводит к определенной погрешности установки частоты и, в конечном счете, снижает точность преобразования. Из сказанного следует, что рассмотренный преобразователь код-частота имеет ограниченные функциональные возможности и вытекающую из этого методическую погрешность устан1 вки частоты. Цель изобретения - расширение функциональных возможностей и повьшение точности преобразования. Поставленная цель достигается тем, что в преобразователь код-настота, содержащий сумматор, первые п вхо-. дов которого подключены к соответствующим выходам регистра, тактируемый вход которого соединен с шиной тактирования и тактируемым входом выходного формирователя импульсов, выход которого соединен с выходной шиной, введены цифровой компаратор, комбинационный сумматор и преобразователь кода, входы которого подключены к соответствующим шинам кода режима и соответствующим первым входам цифрового компаратора, а выходы к соответствующим первым входам ком бинационного сумматора, вторые входы которого подключены к соответствующим шинам входного кода, а выходык соответствующим вторым п входам сумматора, выходы которого подключены к соответствующим разрядным входам регистра, выходы которого соединены с соответствующим вторыми входами цифрового компаратора, выход ко.31

торого соединен с информационным входом выходного формирователя импульсов и тактируемым входом преобразователя кода.

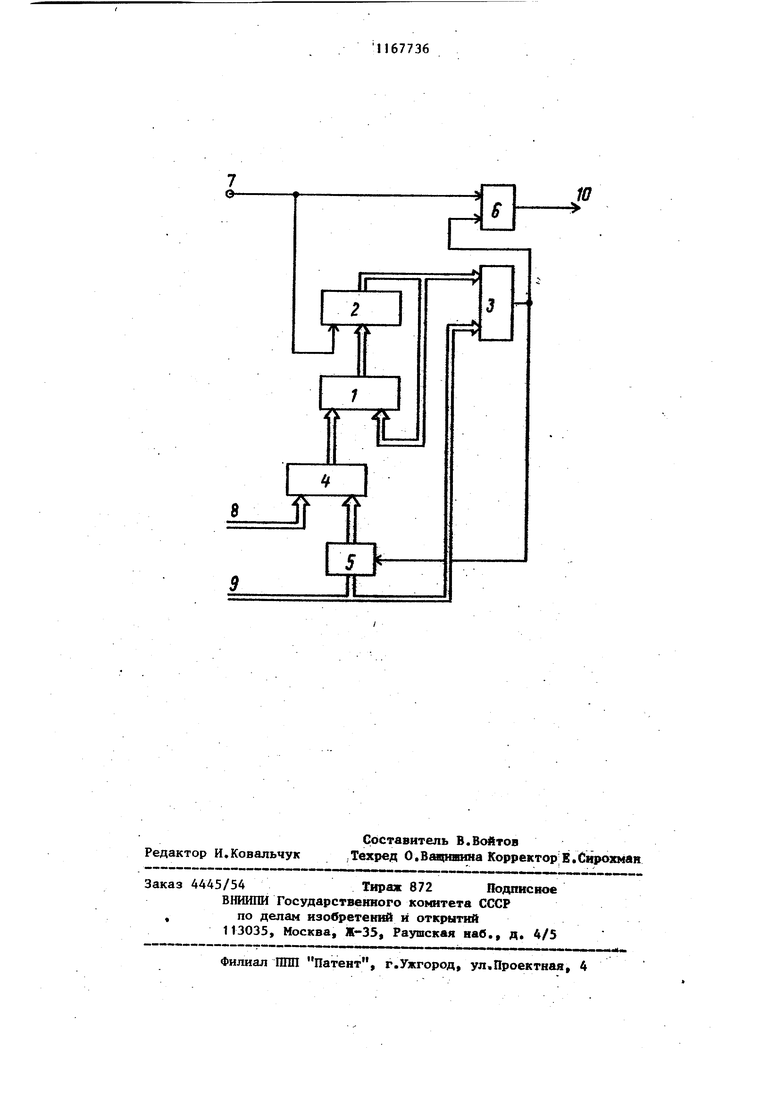

На чертеже дана структурная электрическая схема устройства.

Преобразователь содержит сумматор 1, регистр 2, цифровой компаратор 3, комбинационный сзт матор 4, преобразователь 5 кода, выходной формирователь 6 импульсов, шину 7 тактирования, шины 8 входного кода, шины 9 кода режима и выходную шину 10.

Первые п входов сумматора 1 подключены к выходам регистра 2, тактируемый вход, которого соединен с шиной 7 и тактируемым входом выходного формирователя 6, входы преобразователя кода 5 подключены к соответствующим шинам 9 и первым входам цифрового компаратора 3, а выходы к nepBbiM входам входного комбинационного сумматора 4, вторые входы которого подключены к соответствующим шинам 8, а выходы - к соответствующим вторым п входам сумматора J, выходы которого подключены к соответствующим разрядным входам регистра 2, выходы которого соединены с соответствующими вторыми входами цифрового компаратора 3, выход которог9 соединен с информационным входом выходного формирователя 6 и тактируемым входом преобразователя 5

кода.

Преобразователь работает следующим образом.

На шины В подается входной код f а на шины 9 - код режима М, на шине тактирования 7 действует импульсный сигнал с частотой f . Входнсй код N, поступает на вход комбинационного сумматора 4. На второй вход комбинационного сз мматора 4. поступает код с выхода преобразователя 5 кода, на вход (Которого поступает код режима, определяемый числом М. Код режима М преобразуется в дополнительный код М.дд преобразователем 5 кода. Вьщача кода Мдд„на вход комбииацион- ного cyiiiMaTopa 4 присходит только ,. в те моменты, когда на тактируемом входе преобразователя 5 кода появляется сигнал, поступающий с выхода цифрового компаратора 3. йри отсутствии сигнала на тактируемом входе преобразователь 5 кода фо{цшрует

677364

код, равный нулю. До появления сигнала на тактируемом входе преобразователя 5 кода на выходе комбинационного сумматора 4 повторяется входной 5 код N), который поступает на вход сумматора 1, на второй вход сумматора 1 поступает код, содержащийся в регистре 2. На информационные входы регистра 2 поступает код, веtoличина которого определяется как входного кода Ny и кода, содержащегося в регистре 2. При поступлении импульсного сигнала с шины 7 на тактируемый вход регистра 2 происходит

5 запись в регистр 2 кода с выхода сумматора 1. При этом на выходе сумматора 1 формируется новое число, значение которого по сравнению с предьщущим состоянием увеличилось на ве0личину N)(. С приходом следующего импульсного сигнала на тактируемый вход регистра 2 снова увеличится значение выходного кода сумматора t на величину N. С каждым новым так5том происходит также увеличение значения содержимого регистра 2. Вьйсод-« ной код регистра 2 поступает на вход цифрового компаратора 3, на второй вход которого подается код режима М. Цифровой компаратор 3 срав0нивает значение содержимого регистра 2 с величиной кода , М. Если величина выходного кода регистра 2 больше или равна, величине кода режима М, на выходе цифрового компарато5ра 3 появляется сигнал, который поступает на информационный вход выходного формирователя 6 и тактируемый вход преобразователя 5 кода. На выходкой шине 10 с выхода формирова0теля 6 появляется сигнал при наличии на его входах одновременно тактрфзтощего сигнала и сигнала с выхода цифрового компаратора 3. Таким образом, при поступлении импульсов на тактиру5емый вход регистра 2 происходит увеличение содержимого регистра 2. При достижении состояния, при котором выполняется неравенство

L М (3)

0 где L - выходной код регистра 2, а М - код режима, на выходе цифрового компаратора 3 появляется сигнал, который .поступает на тактируемый вход преобразователя 5 кода. На вьпсо5де преобразователя 5 кода формируется дополнительный код М. На выходе комбинационного суммат.ора 4 формируется код, величина которого определяется как разность входного кода NJ и кода режима М. За время очередного такта содержимое регист ра 2 уменьшится на величину М. Если в последующие такты условие (3) не вьтолняется, то выход преобразователя кода блокируется и на выходе комбинационного сумматора повторяется входной код Ы и накопление содержимого регистра повторяется вышеописанным способом Из описания функциональной схем вытекает, что накопление содержимо го регистра 2, формирование сигнал сравнения цифровым компаратором 3 и формирование выходного сигнала будет происходить циклически, т.е. этот процесс является периодически Период появления выходных импульсо можно определить по формуле r--l M-enl;erU- -)tent;er iK-i)w где М - код режима; NK - входной код; К - порядковый номер вьосодног импульса, по отношению к которому измеряется пери од; f - частота эталонного генератора;entier(z) - функция вьщеления целой части числа Z , Анализ выражения (4) показывает что в общем случае период появления выходных импульсрв является неравномерным, но эта неравномерность циклически повторяется, получается периодическая последова тельность пачек импульсов, распред ление импульсов в пачке зависит от величин М и Nj(, В частных случаях последовательность импульсов может быть равномерной. Период повторения пачек импульсов будет равен: т . fS п f НОД(М,М,) где М - код режима; НОД(М,Ы) - наибольший общий делитель чисел М f - частота эталонного генератора. Усредненная частота за период Т для выходных импульсов преобразователя равна f --- N Bbix М где N - входной код преобразователя, М - код режима, fo - частота эталонного генератора. Из выражения (6) видно, что на выходе преобразователя имеем сигнал с частотой, прямопропорциональной входному коду. . Возможность управления предлагаемым преобразователем при помощи кода режима М дает преимущества перед прототипом,так как благодаря этому расширяются функциональные возможности при выборе частотного шага формируемой сетки частот и тем самым повьшается точность установки частоты. Для полного исключения неравномерности выходных импульсов достаточно на выходе преобразователя поставить делитель, частоты с коэффициентом деления (М-1)(-факториал). Это исключает для любьт соотношений М и N появление неравномерностеи в выходных импульсах преобразователя кодчастота. Тогда выходная частота равнаf N m (М-1) Рьа Мт где m - коэффициент деления счётчика на выходе. Для работы преобразователя кодчастота необходимо обеспечить 2 М, 2 М (8) где п - разрядность сумматора 1, регистра 2, входного комбинационного сумматора А, преобразователя 5 кода 1 - разрядность входного кода. Технико-экономические преимущества изобретения заключатся в расширении функциональных возможностей за счет осуществления управления дискретностью преобразования, что повышает точность установки частоты и расширяет область применения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь код-частота | 1987 |

|

SU1474849A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Преобразователь код-частота | 1984 |

|

SU1206959A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОД - ЧАСТОТА | 1995 |

|

RU2092973C1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Параллельный аналого-цифровой преобразователь | 1986 |

|

SU1332533A1 |

| СИГМА-ДЕЛЬТА-АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1998 |

|

RU2145149C1 |

| Преобразователь код-частота | 1981 |

|

SU966890A1 |

ПРЕОБРАЗОВАТЕЛЬ КОД-ЧАСТОТА, содержащий сумматор, первые п входов которого подключены к соответствую щим выходам регистра, тактируемый вход которого соединен с шиной тактирования и тактируемым входом вы ходного формирователя импульсов, выход которого соединен с выходной шиной, отлича-ющийся тем, что, с целью расширения функциональных возможностей и повышения точности преобразования, в негр введены цифровой компаратор, комбинационный сумматор и преобразователь кода, входы которого подключены к соответствующим шинам кода режима и соответствуювщм первьм входам цифрового компаратора, а выходы к соответствующим первым входам комбинационного сумматора, вторые входы которого подключены к соответствующим шинам входного кода, а выходы - к соответствующим вторым п входам сумматора, выходы которого подключены к соответствующим разрядным (Л входам регистра, выходы которого соединены с соответствующими вторыс ми входами цифрового компаратора, выход которого соединен с информационным входом выходного формирователя импульсов и тактируемым входом преобразователя кода. 535 Ч Ч СО О)

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОД-ЧАСТОТА | 0 |

|

SU345609A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь код-частота | 1981 |

|

SU966890A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-07-15—Публикация

1984-01-09—Подача