тель 3 напряжения, группу 1 компараторов с памятью, введены пять мультиплексоров 5-9, два аналоговых сумматора 10 и 11, буферный усилитель

1

Изобретение относится к измерительной технике и предназначено для преобразования параллельным методом широкополосных аналоговых сигналов с методической погрешностью k-разряд- ного устройства при одном входном сигнале и (k-1)-разрядного устройств при двух входных сигналах, измеряемых одновременно,

Целью изобретения является расширение области применения за счет возможности одновременного преобразования большего числа сигналовi

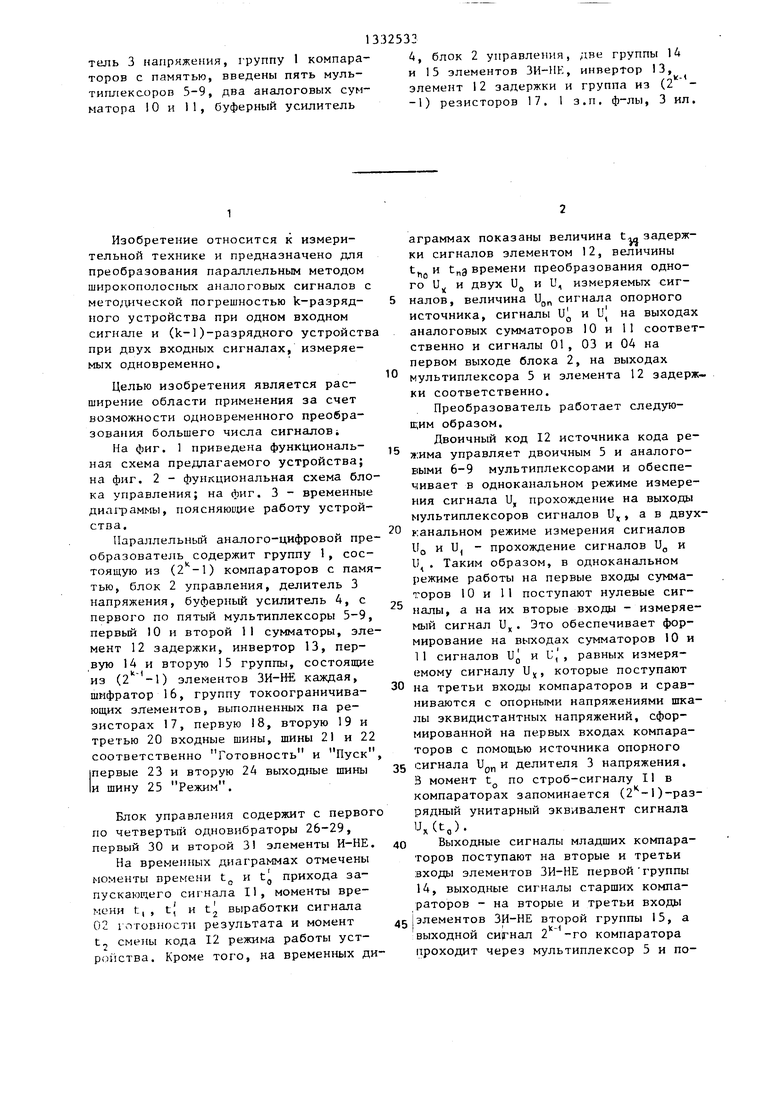

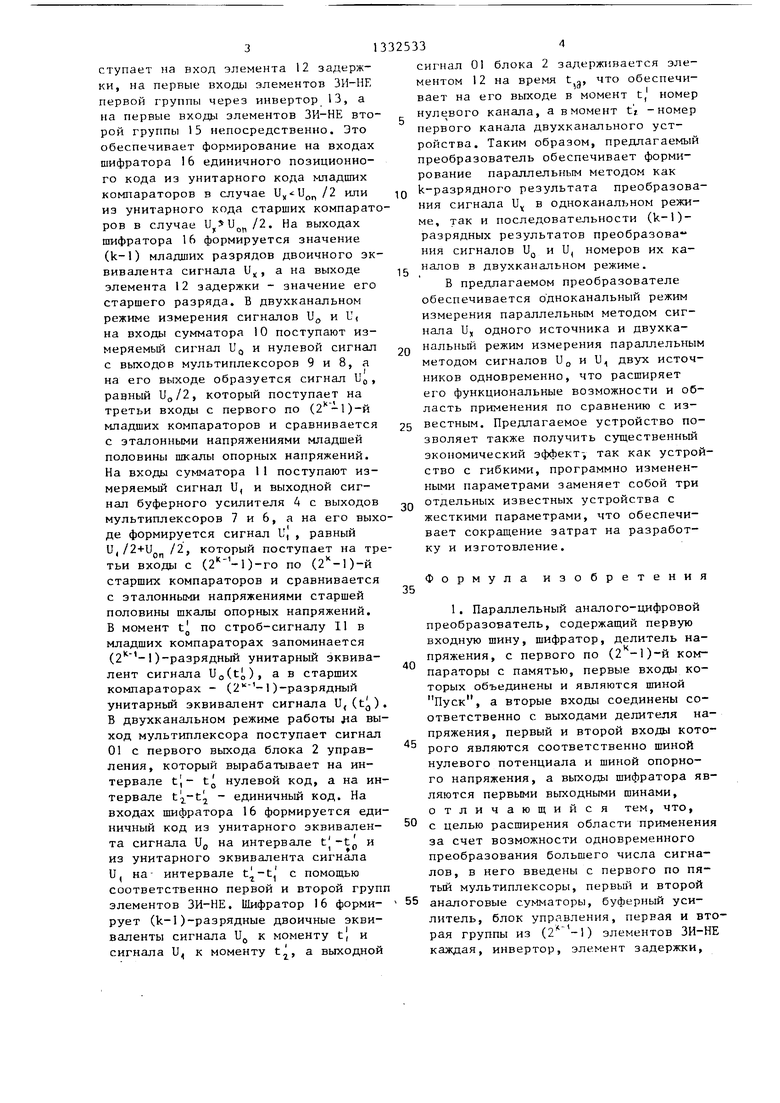

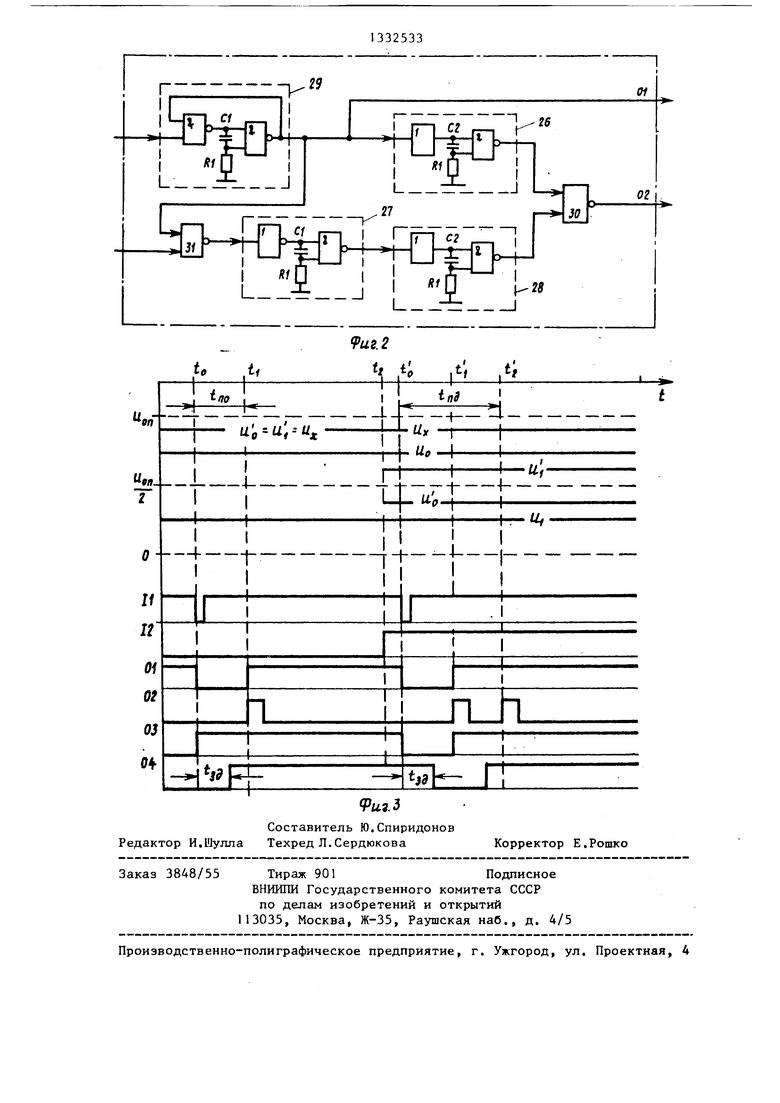

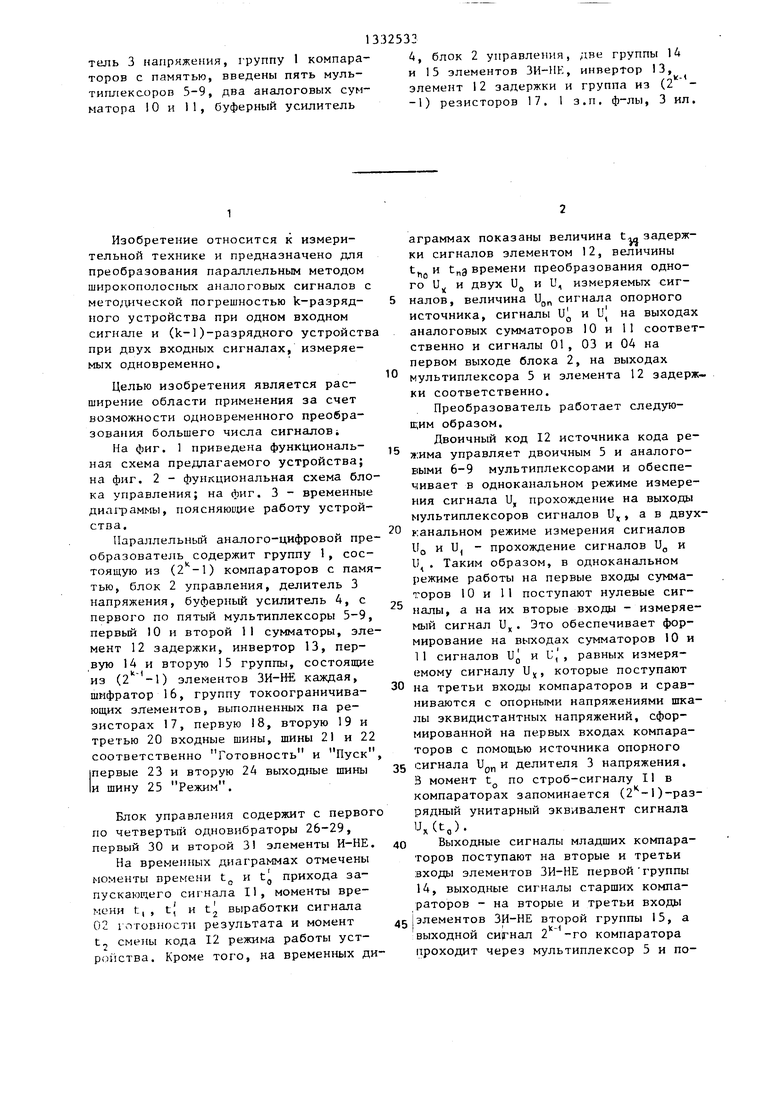

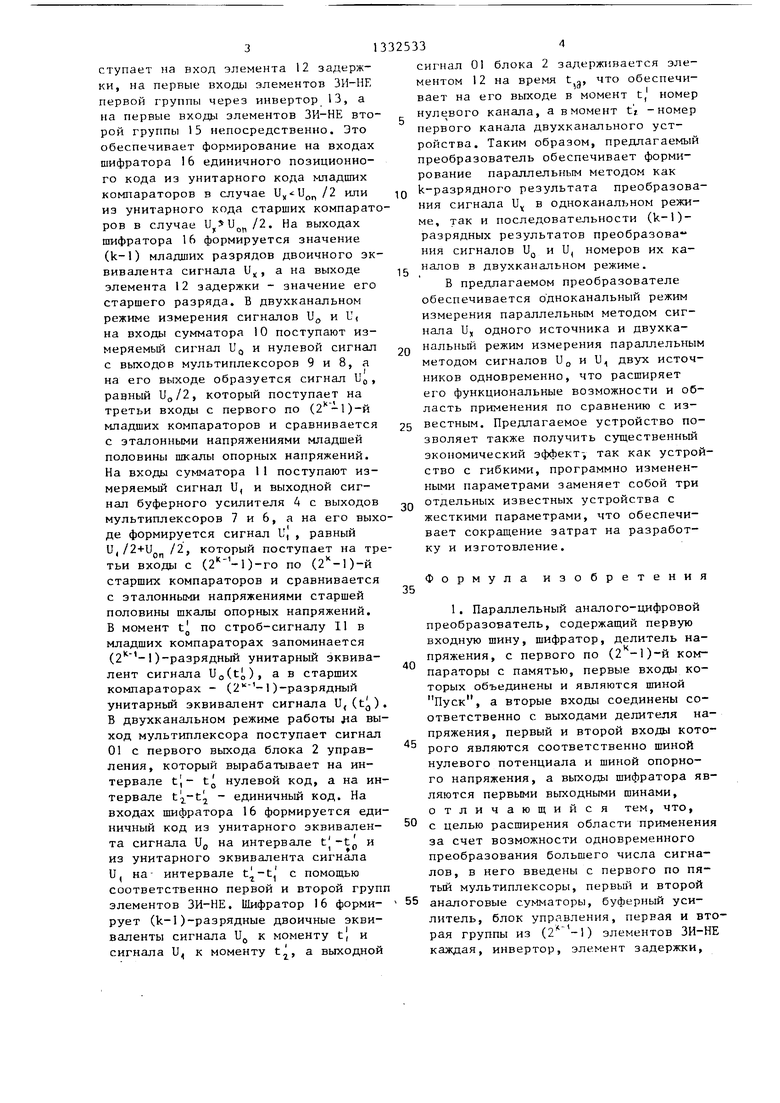

На фиг, 1 приведена функЦиональ- ная схема предлагаемого устройства; на фиг, 2 - функциональная схема блока управления; на фиг. 3 - временные диа1Т5аммы, поясняюии1е работу устройства.

Параллельный аналого-цифровой преобразователь содержит группу 1, состоящую из (2-1) компараторов с памятью, блок 2 управления, делитель 3 напряжения, буферный усилитель А, с первого по пятый мультиплексоры 5-9, первый 10 и второй 11 сумматоры, элемент 12 задержки, инвертор 13, первую 14 и вторую 15 группы, состоящие из (2 -1) элементов ЗИ-НЕ каждая, шифратор 16, группу токоограничива- ющих элементов, выполненных па резисторах 17, первую 18, вторую 19 и третью 20 входные шины, шины 21 и 22 соответственно Готовность и Пуск первые 23 и вторую 24 выход1Ш1е шины и шину 25 Режим.

Блок управления содержит с первог по четверть одновибраторы 26-29, первый 30 и второй 3 элементы И-НЕ.

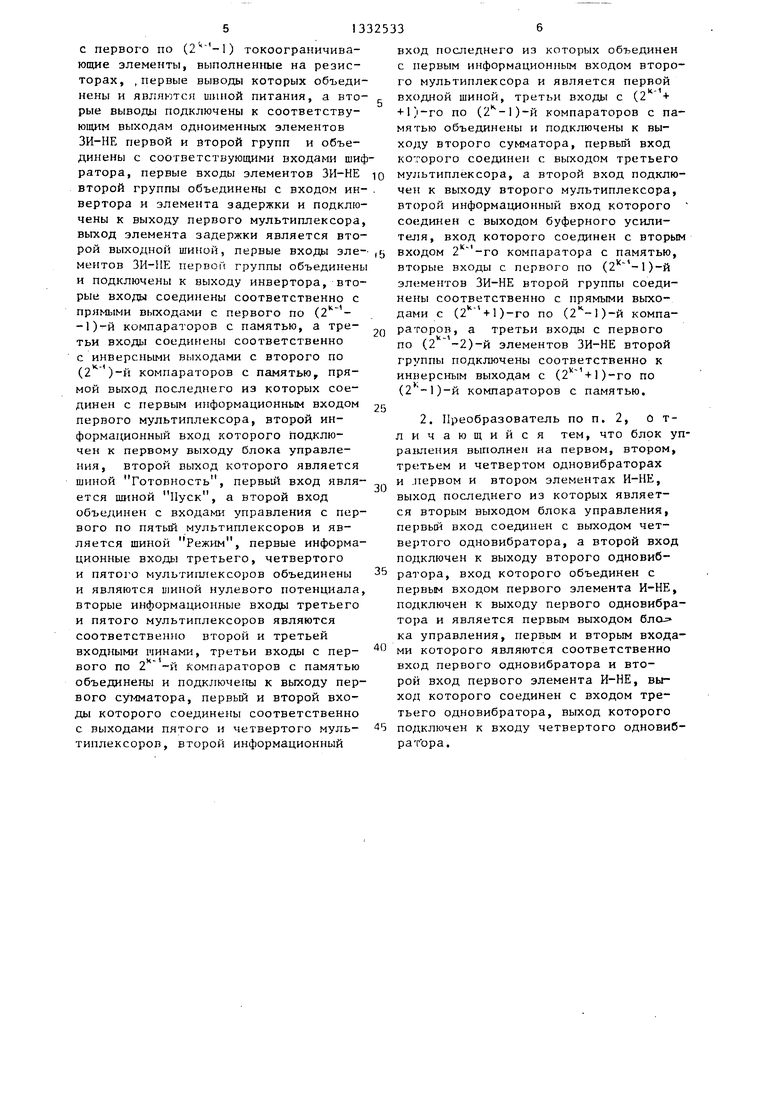

На временных диаграммах отмечены моменты времени t и t прихода запускающего сиг нала II, моменты времени t,, tj и tj выработки сигнала 02 готовности результата и момент tj смены кода 12 режима работы устройства. Кроме того, на временных ди4, блок 2 управления, две группы 14 и 15 элементов ЗИ-НЕ, инвертор 13, элемент 12 задержки и группа из (2 - -1) резисторов 17, 1 з.п. ф-лы, 3 ил.

0

g

c 5

0

5

аграммах показаны величина ty, задержки сигналов элементом 12, величины t и времени преобразования одного и и двух Ug и и, измеряемых сигналов, величина U сигнала опорного источника, сигналы U и u| на выходах аналоговых сумматоров 10 и 11 соответственно и сигналы 01, 03 и 04 на первом выходе блока 2, на выходах мультиплексора 5 и элемента 12 задержки соответственно.

Преобразователь работает следую- п;;им образом.

Двоичный код 12 источника кода режима управляет двоичным 5 и аналоговыми 6-9 мультиплексорами и обеспечивает в одноканальном режиме измерения сигнала и„ прохождение на выходы мультиплексоров сигналов U, а в двух- канальном режиме измерения сигналов UQ и и, - прохождение сигналов U и и . Таким образом, в одноканальном режиме работы на первые входы сумматоров 10 и 11 поступают нулевые сигналы, а на их вторые входь - измеряемый сигнал и. Это обеспечивает формирование на выходах сумматоров 10 и 11 сигналов Ug и и,, равных измеря- «;мому сигналу U,;, которые поступают на третьи входы компараторов и сравниваются с опорными напряжениями шкалы эквидистантных напряжений, сформированной на первых входах компараторов с помощью источника опорного сигнала U и делителя 3 напряжения. В момент t по строб-сигналу II в компараторах запоминается ()-раз- рядный унитарный эквивалент сигналн

и. (to).

Выходные сигналы младших компараторов поступают на вторые и третьи входы элементов ЗИ-НЕ первой группы 14, выходные сигналы старших компараторов - на вторые и третьи входы элементов ЗИ-НЕ второй группы 15, а выходной сигнал -го компаратора проходит через мультиплексор 5 и поступает на вход элемента 12 задержки, на первые входы элементов ЗИ-НЕ первой группы через инвертор 13, а на первые входь элементов ЗИ-НЕ второй группы 15 непосредственно. Это обеспечивает формирование на входах шифратора 16 единичного позиционного кода из унитарного кода младших компараторов в случае , /2 или из унитарного кода старших компаратров в случае . На выходах шифратора 16 формируется значение (k-1) младших разрядов двоичного эквивалента сигнала и,, а на выходе элемента 12 задержки - значение его старшего разряда. В двухканальном режиме измерения сигналов U и U, на входы сумматора 10 поступают измеряемый сигнал UQ и нулевой сигнал с выходов мультиплексоров 9 и 8, а на его выходе образуется сигнал U,, равный Uo/2, который поступает на третьи входы с первого по (2-1)-й младших компараторов и сравнивается с эталонными напряжениями младшей половины шкалы опорных напряжений. На входы сумматора 11 поступают измеряемый сигнал и, и выходной сигнал буферного усилителя 4 с выходов мультиплексоров 7 и 6, а на его выхде формируется сигнал Uj , равный и,/2+Up /2, который поступает на тртьи входы с ()-го по (2-1)-й старших компараторов и сравнивается с эталонными напряжениями старшей половины шкалы опорных напряжений. В момент t по строб-сигналу II в младших компараторах запоминается ()-разрядный унитарный эквивалент сигнала UoCtj,), а в старших компараторах - ()-разрядный унитарный эквивалент сигнала U,(t) В двухканапьном режиме работы да выход мультиплексора поступает сигнал 01 с первого выхода блока 2 управления, который вырабатывает на интервале t нулевой код, а на интервале - единичный код. На входах шифратора 16 формируется единичный код из унитарного эквивалента сигнала UQ на интервале t - из унитарного эквивалента сигнала

и

и. на- интервале

Ч-Ч

с помощью

соответственно первой и второй групп элементов ЗИ-НЕ. Шифратор 16 формирует (k-1)-разрядные двоичные эквиваленты сигнала U к моменту t , и сигнала U к моменту t, а выходной

сигнал 01 блока 2 задерживается элементом 12 на время вает на его выходе в момент

что обеспечи- номер

5

0

5

0

ния сигнала U, ме, так и

нулевого канала, а в момент tt -номер первого канала двухканального устройства. Таким образом, предлагаемый преобразователь обеспечивает формирование параллельным методом как k-разрядного результата преобразова в одноканальном режи- последовательности (k-1)- разрядных результатов преобразования сигналов UQ и и, номеров их каналов в двухканальном режиме.

В предлагаемом преобразователе обеспечивается о дноканальный режим измерения параллельным методом сигнала и, одного источника и двухка- нальный режим измерения параллельным методом сигналов Uj, и U, двух источников одновременно, что расширяет его функциональные возможности и область применения по сравнению с известным. Предлагаемое устройство позволяет также получить существенный экономический эффект-, так как устройство с гибкими, программно измененными параметрами заменяет собой три отдельных известных устройства с жесткими параметрами, что обеспечивает сокращение затрат на разработку и изготовление.

40

45

50

55

35

Формула изобретения

1. Параллельный аналого-цифровой преобразователь, содержащий первую входную шину, шифратор, делитель напряжения, с первого по (2 -1)-й компараторы с памятью, первые входы которых объединены и являются шиной Пуск, а вторые входы соединены соответственно с выходами делителя напряжения, первый и второй входы которого являются соответственно шиной нулевого потенциала и шиной опорного напряжения, а выходы шифратора являются первыми выходными шинами, отличающийся тем, что, с целью расширения области применения за счет возможности одновременного преобразования большего числа сигналов, в него введены с первого по пятый мультиплексоры, первый и второй аналоговые сумматоры, буферный усилитель, блок управления, первая и вторая группы из (2 -1) элементов ЗИ-НЕ каждая, инвертор, элемент задержки.

с первого по () токоограничива- ЮЕЦие элементы, выполненные на резисторах, .первые выводы которых объединены и являются шиной питания, а вторые выводы подключены к соответствующим выходам одноименных элементов ЗИ-НЕ первой и второй групп и объединены с соответствующими входами шифратора, первые входы элементов ЗИ-НЕ второй группы объединены с входом ин- вертора и элемента задержки и подключены к выходу первого мультиплексора, вьгкод элемента задержки является второй выходной шиной, первые входы элементов ЗИ-НЕ первой группы объединены и подключены к выходу инвертора, вторые входы соединены соответственно с прямыми выхода.ми с первого по ( -1)-й компараторов с памятью, а третьи входы соединены соответственно с инверсными выходами с второго по ()-й компараторов с памятью, прямой выход последнего из которых соединен с первым информационным входом первого мультиплексора, второй информационный вход которого подключен к первому выходу блока управле

ния.

второй выход которого является

шиной Готовность, первый вход является шиной Пуск, а второй вход объединен с входами управления с первого по пятьш мультиплексоров и является шиной Режим, первые информационные входы третьего, четвертого и пятого мультиплексоров объединены и являются шиной нулевого потенциала вторые информационные входы третьего и пятого мультиплексоров являются соответственно второй и третьей входными шинами, третьи входы с пер- вого по 2 -и компараторов с памятью объединены и подключены к выходу первого сумматора, первый и второй входы которого соединены соответственно с выходами пятого и четвертого муль- типлексороп, второй информационный

вход последнего из которых объединен с первым информационным входом второго мультиплексора и является первой входной шиной, третьи входы с (2 + 1)-го по ()-й компараторов с памятью объединены и подключены к выходу второго сумматора, первый вход которого соединен с выходом третьего мультиплексора, а второй вход подключен к выходу второго мультиплексора, второй информационный вход которого соединен с выходом буферного усилителя, вход которого соединен с вторым входом 2 -го компаратора с памятью, вторые входы с первого по (2-1)-й элементов ЗИ-НЕ второй группы соединены соответственно с прямыми выходами с ( + 1)-го по ( )-й компараторов, а третьи входы с первого по (2 -2)-й элементов ЗИ-НЕ второй группы подключены соответственно к инверсным выходам с (2 + 1)-го по (2-1)-й компараторов с памятью.

2. Преобразователь по п. 2, отличающийся тем, что блок уп- раиления выполнен на первом, втором, третьем и четвертом одновибраторах и .первом и втором элементах И-НЕ, выход последнего из которых является вторым выходом блока управления, первый вход соединен с выходом четвертого одновибратора, а второй вход подключен к выходу второго одновибратора, вход которого объединен с первым входом первого элемента И-НЕ, подключен к выходу первого одновибратора и является первым выходом бло- ка управления, первым и вторым входами которого являются соответственно вход первого одновибратора и второй вход первого элемента И-НЕ, выход которого соединен с входом третьего одновибратора, выход которого подключен к входу четвертого одновибратора.

Un

Jf

Г

/27

b-И

С1

.

±Г

RlQ

I-ЬI

Редактор И.Шулла

Физ.З

Составитель Ю.Спиридонов Техред Л.Сердюкова

Заказ 3848/55 Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

- 30

г

сг

У и 25

1- --±

Корректор Е.Рошко

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1464289A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Устройство для аналого-цифрового преобразования импульсных сигналов | 1987 |

|

SU1564725A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Способ следящего аналого-цифрового преобразования и устройство для его осуществления | 1983 |

|

SU1229954A1 |

Изобретение относится к измерительной технике и предназначено для преобразования широкополосных аналоговых сигналов с разрешающей способностью k-разрядного устройства при одном и (k-1)разрядного устройства при двух входных сигналах. Целью изобретения является расширение области применения за счет возможности одновременного преобразования большего числа сигналов. В преобразователь, содержаЕций шифратор 16, дели г -/ 152--/ 7г«- -/ Чп. с (Л I-J I -i /5, V- -; W f- -, 2 1 /6 0 X) ю У1 : :о

| Преобразование информации в аналого-цифровых вычислительных устройствах и системах./Под ред | |||

| Г.М.Петрова | |||

| М.: Маииностроение, 1973, с | |||

| Приспособление для воспроизведения изображения на светочувствительной фильме при посредстве промежуточного клише в способе фотоэлектрической передачи изображений на расстояние | 1920 |

|

SU172A1 |

| Балакай В.Г | |||

| и др | |||

| Интегральные схемы АЦП и ЦАП | |||

| - М.: Энергия, с | |||

| Ветряный много клапанный двигатель | 1921 |

|

SU220A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-23—Публикация

1986-03-25—Подача