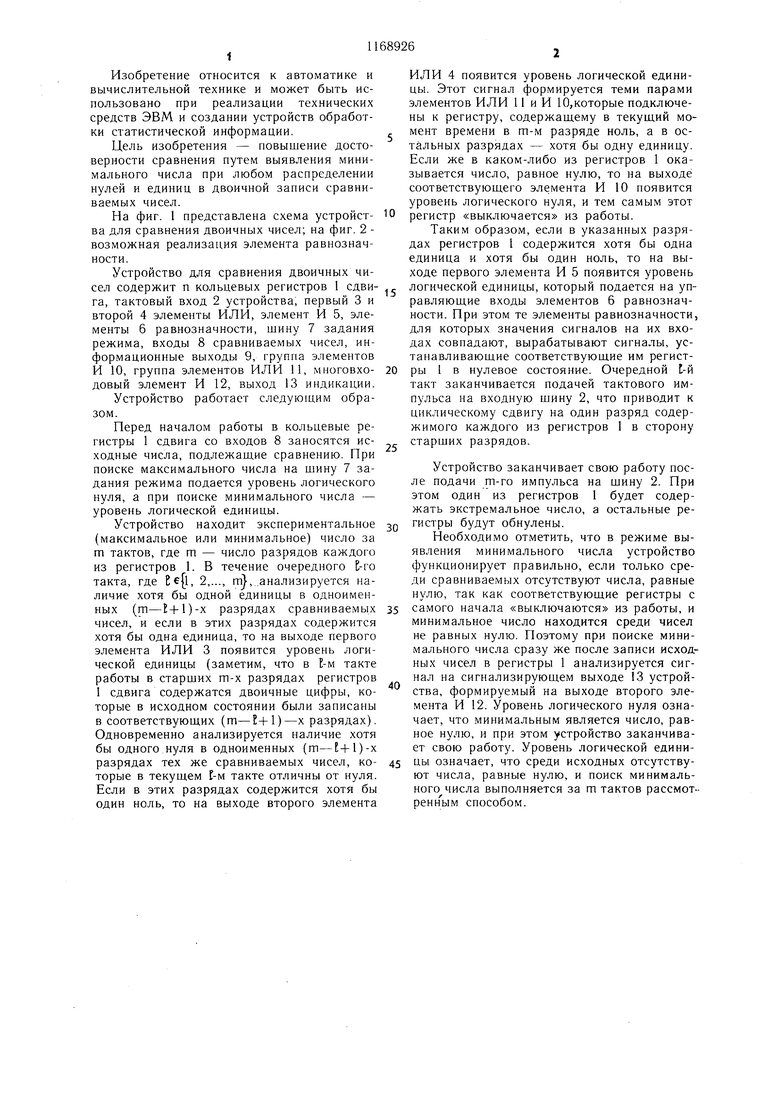

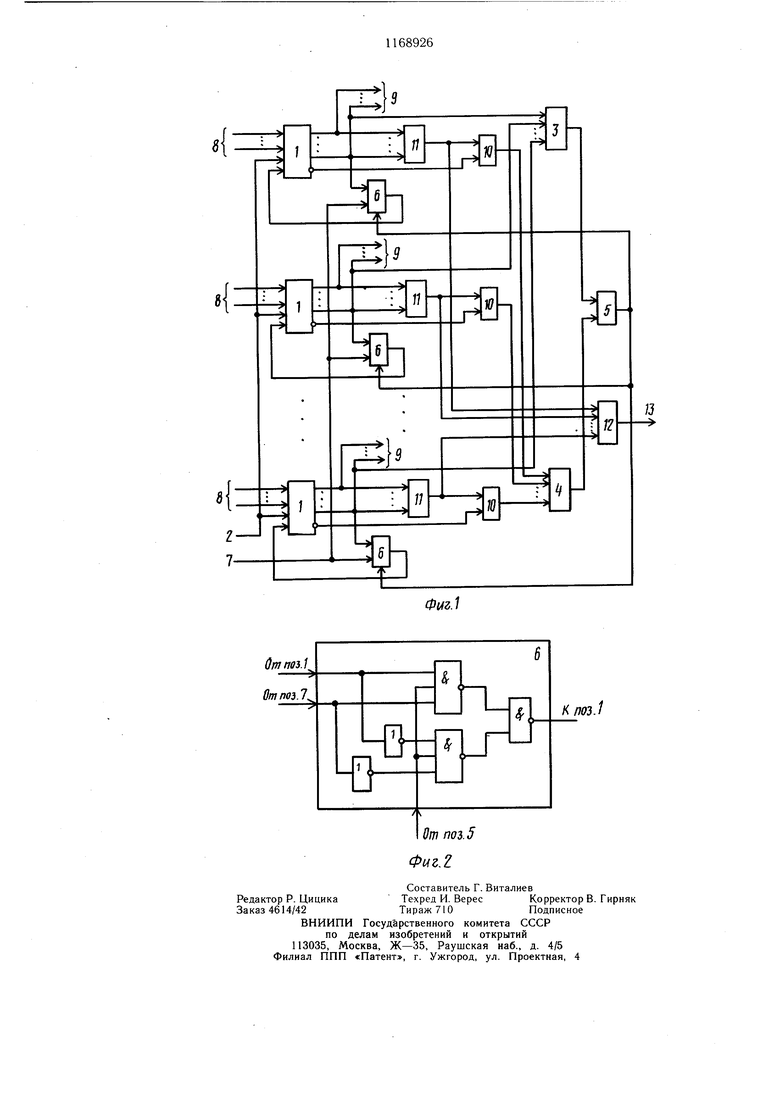

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств ЭВМ и создании устройств обработки статистической информации. Цель изобретения - повышение достоверности сравнения путем выявления минимального числа при любом распределении нулей и единиц в двоичной записи сравниваемых чисел. На фиг. 1 представлена схема устройства для сравнения двоичных чисел; на фиг. 2 возможная реализация элемента равнозначности. Устройство для сравнения двоичных чисел содержит п кольцевых регистров 1 сдвига, тактовый вход 2 устройства, первый 3 и второй 4 элементы ИЛИ, элемент И 5, элементы 6 равнозначности, шину 7 задания режима, входы 8 сравниваемых чисел, информационные выходы 9, группа элементов И 10, группа элементов ИЛИ 11, многовходовый элемент И 12, выход 13 индикации. Устройство работает следующим образом. Перед началом работы в кольцевые регистры 1 сдвига со входов 8 заносятся исходные числа, подлежащие сравнению. При поиске максимального числа на шину 7 задания режима подается уровень логического нуля, а при поиске минимального числа - уровень логической единицы Устройство находит экспериментальное (максимальное или минимальное) число за m тактов, где m - число разрядов каждого из регистров 1. В течение очередного Е-го такта, где , 2,..., пт},.,анализируется наличие хотя бы одной единицы в одноименных (т-В+1)-х разрядах сравниваемых чисел, и если в этих разрядах содержится хотя бы одна единица, то на выходе первого элемента ИЛИ 3 появится уровень логической единицы (заметим, что в Е-м такте работы в старших т-х разрядах регистров 1 сдвига содержатся двоичные цифры, которые в исходном состоянии были записаны в соответствующих (т-Е+1)-х разрядах). Одновременно анализируется наличие хотя бы одного нуля в одноименных (т-Е+1)-х разрядах тех же сравниваемых чисел, которые в текущем f-м такте отличны от нуля. Если в этих разрядах содержится хотя бы один ноль, то на выходе второго элемента ИЛИ 4 появится уровень логической единицы. Этот сигнал формируется теми парами элементов ИЛИ 11 и И 10,которые подключены к регистру, содержащему в текущий момент времени в т-м разряде ноль, а в остальных разрядах - хотя бы одну единицу. Если же в каком-либо из регистров 1 оказывается число, равное нулю, то на выходе соответствующего элемента И 10 появится уровень логического нуля, и тем самым этот регистр «выключается из работы. Таким образом, если в указанных разрядах регистров 1 содержится хотя бы одна единица и хотя бы один ноль, то на выходе первого элемента И 5 появится уровень логической единицы, который подается на управляющие входы элементов 6 равнозначности. При этом те элементы равнозначности, для которых значения сигналов на их входах совпадают, вырабатывают сигналы, устанавливающие соответствующие им регистры 1 в нулевое состояние. Очередной t-й такт заканчивается подачей тактового импульса на входную щину 2, что приводит к циклическому сдвигу на один разряд содержимого каждого из регистров 1 в сторону старших разрядов. Устройство заканчивает свою работу после подачи 1Т1-ГО импульса на щину 2. При этом один из регистров 1 будет содержать экстремальное число, а остальные ре™стры будут обнулены. Необходимо отметить, что в режиме выявления минимального числа устройство функционирует правильно, если только среди сравниваемых отсутствуют числа, равные нулю, так как соответствующие регистры с самого начала «выключаются из работы, и минимальное число находится среди чисел не равных нулю. Поэтому при поиске минимального числа сразу же после записи исходных чисел в регистры 1 анализируется сигнал на сигнализирующем выходе 13 устройства, формируемый на выходе второго элемента И 12. Уровень логического нуля означает, что минимальным является число, равное нулю, и при этом устройство заканчивает свою работу. Уровень логической единицы означает, что среди исходных отсутствуют числа, равные нулю, и поиск минимального числа выполняется за m тактов рассмотренр/ым способом.

г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двоичных чисел | 1984 |

|

SU1201855A1 |

| Устройство для сравнения двоичных чисел | 1986 |

|

SU1410020A1 |

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

| Устройство для сравнительного анализа п чисел | 1978 |

|

SU736090A1 |

| Устройство для выделения максимального числа | 1982 |

|

SU1043634A1 |

| Устройство для сравнения чисел | 1986 |

|

SU1439574A1 |

| Устройство для сравнения чисел | 1978 |

|

SU729586A1 |

| Устройство для сравнения -разрядных двоичных чисел | 1977 |

|

SU746502A1 |

| Устройство для сравнения чисел | 1986 |

|

SU1376079A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ, содержащее п кольцевых регистров сдвига, где п-число сравниваемых чисел, п элементов равнозначности, первый и второй элементы ИЛИ и элемент И, причем входы сравниваемых чисел устройства подключены к установочным входам соответствующих кольцевых регистров сдвига, прямые иыходы старших разрядов которых соедине.41,1 с первыми информационными входами соответствующих элементов равнозначности и входами первого элемента ИЛИ, выход которого подключен к первому входу элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, а выход подключен к входам разре1пения сравнения всех элементов равнозначности, вторые информационные входы которых подключены к шине -.а 1ания режима устройства, выходы элементов равнозначности соединены с входами установки в «О соответствующих кольцевы.х регистров сдвига, выходы которых являются инфор.мационными выходами устройства, входы управления сдвигом всех кольцевых регистров сдвига подключены к тактовому входу устройства, отличающееся тем, что, с целью повышения достоверности сравнения путем выявления минимального числа при любом распределении нулей и единиц в двоичной записи сравниваемых чисел, в него введены группа п элементов ИЛИ. группа п элементов И и многовходовый элемент И, причем выходы разрядов кольцевых регистров сдвига подключены к входам соответствующих элементов ИЛИ группы, выходы кото о рых соединены с соответствующими входами многовходового элемента И и первыми (Л входами соответствующих элементов И группы, вторые входы которых соединены с инверсными выходами старших разрядов соответствующих кольцевых регистров сдвига, а выходы подключены к входам второго элемента ИЛИ, выход многовходового элемента И является выходом индикации устройства. а 00 ;о ГчЭ 0

7-

z

;j

/

Ж

ВД

| Устройство для сравнения п двоичных чисел | 1973 |

|

SU478303A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1984-02-16—Подача