Изобретение относится к вычислительной технике, а именно к устройствам для программного управления, может быть использовано при разработке и отладке программ для ЭВМ и является усовершенствованием изобретения по авт. св. № 962945.

Цель изобретения - расширение класса решаемых задач путем обеспечения прерывания отлаживаемой программы при чтении информации.

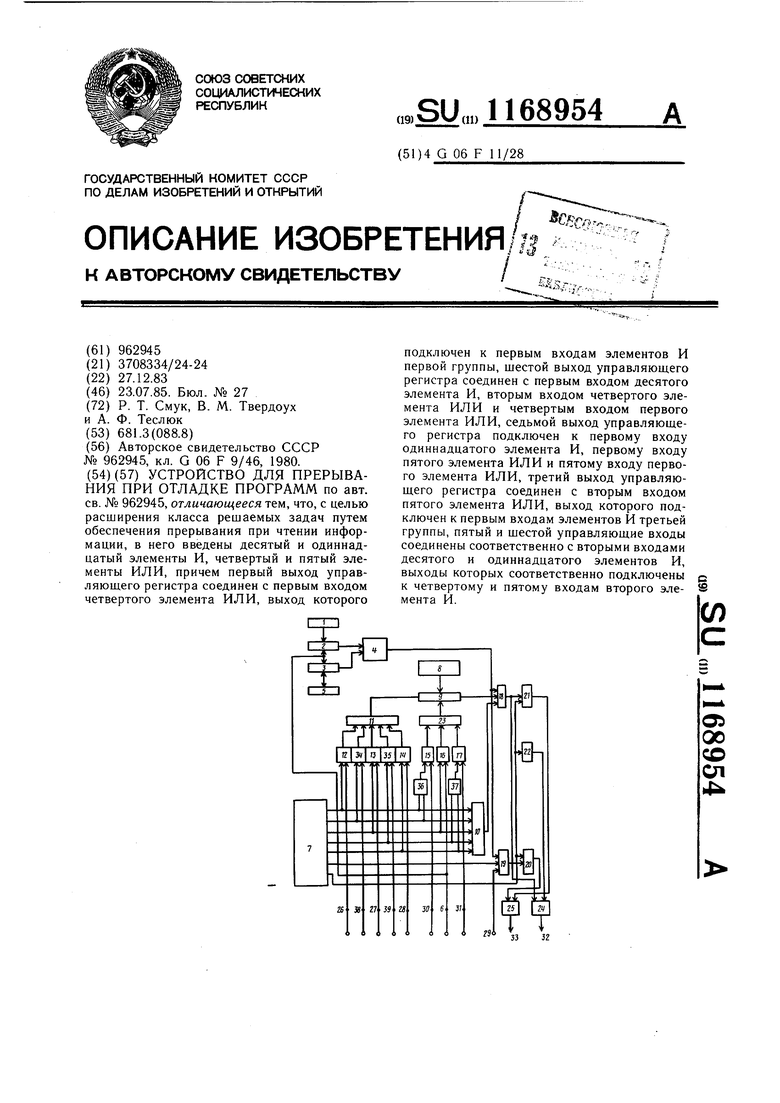

На чертеже приведена схема устройства для прерывания при отладке программ.

Устройство содержит первый регистр 1, первый 2 и второй 3 узлы сравнения, первый элемент И 4, второй регистр 5, первый информационный вход 6, управляюш,ий регистр 7, третий регистр 8, третий узел 9 сравнения, первый 10, второй 11 элементы ИЛИ, второй 12, третий 13 и четвертый 14 элементы И, первую 15, вторую 16 и третью 17 группу элементов И, пятый 18, шестой 19, седьмой 20 и восьмой 21 элементы И, элемент НЕ 22, группу 23 элементов ИЛИ, девятый элемент И 24, третий элемент ИЛИ 25, первый 26, второй 27, третий 28 и четвертый 29 управляюшие входы, второй 30 и третий 31 информационные входы, первый 32 и второй 33 управляюшие выходы, десятый 34 и одиннадцатый 35 элементы И, четвертый 36 и пятый 37 элементы ИЛИ, пятый 38 и шестой 39 управляюшие входы.

Выходы первого 1 и второго 5 регистров соединены соответственно с первыми входами первого 2 и второго 3 узлов сравнения, выходы которых соединены соответственно с первым и вторым входами первого элемента И 4. Первый выход управляющего регистра 7 соединен с первыми входами второго элемента И 12, первого 10 и четвертого 36 элементов ИЛИ. Шестой выход управляющего регистра 7 соединен с первым входом десятого элемента И 34, вторым входом четвертого элемента ИЛИ 36 и четвертым входом первого элемента ИЛИ 10, второй вход которого совместно с первым входом третьего элемента И 13 и первыми входами второй группы элементов И 16 подключен к второму выходу управляющего регистра, третий выход которого соединен с первым входом четвертого элемента И 14, вторым входом пятого элемента ИЛИ 37 и третьим входом первого элемента ИЛИ, пятый вход которого совместно с первым входом пятого элемента ИЛИ и первым входом одиннадцатого элемента И 35 подключен к седьмому выходу управляющего регистра. Выход первого элемента ИЛИ 10 соединен с первым входом пятого элемента И 18. Четвертый выход управляющего регистра соединен с первым входом шестого элемента И 19, выход которого соединен с первым входом седьмого элемента И 20. Пятый выход управляюшего регистра соединен с вторым входом седьмого элемента И 20, первым входом восьмого элемента И 21 и через элемент НЕ 22 - с первым входом

девятого элемента И 24. Выходы второго, третьего и четвертого, десятого и одиннадцатого элементов И соответственно подключены к входам второго элемента ИЛИ 11, выход которого соединен с управляющим входом третьего узла 9 сравнения. Выходы каждого элемента И 15-17 соответственно первой, второй и третьей групп соединены с входами соответствующих элементов ИЛИ группы 23 элементов ИЛИ, выходы третьего

регистра 8 и выходы группы 23 элементов ИЛИ соединены соответственно с первой и второй группами информационных входов третьего узла сравнения, выход которой соединен с вторым входом пятого элемента И 18, выход которого подключен к вторым

5 входам восьмого 21 и девятого 24 элементов И. Выход девятого элемента И подключен к первому управляющему выходу 32 устройства. Выходы седьмого и восьмого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ 25, выход которого подключен к второму управляющему выходу 33 устройства. Выход первого элемента И 4 соединен с третьими входами пятого 18 и шестого 19 элементов И. Первый информационный вход

5 6 устройства соединен с вторыми входами первого и второго узлов сравнения и элементов И 16 второй группы. Второй 30 и третий 31 информационные входы устройства соответственно подключены к вторым входам элементов И первой 15 и третьей 17 групп.

0 К первым входам элементов И первой и третьей групп соответственно подключены выходы четвертого 36 и пятого 37 элементов ИЛИ.

Регистры 1, 5, 7 и 8 являются тумблерными регистрами.

Первый 26, второй 27 и третий 28 управляющие входы устройства соединены соответственно с вторыми входами второго, третьего и четвертого элементов И. Четвертый управляюший вход 29 устройства подключен к

Q второму входу шестого элемента И. Пятый 38 и шестой 39 управляющие входы устройства соответственно соединены с вторыми входами десятого 34 и одиннадцатого 35 элементов И.

Устройство может работать в одном из

5 шести режимов. В первых четырех режи.мах устройство работает аналогично известному устройству.

В пятом режиме устройство работает следующим образом.

Оператор, .производящий отладку программ, устанавливает на регистре 7 управления пятый режим и режим отладки и при этом на пятом и шестом выходах регистра 7 появляются единичные потенциалы. При выполнении программы, подлежащей отладке, адреса выполняемых команд находятся в пределах, значения которых установлены на выходах регистров 1 и 5, следовательно, на выходе первого элемента И 4 будет разрешающий потенциал.

Каждая команда чтения из ОЗУ ЭВМ сопровождается управляющим потенциалом, который поступает из процессора через пятый управляющий вход 38 устройства на второй вход элемента И 34, на первый вход которого поступает положительный потенциал с шестого выхода управляющего регистра 7. С выхода десятого элемента И 34 положительный потенциал через второй элемент ИЛИ 11 поступает на управляющий вход третьего узла 9 сравнения и тем самым разрешается сравнение информации, набранной на третьем регистре 8 с информацией, находящейся на информационном входе 30. При этом на выходе четвертого элемента ИЛИ 36 формируется положительный потенциал и содержимое регистра адреса ОЗУ через первую группу элементов И 15 и группу 23 элементов ИЛИ поступит на второй информационный вход третьего узла 9 сравнения. При совпадении содержимого третьего регистра 8 с информацией, находящейся на информационном входе 30, на выходе узла 9 сравнения вырабатывается положительный потенциал, который поступает на второй вход пятого элемента И 18, на первый и третий входы которого поступают разрешающие потенциалы с выхода первого элемента ИЛИ 10 и первого элемента И 4. Положительный потенциал с выхода пятого элемента И 18 через восьмой элемент И 21 и третий элемент ИЛИ 25 поступает на второй управляющий выход 33 устройства, который соединен с регистром прерывания

ЭВМ. По этому сигналу ЭВМ, программа которой подлежит отладке, прерывает свою работу и осуществляет вызов программы обработки прерывания, которая в зависимости от отладочного задания программиста производит заранее определенные действия. В шестом режиме устройство вырабатывает сигнал прерывания при чтении информации из регистра общего назначения ЭВМ, номер которого совпадает с номером,

0 набранным на третьем регистре 8. Работа устройства в этом режиме отличается от пятого режима тем, что при чтении из регистра общего назначения ЭВМ вырабатывается управляющий сигнал на входе 39, который через элемент И 35 и элемент ИЛИ

11 поступает на опрос схемы сравнения, на второй вход которой через третий информационный вход 31, группу 17 элементов И и группу 23 элементов ИЛИ поступает номер регистра общего назначения. На первые

Q входы группы 17 элементов И поступает положительный потенциал с выхода пятого элемента ИЛИ 37, формирующийся из положительного потенциала, поступающего на первый вход пятого элемента ИЛИ 37 с седьмого выхода управляющего регистра 7.

Таким образом, по сравнению с известным предлагаемое устройство позволяет реализовать прерывание отлаживаемой программы при чтении информации из ОЗУ и РОН. Тем самым повышается эффективность отлад0 ки программ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1983 |

|

SU1138804A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для прерывания при отладке программ | 1987 |

|

SU1437868A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для прерывания при отладке программ | 1984 |

|

SU1171799A2 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для отладки программ | 1983 |

|

SU1293732A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для контроля вычислительного процесса ЭВМ | 1988 |

|

SU1596332A1 |

УСТРОЙСТВО ДЛЯ ПРЕРЫВАНИЯ ПРИ ОТЛАДКЕ ПРОГРАММ по авт. св. № 962945, отличающееся тем, что, с целью расширения класса решаемых задач путем обеспечения прерывания при чтении информации, в него введены десятый и одиннадцатый элементы И, четвертый и пятый элементы ИЛИ, причем первый выход управляющего регистра соединен с первым входом четвертого элемента ИЛИ, выход которого подключен к первым входам элементов И первой группы, шестой выход управляющего регистра соединен с первым входом десятого элемента И, вторым входом четвертого элемента ИЛИ и четвертым входом первого элемента ИЛИ, седьмой выход управляющего регистра подключен к первому входу одиннадцатого элемента И, первому входу пятого элемента ИЛИ и пятому входу первого элемента ИЛИ, третий выход управляющего регистра соединен с вторым входом пятого элемента ИЛИ, выход которого подключен к первым входам элементов И третьей группы, пятый и щестой управляющие входы соединены соответственно с вторыми входами десятого и одиннадцатого элементов И, выходы которых соответственно подключены к четвертому и пятому входам второго элемента И.

| Устройство для прерывания при отладке программ | 1980 |

|

SU962945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1983-12-27—Подача