(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для прерывания при отладке программ | 1980 |

|

SU962945A1 |

| Устройство для прерывания при отладке программ | 1983 |

|

SU1168954A2 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| СПОСОБ КОНТРОЛЯ И ОТЛАДКИ ПРОГРАММ РЕАЛЬНОГО ВРЕМЕНИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2050588C1 |

| Устройство для отладки программ | 1983 |

|

SU1138804A1 |

Изобретение относится к вычислительной технике и может быть использовано при отладке программ. Целью изобретения является повьппение быстродействия отладки программ. Устройство содержи т четыре узла сравнения, одиннадцать элементов И, четыре элемента ИЛ11, три блока элементов И, блок элементов ИЛИ, пять регистров, управляющий регистр, два элемента НЕ. Устройство обеспечивает вьщачу в ЭВМ управляющего сигнала при возникновении назначенной ситуации с учетом анализа и идентификации обрабатываемой информации, что позволяет повысить быстродействие при отладке. 1 ил.

4iib

00

ОС

а

QO

Изобретение относится к вычислительной технике, а именно к устройствам для программного управления, и может быть использовано при отладке програм ; для ЭВМ.

Цель изобретения - сокращение времени отладки программ.

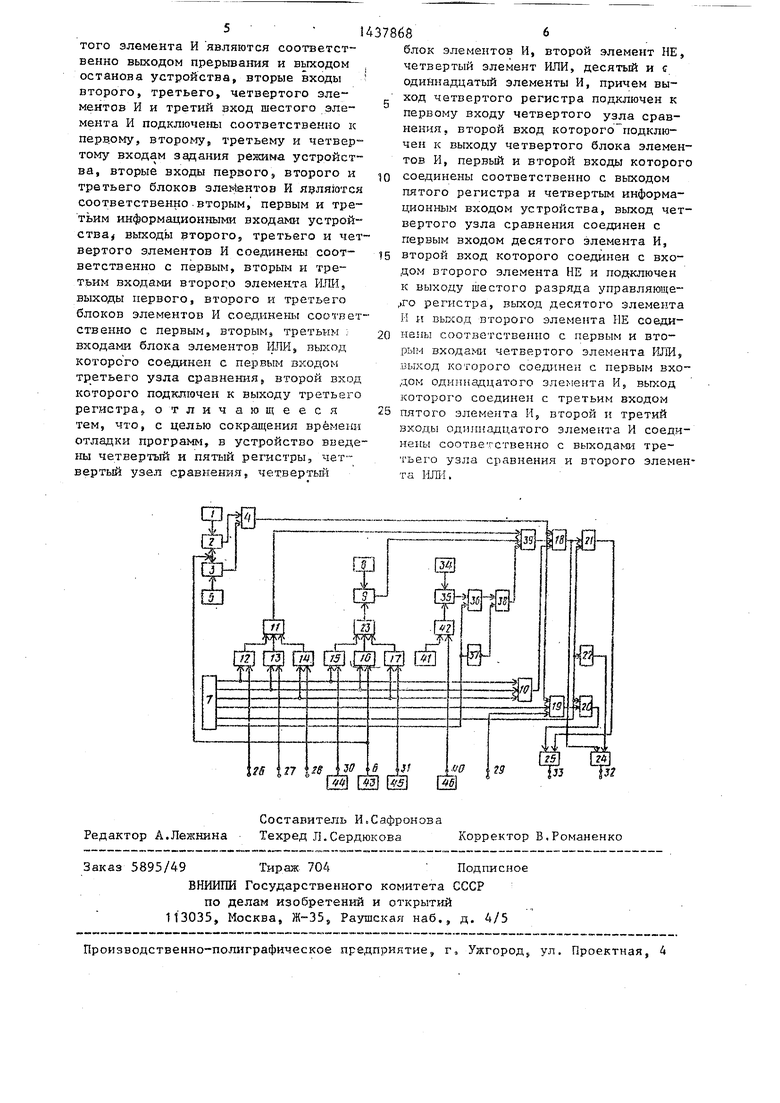

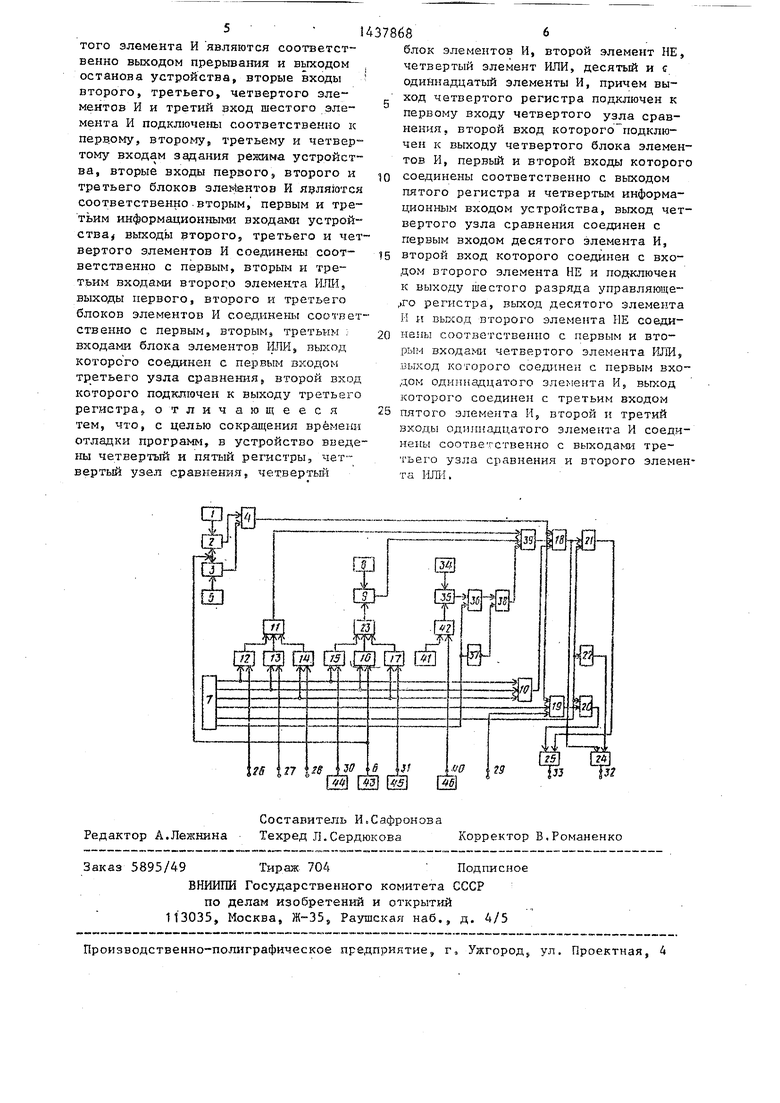

На чертеже представлена структурная схема предлагаемого, устройства.

Устройство содержит первый регистр I5 первый 2 и второй 3 узлы сравнения, первый элемент И 4, второй регистр 5, первьш информационный вход 6, управляющий регистр 7, третий регистр 8, третий узел 9 сравнения, первый 10 и второй 11 элементы ИЛИ, второй 12s третр-ш 13 и четвертый 14 элементы И, первый 15, второй 6 и третий 17 блоки элементов И, пя тьш 18, шестой 13, седьмой 20 и восьмой 21 элементы И, первый элемент НЕ 22 5 блок 23 элементов ШШ, девятый элемент И 24, третий элемент ИЛИ 25, первый 26, второй 27, третий 28 и четвертый 29 входы задания режима, второй 30 и третий 31 информационные входы, выходы 32 и 33 останова прерывания устройства, четвертый регистр 34, четвертый узел 35 сравнения, десятый элемент И 36,. второй элемент НЕ 373 четвертьй элемент ИЛИ 38, одиннадцатый элемент И 39, четвертый информационный вход 40, пятый регист 41 и четвертый блок элементов И 42.

Кроме того, на чертеже показаны узлы ЭВМ, которые не входят в состав предлагаемого устройства, а служат ,пишь для пояснения его работы; регистр 43 номера команды,, регистр 44 адреса записи, регистр 45 номера регистра общего назначения центрального процессора и буферный регистр 46 центрального процессора,

Устройство может работать в одном из семи режимов.

Подготовка устройства к работе в любом из семи режимов начинается с установки зоны отладки путем занесе- 1ШЯ на регистр 1 первого и на регистр 5 последнего адресов программы, подлежащей отладке.

Во время работы ЭВМ номер выполняемой команды поступает на вторые входы узлов 2 и 3 сравнения. На выходе Первого узла 2 сравнения присутствует положительный потенциап только в случае если номер команды больше

номера, набра пюго на регистре 1 , а на выходе второго узла 3 сравнения присутствует сигнал положительной г полярности только в случае, если номер команды меньше номера, набранного на регистре 5.

Таким образом, нулевой потенциал, появляющийся на первых входах элемен0 тов И 18 и 19, блокирует работу устройства вне зоны отладки.

При работе устройства в ЭВМ может быть выдан один из двух управляющих сигналов:

5 сигнал с выхода 33, вызывающий прерывание отлаживаемой программы и вызов вклинивающейся программы, которая в зависимости от отладочного за- даьшя програмш1ста производит зара0 нее определенные им действия;

сигнал с выхода 32, вызьшающий останов вычислительного процесса.

При наличии единичного потенциала на пятом выходе регистра 7 управляю5 щий сигнал может быть выдан в ЭВМ с выхода 33, в противном случае - с выхода 32. Во всех режимах, кроме режима 4, необходимым условием выдачи в ЭВМ управляющего сигнала является

0 -одновременное появление единичного потенциала на всех трех входах элемента И 39.

В первых четырех режимах устройство работает аналогично известному

5 устройству. Это обеспечивается тем, что нул евой потенциал, присутствую- ь Д1Й в названных режимах на шестом выходе управляющего регистра 7, через элемент НЕ 37 и элемент ИШ- 38

0 обусловливает появление разрещающего сигнала на третьем входе элемента И 39.

Режим 5 определяется наличием единичных потенциалов на первом и шестом

5 входах тумблерного управляющего регистра 7. В этом режиме условие, необходимое для выработки управляющего сигнала, реализуется при выполнении записи идентифицированной информации в определенную ячейку памяти. На первый вход элемента И 39 сигнал, сопровождающий команду записи в оперативную память, поступает из процессора ЭВМ через управляющей вход 26, элемент И 12 и элемент 1ШЛ 11. На второй вход элемента И 39 сигнал поступает с узла 9 сравнения при совпадении адреса записи, набранного на туь блерном регистре 8, с информацией

0

5

на регистре 44 адреса записи ЭВМ, который поступает на вторые входы узла 9 сравнения через информационный вход 30 устройства, блок элементов И 15 и блок элементов ИЛИ 23. На третий вход элемента Р1 39 сигнал поступает с узла 35 сравнения через элемент И 36 и элемент ИЛИ 38 при совпадении информации, набранной на тумблерном ре- IQ ладке программ, содержащее первый, гистре 34, с информацией, записывае- второй, третий регистры, три узла

И,

мой в ячейку памяти. Эта информация поступает на вторые входы узла 35 сравнения с буферного регистра 46 центрального процессора ЭВМ через информационный вход 40 устройства и блок элементов И 42. Разряды информации, участвуювдге в сравнении, определяются кодом, предварительно занесенным на тумблерньп регистр 41 маски.

Режим 6 определяется наличием еди- fffl4Hi5 x потенциалов на втором и шестом выходах регистра 7. В этом режиме условие, необходимое для выработки управляющего сигнала, реализуется при положительном результате идентификации информации на буферном регистре центрального процессора в момент выполнения команды с определенным iTOMepoM. ila первый вход элемента И 39 сигнал, сопровождающий включение каждой команды, поступает из процессора ЭВМ через управляющий вход 27, элемент И 13 и элемент ИЛИ 11, На второй вход элемента И 39 сигнал поступает с узла 9 сравнения при совпадении номера команды, набранного на регистре 8, с информацией на регистре 43 номера команды ЭВМ, которая поступает на вторые входы узла 9 сравнения через информационный вход 6 устройства, блок элементов И 16 и блок элементов ИЛИ 23. На третий вход элемента И 39 сигнал поступает с узла 35 сравнения через элемент И 36 и элемент ИЛИ 38 при совпадении информации, набранной на тумблерном регистре 34, с информацией, про-пущен- ной с буферного регистра 46 ЭВМ через блок элементов И 42 в соответствии с кодом маски, предварительно занесенным на регистр 41.

Режим 7 определяется наличием единичных потенциалов на третьем и шестом выходах регистра 7. При этом в отличие от режима 5 в качестве входов устройства используются вход 28 задания режима и информационньш вход 31 вместо входов 26 и 30 соответст15

20

25

30

35

40

45

50

55

сравнения, девять элементов и, три блока элементов И, блок элементов 1-ШИ, три элемента ИЛИ, пер вый элемент НЕ, управляющий регистр, причем выходы первого и в рого регистров соединены с первым входами соответственно первого и в рого узлов сравнения, выходы котор соединены соответственно с первым вторым входам- первого элемента И, вторые входы первого и второго узл сравнения объединены и подключены первому информационному входу устройства, первые входы второго элем та И, первого блока элементов И и первого элемента ИЛИ подключены к ходу первого разряда управляющего гистра, первые входы третьего элем та И, второго блока элементов И и второй вход первого элемента ИЛИ п ключены к выходу второго разряда у равляющего регистра, первые входы четвертого элемента И, третьего бл ка элементов И и третий вход перво элемента ИЛИ подключены к выходу т тьего разряда управляющего регистр выход первого элемента ИЛИ соедине с первым входом пятого элемента И, второй вход которого соединен с пе вым входом шестого элемента И и по ключен к выходу первого элемента И первые входы восьмого и девятого э ментов И подключены к выходу пятог элемента И, выход четвертого разря управляющего регистра соединен с в рым входом шестого элемента И, вых которого соединен с первым входом седьмого элемента И, второй вход к торого соединен с вторым входом во мого элемента И и входом первого э мента НЕ и подключен к выходу пято разряда управляющего регистра, вых ды седьмого и восьмого элементов И соединены соответственно с первым вторым входами третьего элемента И выход первого элемента НЕ соединен вторым входом девятого элемента И, выходы третьего элемента И.Ш и дев

венно, а управляющий сигнал вырабатывается устройством при записи идентифицированной информации в определенный центральный регистр.

Формула изобретения Устройство для прерывания при отИ,

5

0

5

0

5

0

5

0

5

сравнения, девять элементов и, три блока элементов И, блок элементов 1-ШИ, три элемента ИЛИ, первый элемент НЕ, управляющий регистр, причем выходы первого и второго регистров соединены с первым 1 входами соответственно первого и второго узлов сравнения, выходы которых соединены соответственно с первым и вторым входам- первого элемента И, вторые входы первого и второго узлов сравнения объединены и подключены к первому информационному входу устройства, первые входы второго элемента И, первого блока элементов И и первого элемента ИЛИ подключены к выходу первого разряда управляющего регистра, первые входы третьего элемента И, второго блока элементов И и второй вход первого элемента ИЛИ подключены к выходу второго разряда управляющего регистра, первые входы четвертого элемента И, третьего блока элементов И и третий вход первого элемента ИЛИ подключены к выходу третьего разряда управляющего регистра, выход первого элемента ИЛИ соединен с первым входом пятого элемента И, второй вход которого соединен с первым входом шестого элемента И и подключен к выходу первого элемента И, первые входы восьмого и девятого элементов И подключены к выходу пятого элемента И, выход четвертого разряда управляющего регистра соединен с вто-. рым входом шестого элемента И, выход которого соединен с первым входом седьмого элемента И, второй вход которого соединен с вторым входом восьмого элемента И и входом первого элемента НЕ и подключен к выходу пятого разряда управляющего регистра, выходы седьмого и восьмого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход первого элемента НЕ соединен с вторым входом девятого элемента И, выходы третьего элемента И.Ш и девятого элемента И являются соответственно выходом прерывания и выходом , останова устройства, вторые входы второго, третьего, четвертого элементов И и третий вход шестого элемента И подключены соответственно к первому, второму, третьему и четвертому входам задания режима устройст ва, вторые входы первого, второго и третьего блоков элегИентов И являются соответственно.вторым, первым и третьим информационными входами устрой- ства выходы второго, третьего и четвертого элементов И соединены соответственно с первым, вторым и третьим входами второго элемента ИШ, выходы первого, второго и третьего блоков элементов И соединены соответственно с первым, вторым, третьим : входами блока элементов ЕПИ, выход которого соединен с первым входом тр етьего узла сравнения, второй вход которого подключен к выходу третьего регистра, отличающееся тем, что, с целью сокращения врёмегш отладки программ, в устройство выедены четвертый и пятый регистры, четвертый узел сравнения, четвертьш

,

ЗШ j j

378686

блок элементов И, второй элемент НЕ, четвертый элемент ИЛИ, десятый и с одиннадцатый элементы И, причем вы- ход четвертого регистра подключен к первому входу четвертого узла сравнения, второй вход которого подклю- чен к выходу четвертого блока элементов И, первый и второй входы которого

10 соединены соответственно с выходом пятого регистра и четвертым информационным входом устройства, выход четвертого узла сравнения соединен с первым входом десятого элемента И,

15 второй вход которого соединен с входом второго элемента НЕ и подключен к выходу шестого разряда управляюще- го регистра, выход десятого элемента И и вьксод второго элемента НЕ соеди20 йены соответственно с первым и вторым входам четвертого элемента 1ШИ, выход которого соединен с первым входом одиннадцатого элемента И, выход которого соединен с третьим входом

пятого элемента И, второй и третий входы одилиадцатого эле.мента И соединены соответственно с выхода третьего узла сравнения и второго элемента ИШ.

рз 13

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для прерывания при отладке программ | 1980 |

|

SU962945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-15—Публикация

1987-05-18—Подача