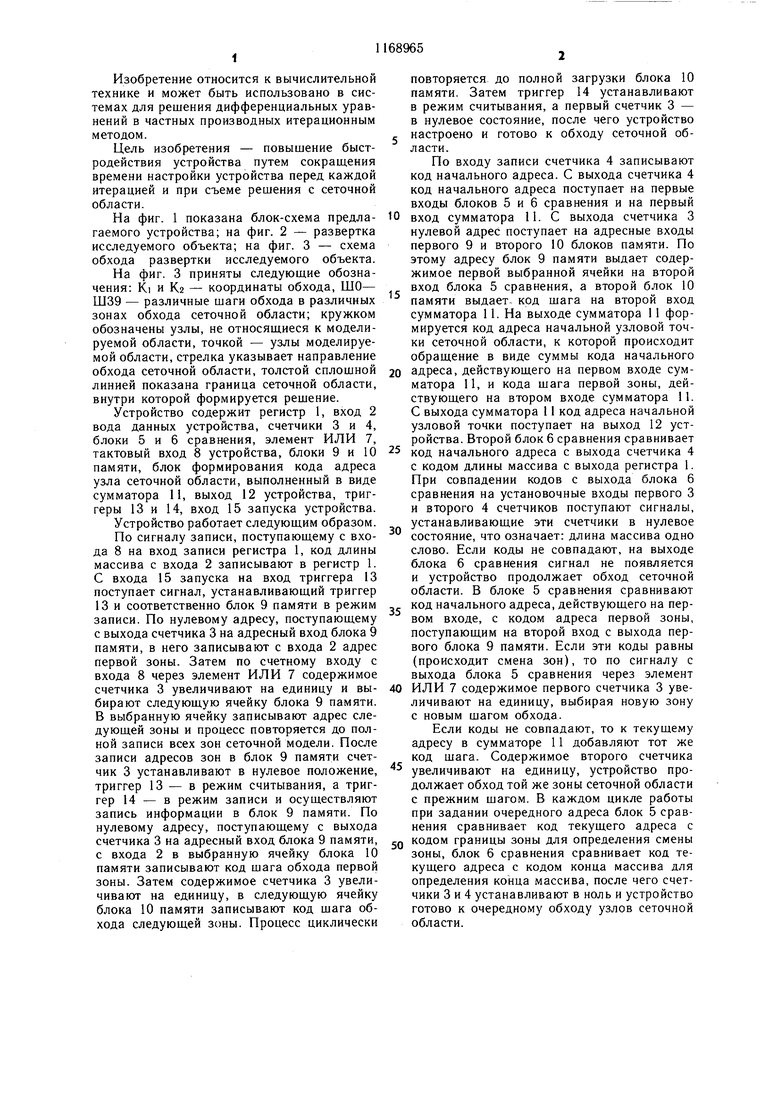

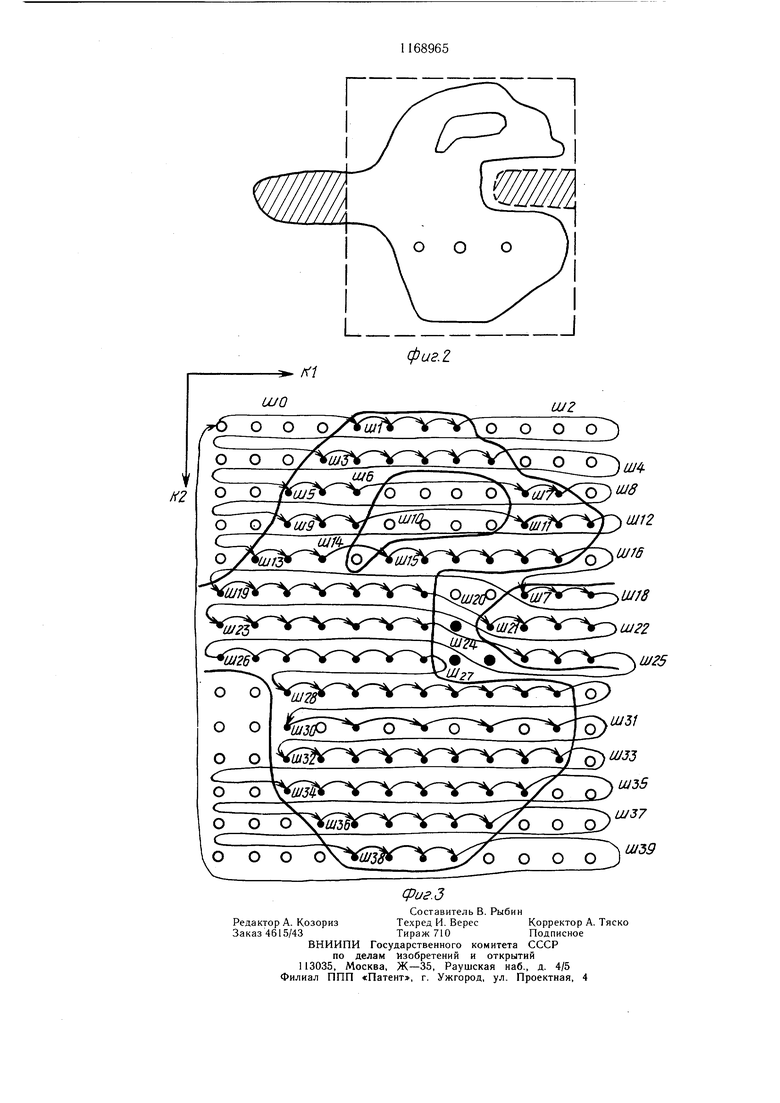

Изобретение относится к вычислительной технике и может быть использовано в системах для решения дифференциальных уравнений в частных производных итерационным методом. Цель изобретения - повышение быстродействия устройства путем сокращения времени настройки устройства перед каждой итерацией и при съеме решения с сеточной области. На фиг. 1 показана блок-схема предлагаемого устройства; на фиг. 2 - развертка исследуемого объекта; на фиг. 3 - схема обхода развертки исследуемого объекта. На фиг. 3 приняты следующие обозначения: Ki и К2 - координаты обхода, ШО- Ш39 - различные шаги обхода в различных зонах обхода сеточной области; кружком обозначены узлы, не относящиеся к моделируемой области, точкой - узлы моделируемой области, стрелка указывает направление обхода сеточной области, толстой сплошной линией показана граница сеточной области, внутри которой формируется решение. Устройство содержит регистр 1, вход 2 вода данных устройства, счетчики 3 и 4, блоки 5 и 6 сравнения, элемент ИЛИ 7, тактовый вход 8 устройства, блоки 9 и 10 памяти, блок формирования кода адреса узла сеточной области, выполненный в виде сумматора 11, выход 12 устройства, триггеры 13 и 14, вход 15 запуска устройства. Устройство работает следующим образом. По сигналу записи, поступающему с входа 8 на вход записи регистра 1, код длины массива с входа 2 записывают в регистр 1. С входа 15 запуска на вход триггера 13 поступает сигнал, устанавливающий триггер 13 и соответственно блок 9 памяти в режим записи. По нулевому адресу, поступающему с выхода счетчика 3 на адресный вход блока 9 памяти, в него записывают с входа 2 адрес первой зоны. Затем по счетному входу с входа 8 через элемент ИЛИ 7 содержимое счетчика 3 увеличивают на единицу и выбирают следующую ячейку блока 9 памяти. В выбранную ячейку записывают адрес следующей зоны и процесс повторяется до полной записи всех зон сеточной модели. После записи адресов зон в блок 9 памяти счетчик 3 устанавливают в нулевое положение, триггер 13 - в режим считывания, а триггер 14 - в режим записи и осуществляют запись информации в блок 9 памяти. По нулевому адресу, поступающему с выхода счетчика 3 на адресный вход блока 9 памяти, с входа 2 в выбранную ячейку блока 10 памяти записывают код шага обхода первой зоны. Затем содержимое счетчика 3 увеличивают на единицу, в следующую ячейку блока 10 памяти записывают код шага обхода следующей зоны. Процесс циклически 1 52 повторяется до полной загрузки блока 10 памяти. Затем триггер 14 устанавливают в режим считывания, а первый счетчик 3 - в нулевое состояние, после чего устройство настроено и готово к обходу сеточной области. По входу записи счетчика 4 записывают код начального адреса. С выхода счетчика 4 код начального адреса поступает на первые входы блоков 5 и 6 сравнения и на первый вход сумматора П. С выхода счетчика 3 нулевой адрес поступает на адресные входы первого 9 и второго 10 блоков памяти. По этому адресу блок 9 памяти выдает содержимое первой выбранной ячейки на второй вход блока 5 сравнения, а второй блок 10 памяти выдает- код шага на второй вход сумматора 11. На выходе сумматора 11 формируется код адреса начальной узловой точки сеточной области, к которой происходит обращение в виде суммы кода начального адреса, действующего на первом входе сумматора 11, и кода шага первой зоны, действующего на втором входе сумматора 11. С выхода сумматора 11 код адреса начальной узловой точки поступает на выход 12 устройства. Второй блок 6 сравнения сравнивает код начального адреса с выхода счетчика 4 с кодом длины массива с выхода регистра 1. При совпадении кодов с выхода блока 6 сравнения на установочные входы первого 3 и второго 4 счетчиков поступают сигналы, устанавливающие эти счетчики в нулевое состояние, что означает: длина массива одно слово. Если коды не совпадают, на выходе блока 6 сравнения сигнал не появляется и устройство продолжает обход сеточной области. В блоке 5 сравнения сравнивают код начального адреса, действующего на первом входе, с кодом адреса первой зоны, поступающим на второй вход с выхода первого блока 9 памяти. Если эти коды равны (происходит смена зон), то по сигналу с выхода блока 5 сравнения через элемент ИЛИ 7 содержимое первого счетчика 3 увеличивают на единицу, выбирая новую зону с новым шагом обхода. Если коды не совпадают, то к текущему адресу в сумматоре 11 добавляют тот же код шага. Содержимое второго счетчика увеличивают на единицу, устройство продолжает обход той же зоны сеточной области с прежним шагом. В каждом цикле работы при задании очередного адреса блок 5 сравнения сравнивает код текущего адреса с кодом границы зоны для определения смены зоны, блок 6 сравнения сравнивает код текущего адреса с кодом конца массива для определения конца массива, после чего счетчики 3 и 4 устанавливают в ноль и устройство готово к очередному обходу узлов сеточной области.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностное устройство для решения конечно-разностных уравнений | 1984 |

|

SU1236499A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1149278A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1095190A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1160434A1 |

| Устройство для вычисления параметров сеток для решения разностных уравнений | 1986 |

|

SU1413642A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

УСТРОЙСТВО ДЛЯ ОБХОДА УЗЛОВ СЕТОЧНОЙ ОБЛАСТИ, содержащее первый и второй счетчики, регистр, вход записи которого является тактовым входом устройства, вход ввода данных которого подключен к информационным входам первого и второго счетчиков и регистра, первый и второй блоки сравнения и элемент ИЛИ, выход которого подключен к счетному входу первого счетчика, вход установки нуля которого соединен с входом установки нуля второго счетчика и подключен к выходу первого блока сравнения, первый вход которого соединен с выходом регистра, выход второго счетчика подключен к второму входу первого блока сравнения и к первому входу второго блока сравнения, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с входом записи второго счетчика и с тактовым входом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены два триггера, два блока памяти и блок формирования кода адреса узла сеточной области, выполненный в виде сумматора, выход которого является выходом устройства, вход запуска которого подключен к установочным входам первого и второго триггеров, выходы которых соединены с входами записи - чтения соответственно первого и второго блоков g памяти, выходы которых подключены соответственно к второму входу второго блока (Л сравнения и к первому входу сумматора, второй вход которого соединен с выходом второго счетчика, выход первого счетчика подключен к адресным входам первого и второго блоков памяти, информационные входы которых являются входом ввода данных устройства. 05 00 со Oi СП

| Вероятностное устройство для решения конечно-разностных уравнений | 1972 |

|

SU477418A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обхода узлов сеточной области | 1981 |

|

SU955084A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1984-02-15—Подача