со с

tsD

1 и

Изобретение относится к цифровой вычислительной технике, а именно к устройствам для обработки цифровых данных, и может быть использовано для расчета параметров множества гру бых сеток в отношении к исходной сетке при решении уравнений математической физики.

Цель изобретения - повьшение быстродействия.

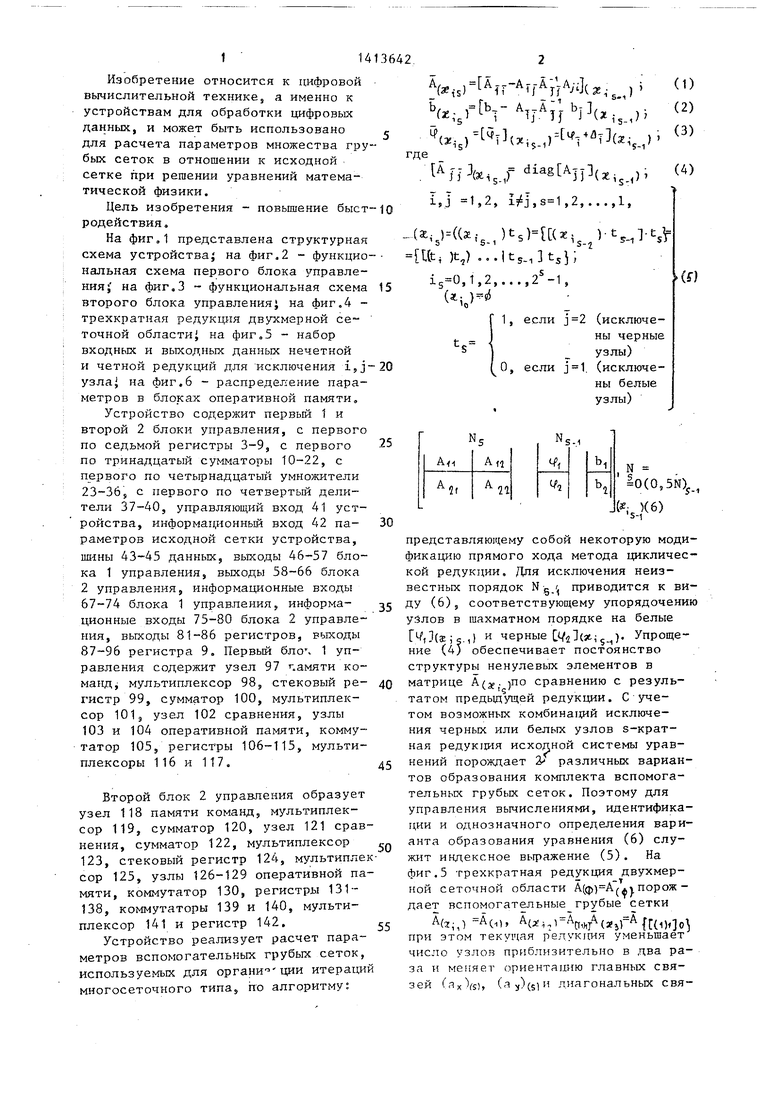

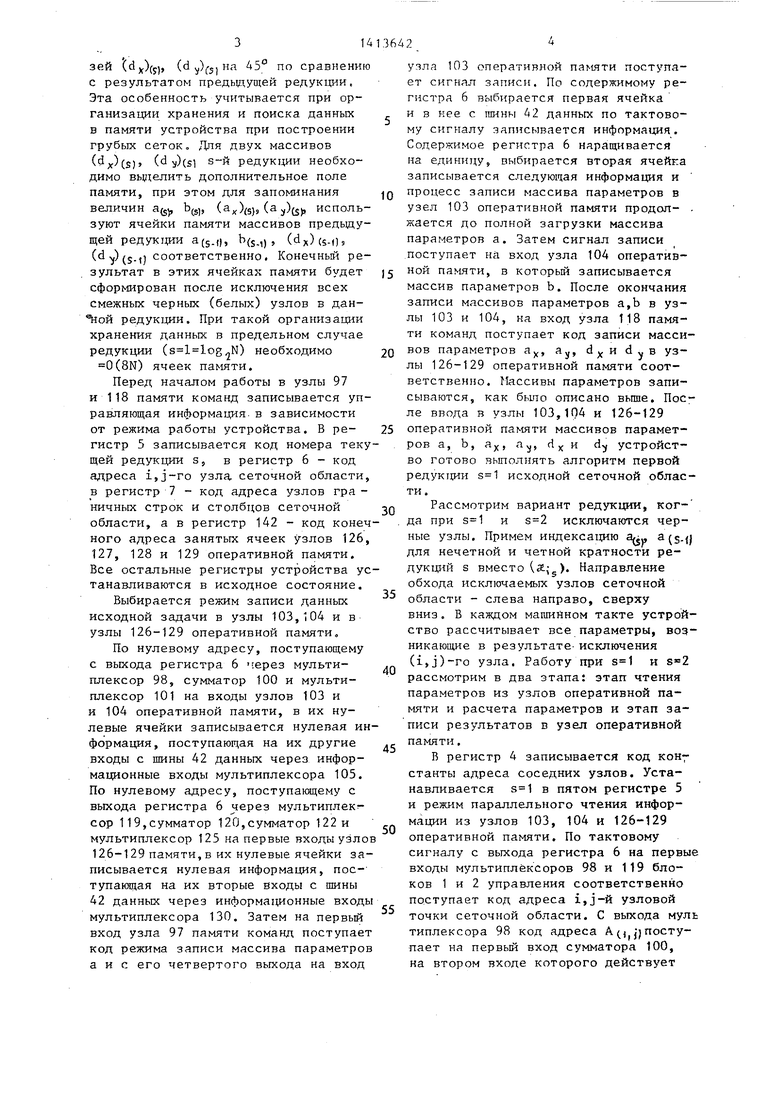

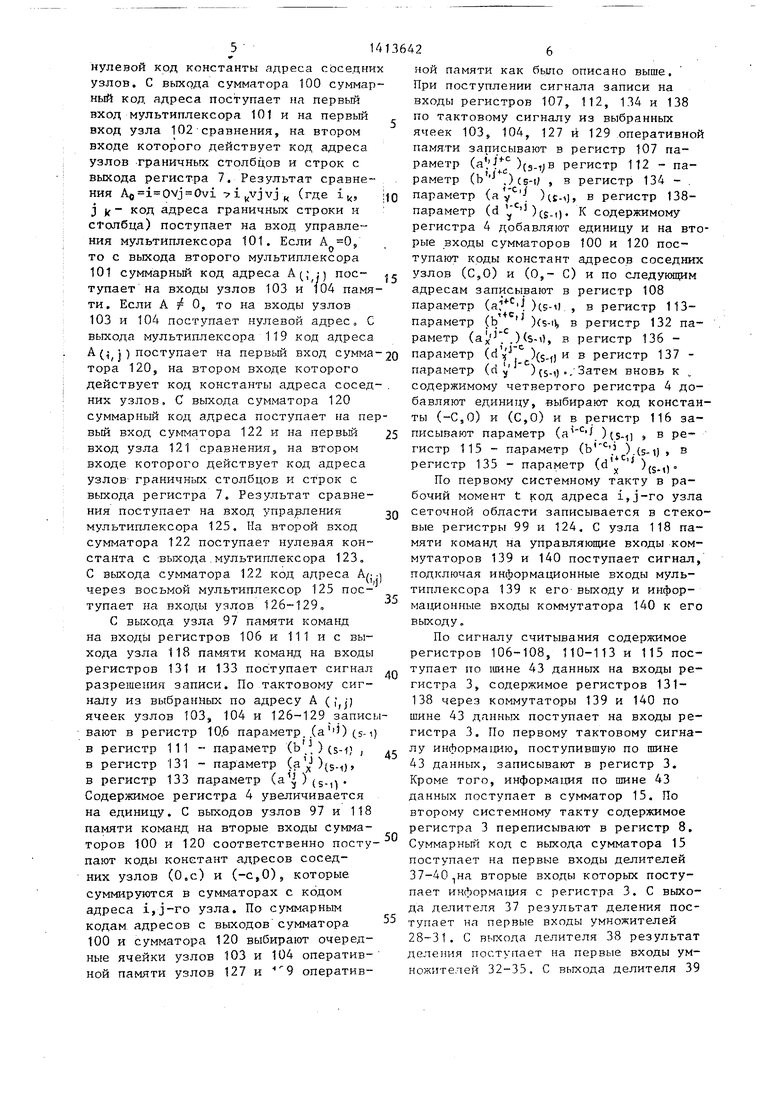

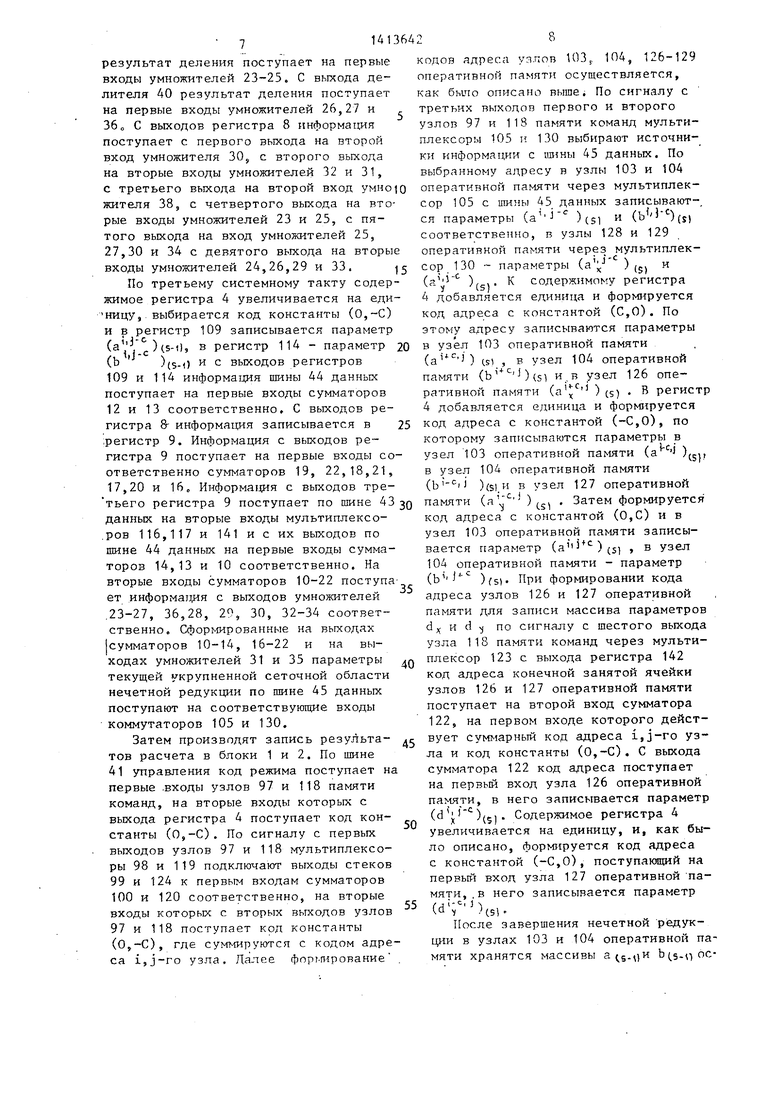

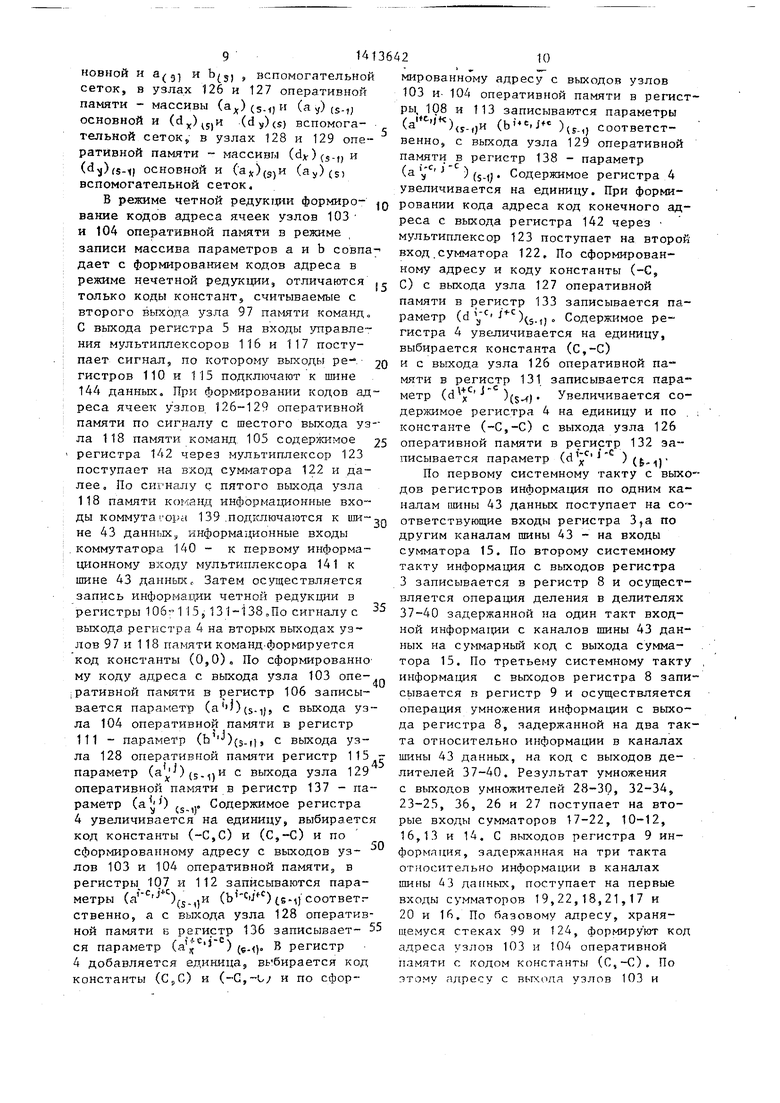

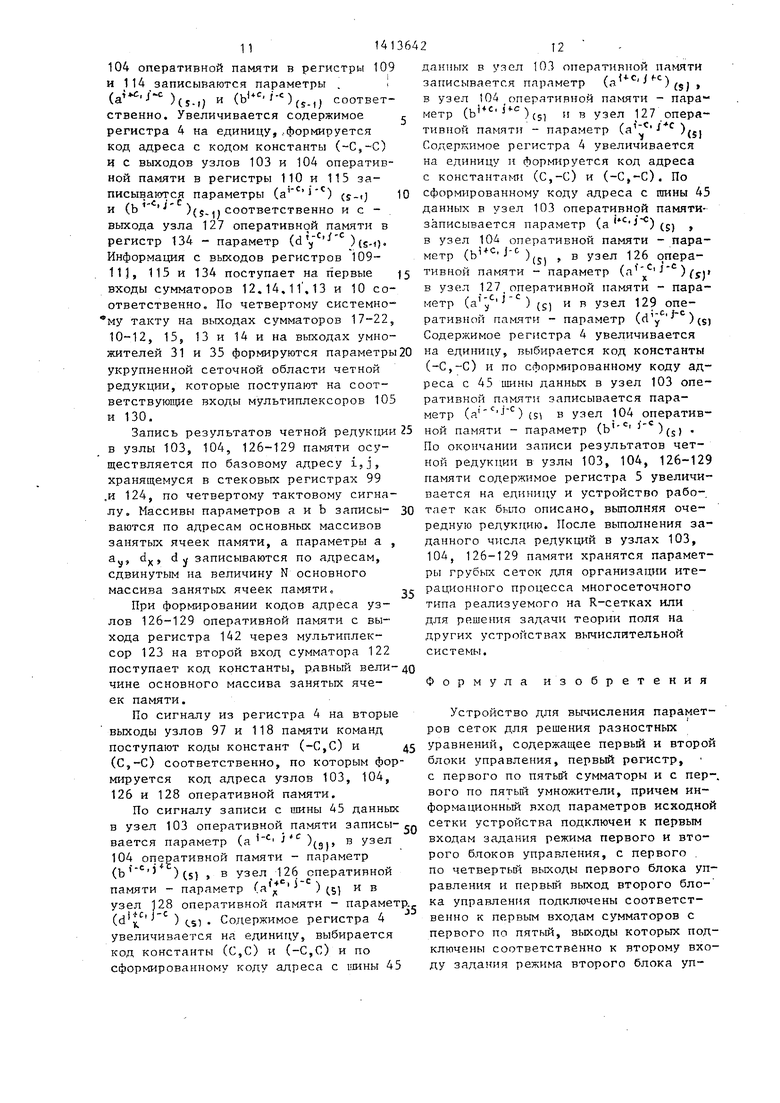

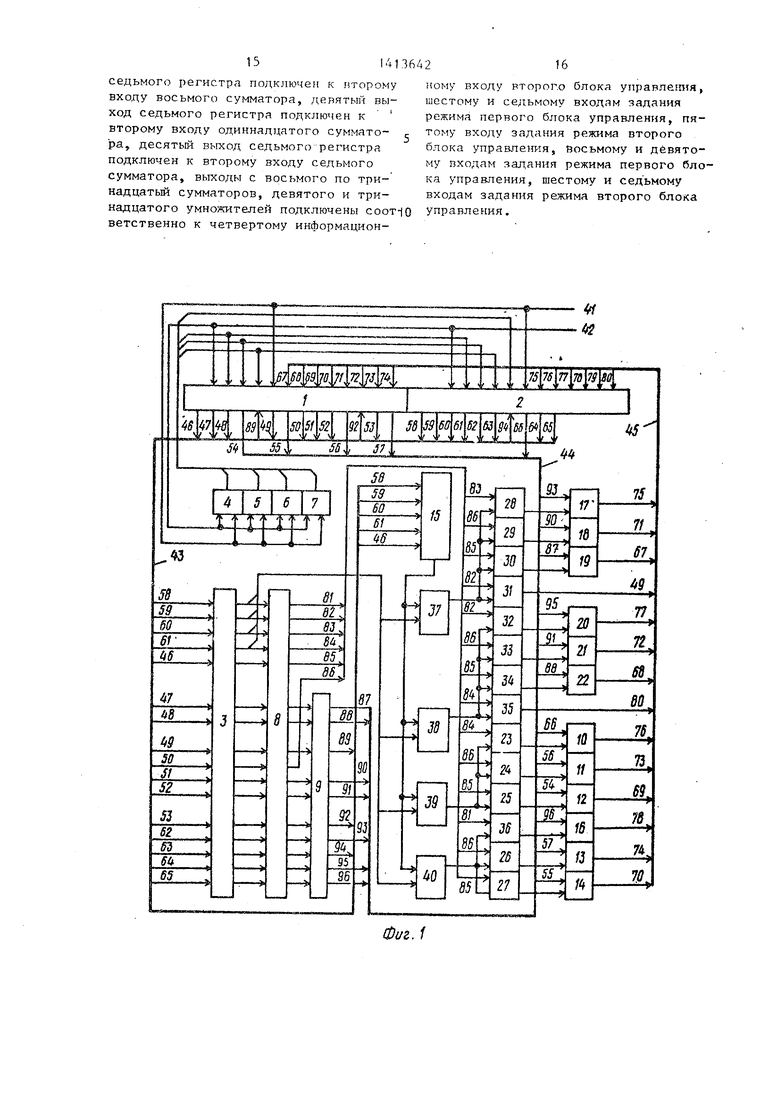

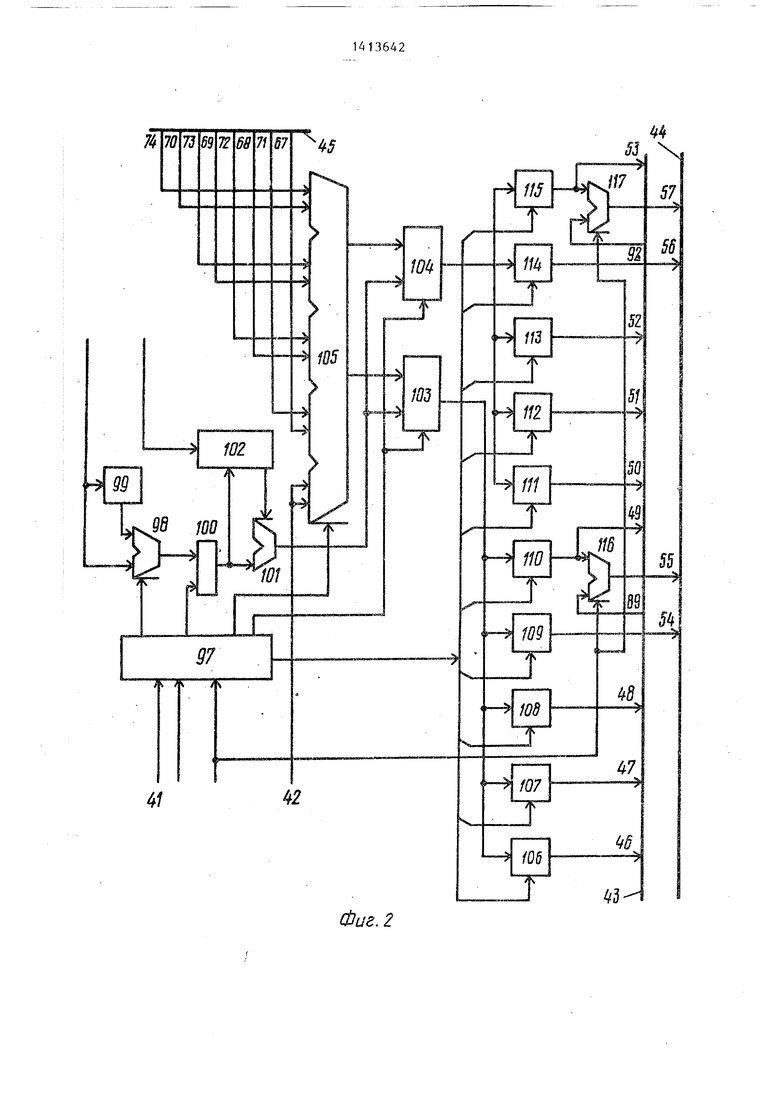

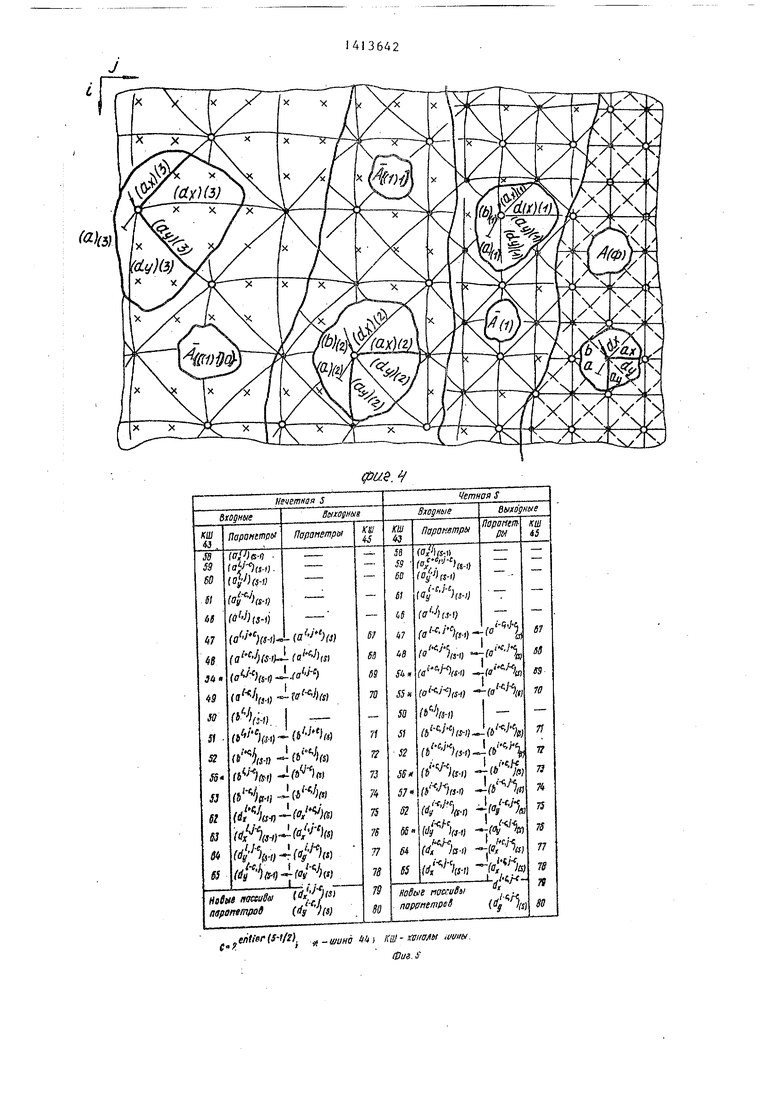

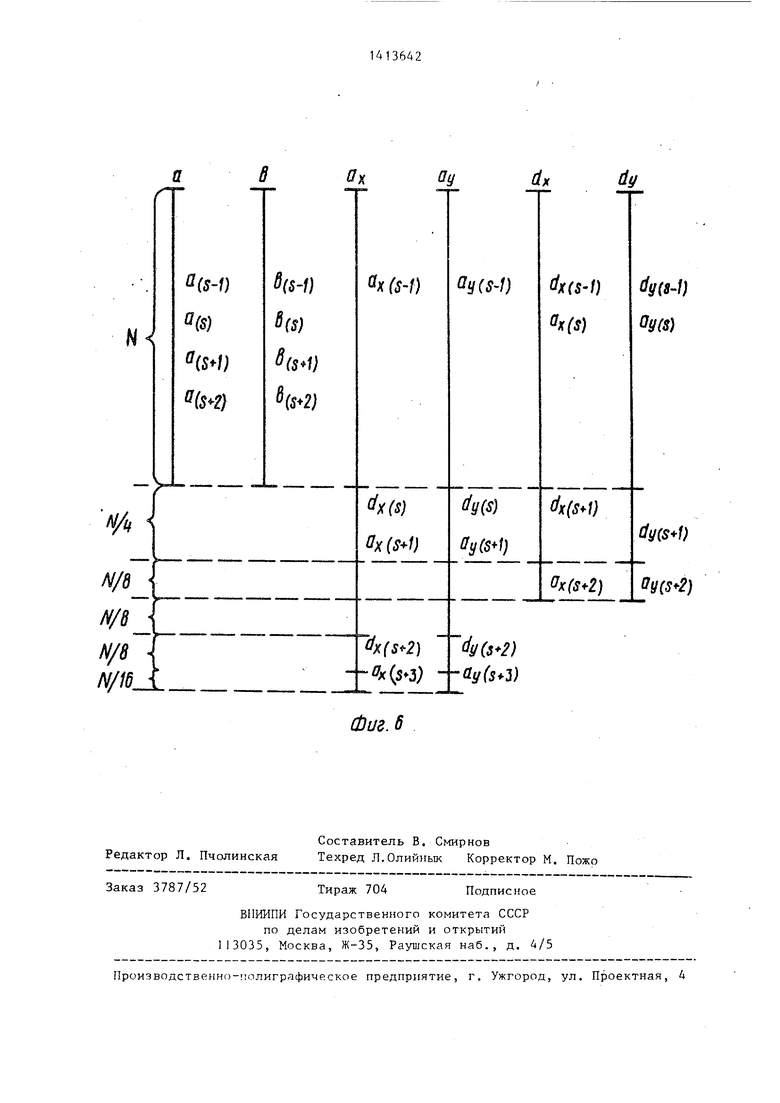

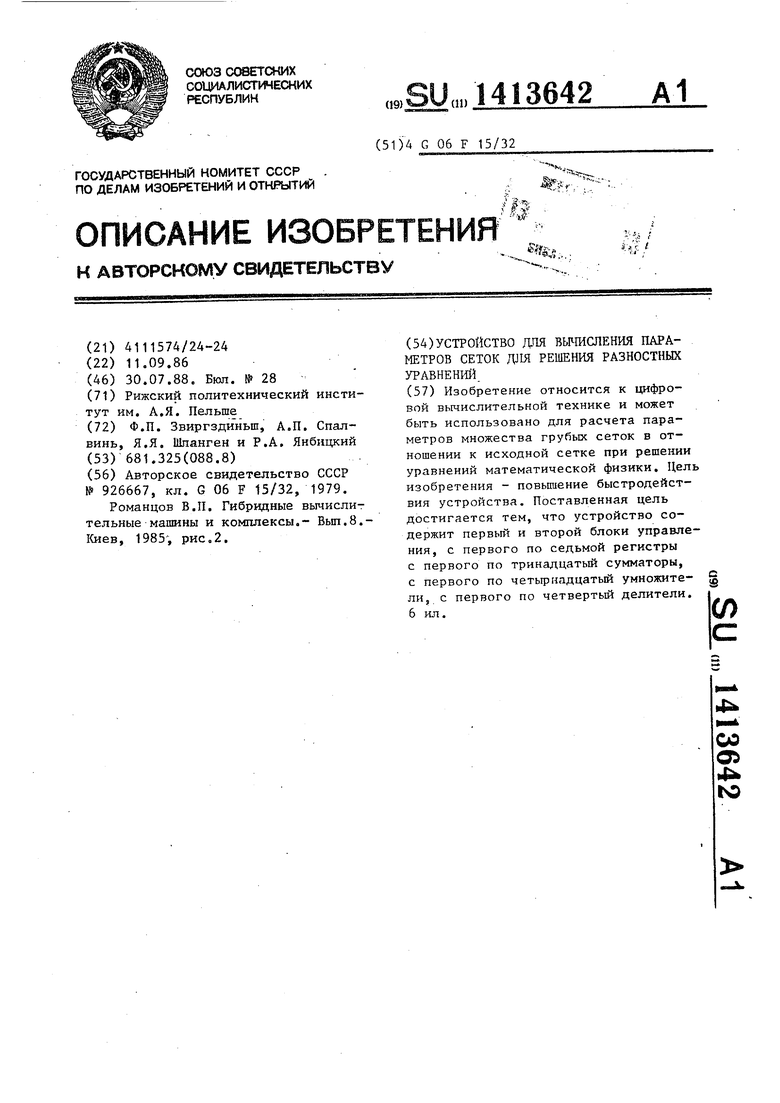

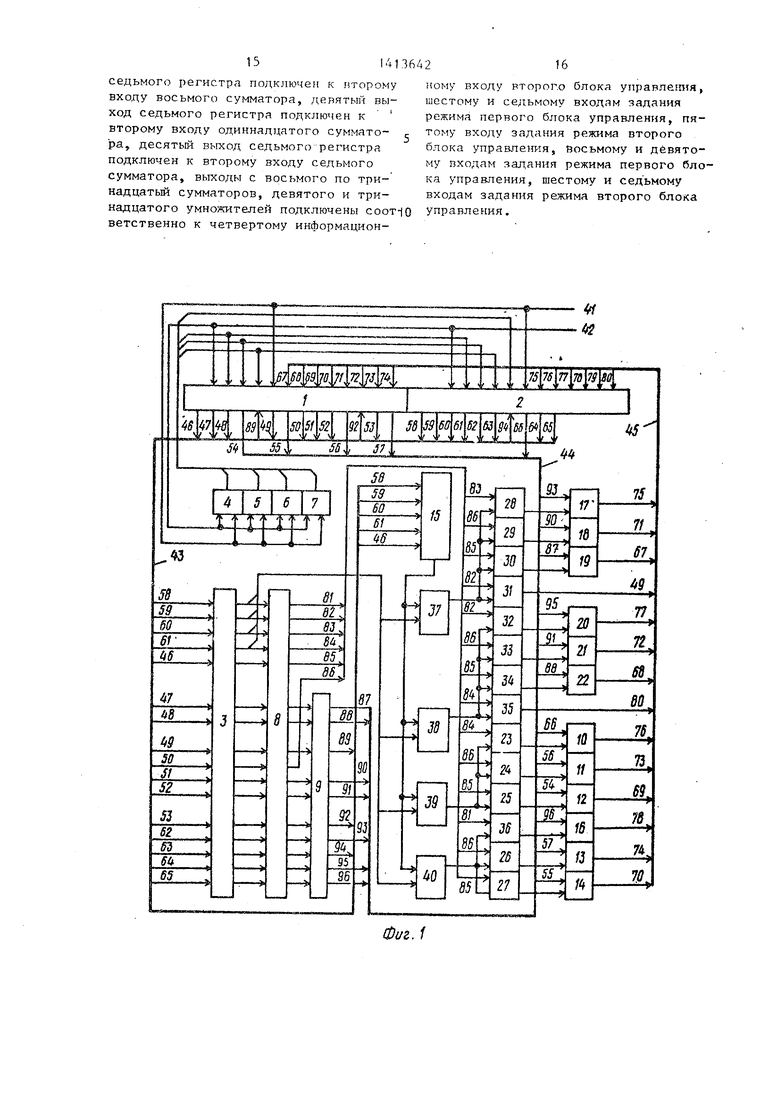

На фиг,1 представлена структурная схема устройстваi на фиг,2 - функциональная схема первого блока управления; на фиг.З функциональная схема второго блока управления на фиг,4 - трехкратная редукция двухмерной се- точной областиi на фиг.5 - набор входных и выходных данных нечетной и четной редукций для исключения i,j узла на фиг.6 - распределение параметров в блоках оперативной памяти.

Устройство содержит первьм 1 и второй 2 блоки управления, с первого по седьмой регистры 3-9, с первого по тринадцатый сумматоры 10-22, с первого по четырнадцатый умножители 23-36, с первого по четвертый делители 37-40, управляющий вход 41 устройства, информационный вход 42 параметров исходной сетки устройства, Ш1ны 43-45 данных, выходы 46-57 блока 1 управления, выходы 58-66 блока 2 управления, информационные входы 67-74 блока 1 управления, информационные входы 75-80 блока 2 управления, выходы 81-86 регистров, выходы 87-96 регистра 9. Первый блоч 1 управления содержит узел 97 памяти ко- магщ, мультиплексор 98, стековый регистр 99, сумматор 100, мультиплексор 101, узел 102 сравнения, узлы 103 и 104 оперативной памяти, коммутатор 105, регистры 106-115, мультиплексоры 116 и 117.

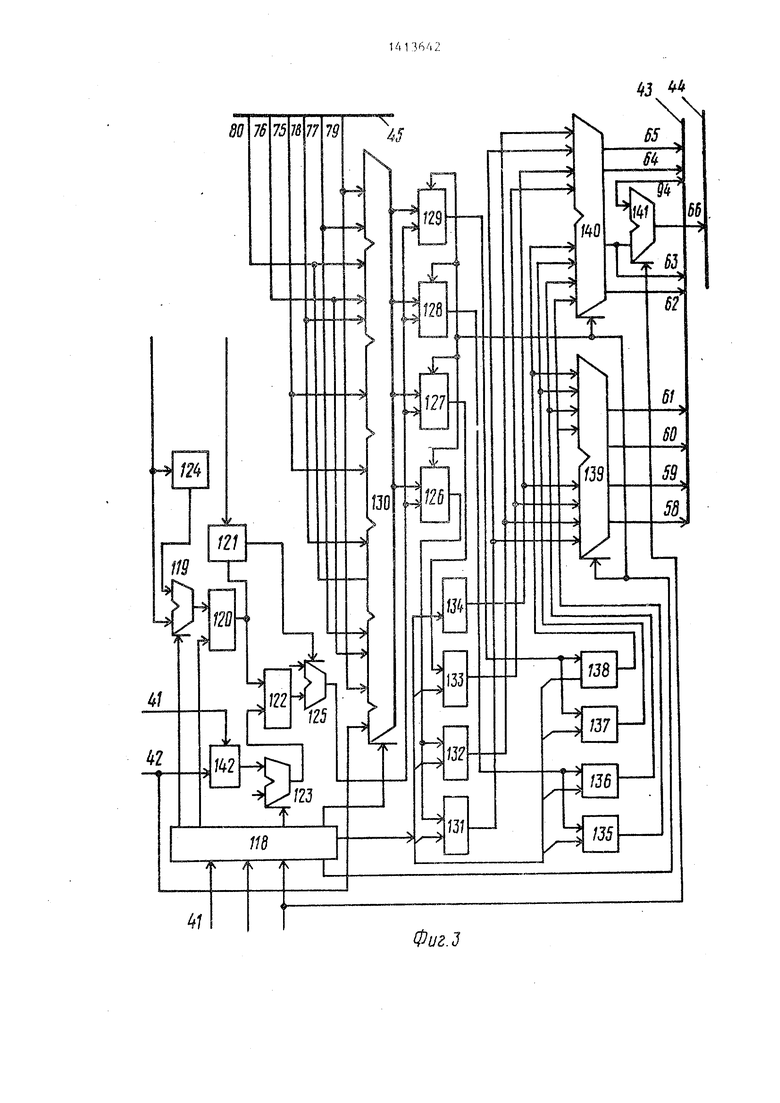

Второй блок 2 управления образует узел 118 памяти команд, мультиплексор 119, сумматор 120, узел 121 сравнения, сумматор 122, мультиплексор 123, стековый регистр 124, мультиплек сор 125, узлы 126-129 оперативной памяти, коммутатор 130, регистры 131- 138, коммутаторы 139 и 140, мультиплексор 141 и регистр 142.

Устройство реализует расчет параметров вспомогательных грубых сеток, используемых для органи- ции итераций многосеточного типа по алгоритму;

136422

V,s)tA;f.. ji (1)

;, )

V),.,),,.,) 3

где

10

15

. fiJ(x4,r ()

i,j 1,2, , ,2, ...,L, -(.,)(U,-,.,)ts)U(,.)-t,.,-t,

Ut )t,) ...its.

,1,22 -1,

U,

(4)

(f)

5

0

5

0

5

представляющему собой некоторую модификацию прямого хода метода циклической редукции. Дпя исключения неизвестных порядок , приводится к ВИДУ (6), соответствующему упорядочению узлов в шахматном порядке на белые

KT(K;S-I) черные CVjlcx-isH Упрощение (4) обеспечивает постоянство

структуры ненулевых элементов в матрице А(зр. по сравнению с результатом предыдущей редукции. С учетом возможных комбинацией исключения черных или белых узлов s-крат- ная редук115-1я исходной системы уравнений порождает 2 различных вариантов образования комплекта вспомогательных грубых сеток. Поэтому для управления вычислениями, идентификации и однозначного определения варианта образования уравнения (6) служит индексное выражение (5). На фиг.5 трехкратная редукция двухмерной сеточной области А(ф)А(А порож- дает вспомогательные грубые сетки

А(г;,) А(„, A(((i) при этом текущая редукгсия уменьшает число узлов приблизительно в два раза и меняет ориентацию главных связей ) :j Csl диагональных связей (d,f)(5), (d ,)(-5j на 45 по сравнению с результатом предыдущей редук1 1И, Эта особенность учитывается при организации хранения и поиска данных в памяти устройства при построении грубых сеток о Для двух массивов (dp(s)j (d v)(sl редук1:;ии необходимо вьщелить дополнительное поле памяти, при этом для запоминания величин а(5 Ъ,, ( y(z)i используют ячейки памяти массивов предыдущей редуктрта afj.)), b(s.,) , (dx)(s-f)s (d ) (5.,j соответственно, Конечньй результат в этих ячейках памяти будет сформирован после исключения всех смежных черных (белых) узлов в дан- ой редукции. При такой организации хранения данных в предельном случае редукции () необходимо 0(8N) ячеек памяти,

Перед началом работы в узлы 97 и 118 памяти команд записывается управляющая информация, в зависимости от режима работы устройства, В регистр 5 записывается код номера текущей редукции 3, в регистр 6 - код адреса i,j-ro узла сеточной области, в регистр 7 - код адреса узлов граничных строк и столбцов сеточной области, а в регистр 142 - код конечного адреса занятых ячеек узлов 126, 127, 128 и 129 оперативной памяти. Все остальш.1е регистры устройства устанавливаются в исходное состояние.

Выбирается режим записи данных исходной задачи в узлы 103,104 и в узлы 126-129 оперативной памяти.

По нулевому адресу, поступающему с выхода регистра 6 через мультиплексор 98, сумматор 100 и мультиплексор 101 на входы узлов 103 и и 104 оперативной памяти, в их нулевые ячейки записывается нулевая информация, поступающая на их другие входы с шины 42 данных через информационные входы мультиплексора 105, По нулевому адресу, поступакядему с выхода регистра 6 через мультиплексор 119,сумматор 120,сумматор 122 и мультиплексор 125 на первые входы узло 126-129 памяти, в их нулевые ячейки записывается нулевая информация, поступающая на их вторые входы с шины 42 данных через информационные входы мультиплексора 130, Затем на первый вход узла 97 памяти команд поступает код режима записи массива параметров а и с его четвертого выхода на вход

5

0

5

0

5

0

5

0

5

узла 103 оперативной памяти поступает сигнал записи. По содержимому регистра 6 выбирается первая ячейка и в нее с шины 42 данных по тактовому сигналу записывается информация, Содержимое регистра 6 наращивается на единицу, выбирается вторая ячейка записывается следующая информация и процесс записи массива параметров в узел 103 оперативной памяти продол- . жается до полной загрузки массива параметров а. Затем сигнал записи .поступает на вход узла 104 оперативной памяти, в который записывается массив параметров Ь, После окончания записи массивов параметров а,Ь в узлы 103 и 104, на вход узла 118 памяти команд поступает код записи массивов параметров а, а, d и узлы 126-129 оперативной памяти соответственно. Массивы параметров записываются, как было описано выше. После ввода в узлы 103,104 и 126-129 оперативной памяти массивов параметров а, Ь, а(, а,, и d устройство готово выполнять алгоритм первой редукн и исходной сеточной области.

Рассмотрим вариант редукции, ког- да при и исключаются черные узлы. Примем индекса1 ;ию ( для нечетной и четной кратности редукций 3 вместо аг.), Направление обхода исключаемых узлов сеточной области - слева направо, сверху вниз. В каждом машинном такте устройство рассчитывает все параметры, возникающие в результате- исключения (i,j)-ro узла. Работу при и рассмотрим в два этапа: этап чтения параметров из узлов оперативной памяти и расчета параметров и этап записи результатов в узел оперативной памяти.

В регистр 4 записывается код кон7 станты адреса соседних узлов. Устанавливается в пятом регистре 5 и режим параллельного чтения информации из узлов 103, 104 и 126-129 оперативной памяти. По тактовому сигналу с выхода регистра 6 на первые входы мультиплексоров 98 и 119 блоков 1 и 2 управления соответственно поступает код адреса i,j-й узловой точки сеточной области, С выхода муль типлексора 98 код адреса А ( поступает на первый вход сумматора 100, на втором входе которого действует

5

нулевой код константы адреса соседн узлов. С выхода сумматора 100 сумманый код адреса поступает на первый вход мультиплексора 101 и на первый вход узла 102 сравнения, на втором входе которого действует код адреса узлов -граничных столбцов и строк с выхода регистра 7, Результат сравнения (где i , j jf - код адреса граничных строки и столбца) поступает на вход управле

раметр (Ь ,)cs-i; , s регистр 134 - параметр ( )c.i), в регистр 138- параметр (d у M(g.,). К содержимому регистра 4 добавляют единицу и на вторые входы сумматоров 100 и 120 поступают коды констант адресов соседних

- ti-i- . vti , / .у tt . у о i i::ijn.t-1JJ I |

параметр ( )(s-t в регистр 132 параметр (. ,)(s-(), в регистр 136 имя мультиплексора 101. Если А 0, то с выхода второго мультиплексора

101 суммарньй код адреса А(; :) пос узлов (С,О) и (О,- С) и по следующим тупает на входы узлов 103 и 104 памя- адресам записы вают в регистр 108 ти. Если А О, то на входы узлов параметр ( )(9-il , в регистр 113- 103 и 104 поступает нулевой адрес С выхода мультиплексора 119 код адреса

А ({J ) поступает на первьй вход сумма-20 параметр (d , (s-i) s регистр 137 - тора 120, на втором входе которого параметр (d ) (j-i) - Затем вновь к действует код константы адреса сосед- . содержимому четвертого регистра 4 до- них узлов. С выхода сумматора 120 бавляют единицу, выбирают код констан- суммарный код адреса поступает на пер- ты (-С,0) и (С,О) и в регистр 116 за- вый вход сумматора 122 и на первый 25 писывают параметр ( )(s-i) Р

гистр 115 - параметр (. ).{s-i) в регистр 135 - параметр (d )(s.,)

По первому системному такту в рабочий момент t код адреса i,j-ro узла 30 сеточной области записывается в стековые регистры 99 и 124. С узла 118 памяти команд на управляющие входы коммутаторов 139 и 140 поступает сигнал, подключая информационные входы мульвход узла 121 сравнения, на втором входе которого действует код адреса узлов граничных столбцов и строк с выхода регистра 7. Результат сравнения поступает на вход упрартения мультиплексора 125. На второй вход сумматора 122 поступает нулевая константа с выхода.мультиплексора 123. С выхода сумматора 122 код адреса .

через восьмой мультиплексор 125 поступает на входы узлов 126-129,

С выхода узла 97 памяти команд на входы регистров 106 и 111 и с выхода узла 118 памяти команд на входы регистров 131 и 133 поступает сигнал разрешения записи По тактовому сигналу из выбранных по адресу А (i ,j) ячеек узлов 103, 104 и 126-129 записывают в регистр 10.6 параметр, .(а ) (S-1) в регистр 111 - параметр (Ь , ) (s-f) , в регистр 131 - параметр (ay)(s-i) в регистр 133 параметр (а ) (д-и Содержимое регистра 4 увеличивается на единицу. С выходов узлов 97 и 118

35

типлексора 139 к его-выходу и инфор40

мадаонные входы коммутатора 140 к его выходу.

По сигналу считывания содержимое регистров 106-108, 110-113 и 115 поступает по шине 43 данных на входы регистра 3, содержимое регистров 131- 138 через коммутаторы 139 и 140 по шине 43 данных поступает на входы регистра 3. По первому тактовому сигна., лу информатдаю, поступившую по шине 43 данных, записывают в регистр 3. Кроме того, информадая по шине 43 данных поступает в сумматор 15. По второму системному такту содержимое регистра 3 переписывают в регистр 8. Суммарньй код с выхода сумматора 15 поступает на первые входы делителей 37-40 .|На вторые входы которых поступает информату я с регистра 3. С выхода делителя 37 результат деления поспамяти команд на вторые входы Сумматоров 100 и 120 соответственно поступают коды констант ал,ресов соседних узлов (О.с) и (-0,0), которые суммируются в сумматорах с кодом адреса i,j-ro узла. По суммарньм кодам адресов с выходов сумматора 100 и сумматора 120 выбирают очередные ячейки узлов 103 и 104 оперативной памяти узлов 127 и 9 оперативной памяти как было описано выше. При поступлении сигнала записи на входы регистров 107, 112, 134 и 138 по тактовому сигналу из выбранньи ячеек 103, 104, 127 и 129 оперативной памяти записывают в регистр 107 параметр (а . )(5-,;в регистр 112 - паП а КХО T TI1Г 1/0.1т -г f -r Trf-i т-п1 3/1

раметр (Ь ,)cs-i; , s регистр 134 - параметр ( )c.i), в регистр 138- параметр (d у M(g.,). К содержимому регистра 4 добавляют единицу и на вторые входы сумматоров 100 и 120 поступают коды констант адресов соседних

узлов (С,О) и (О,- С) и по следующим адресам записы вают в регистр 108 параметр ( )(9-il , в регистр 113-

- ti-i- . vti , / .у tt . у о i i::ijn.t-1JJ I |

параметр ( )(s-t в регистр 132 параметр (. ,)(s-(), в регистр 136 узлов (С,О) и (О,- С) и по следующим адресам записы вают в регистр 108 параметр ( )(9-il , в регистр 113-

параметр (d , (s-i) s регистр 137 - параметр (d ) (j-i) - Затем вновь к содержимому четвертого регистра 4 до- бавляют единицу, выбирают код констан ты (-С,0) и (С,О) и в регистр 116 за- писывают параметр ( )(s-i) Р

типлексора 139 к его-выходу и инфор

мадаонные входы коммутатора 140 к его выходу.

По сигналу считывания содержимое регистров 106-108, 110-113 и 115 поступает по шине 43 данных на входы регистра 3, содержимое регистров 131- 138 через коммутаторы 139 и 140 по шине 43 данных поступает на входы регистра 3. По первому тактовому сигналу информатдаю, поступившую по шине 43 данных, записывают в регистр 3. Кроме того, информадая по шине 43 данных поступает в сумматор 15. По второму системному такту содержимое регистра 3 переписывают в регистр 8. Суммарньй код с выхода сумматора 15 поступает на первые входы делителей 37-40 .|На вторые входы которых поступает информату я с регистра 3. С выхода делителя 37 результат деления поступает на первые входы умножителей 28-31. С выхода делителя 38 результат деления поступает на первые входы умножителей 32-35, С выхода делителя 39

71А1

результат деления поступает на первые входы умножителей 23-25. С выхода делителя 40 результат деления поступает на первые входы умножителей 26,27 и 36 о С выходов регистра 8 информату я поступает с первого выхода на второй вход умножителя 30 с второго выхода на вторые входы умножителей 32 и 31, с третьего выхода на второй вход умно жителя 38, с четвертого выхода на вторые входы умножителей 23 и 25, с пятого выхода на вход умножителей 25, 27,30 и 34 с девятого выхода на вторы входы умножителей 24,26,29 и 33.

По третьему системному такту содержимое регистра 4 увеличивается на еди яйцу, выбирается код константы (0,С) и в регистр 109 записывается параметр (а )(s-f), в регистр 114 - параметр (Ь )(5-0 и с выходов регистров 109 и 114 информация шины 44 данных поступает на первые входы сумматоров 12 и 13 соответственно, С выходов регистра 8- информация записывается в :регистр 9. Информация с выходов регистра 9 поступает на первые входы соответственно сумматоров 19, 22,18,,21, 17,20 и 16. Информа1щя с выходов тре- тьего регистра 9 поступает по шине 43 данных на вторые входы мультиплексо- .ров 116,117 и 141 и с их выходов по шине 44 данных на первые входы сумматоров 14,13 и 10 соответственно. На вторые входы сумматоров 10-22 поступа ет информадая с выходов умножителей .23-27, 36,28, 29, 30, 32-34 соответственно. Сформированные на вьгход ях сумматоров 10-14, 16-22 и на выходах умножителей 31 и 35 параметры текущей укрупненной сеточной области нечетной редукции по шине 45 данных поступают на соответствующие входы коммутаторов 105 и 130,

Затем производят запись результа- тов расчета в блоки 1 и 2, По шине 41 управления код режима поступает на первые .входы узлов 97 и 118 памяти команд, на вторые входы которых с выхода регистра 4 поступает код константы (о,-С). По сигналу с первых выходов узлов 97 и 118 мультиплексоры 98 и 119 подключают выходы стеков

99и 124 к первым входам сумматоров

100и 120 соответственно, на вторые входы которых с вторых выходов узлов 97 и 118 поступает код константы

(о,-С), где суммируются с кодом адреса i,j-ro узла, Лалее форг-гирование

5 о Q

с

8

кодов адреса узлов ЮЗ 104, 126-129 оперативной памяти осуществляется, как бьшо описано выше. По сигналу с третьих выходов первого и второго узлов 97 и 118 памяти команд мультиплексоры 105 и 130 выбирают источники информации с шины 45 данных. По выбранному адресу в узлы 103 и 104 оперативной памяти через мультиплексор 105 с шины 45 данных записывают-, ся параметры ( ) (ji и (b )(s) соответственно, в узлы 128 и 129

оперативной памяти через мультиплек;. t-c

5

0

(5)

5

Сор 130 - параметры (a j. ) ( (51 содержимому регистра 4 добавляется единица и формируется код адреса с константой (С,О). По этому адресу записываются параметры в узел 103 оперативной памяти ( ) CS) , в узел 104 оперативной памяти (Ь ) (S1 ив узел 126 оперативной памяти ( ) (s) В регистр 4 добавляется единица и формируется код адреса с константой (-С,0), по которому записываются параметры в узел 103 оперативной памяти (а ), в узел 104 оперативной памяти ( )(sl и в узел 127 оперативной памяти (а ) . Затем формируется код адреса с константой (О,С) и в узел 103 оперативной памяти записывается параметр (a )(si в узел 104 оперативной памяти - параметр ( )(si При формировании кода адреса узлов 126 и 127 оперативной памяти для записи массива параметров d и d ,, по сигналу с шестого выхода узла 118 памяти команд через мультиплексор 123 с выхода регистра 142 код адреса конечной занятой ячейки узлов 126 и 127 оперативной памяти поступает на второй вход сумматора 122, на первом входе которого действует суммарный код адреса i,j-ro узла и код константы (0,-С). С выхода сумматора 122 код адреса поступает на первый вход узла 126 оперативной памяти, в него записывается параметр V (S) Содержимое регистра 4 увеличивается на единицу, и, как было описано, формируется код адреса с константой (-С,0), поступающий на первый вход узла 127 оперативной памяти, в него записывается параметр

(d4 )(sb

После завершения нечетной редукции в узлах 103 и 104 оперативной памяти хранятся массивы а дл) b(5- iocновной н и , ,, вспомогательной сеток, в узлах 126 и 127 оперативной памяти - массивы (а) (j.,, и (а у) (s-tj основной и (d)jjH (dy)s) вспомогательной сеток, в узлах 128 и 129 one- ративной памяти - массивы (d;t-)(j,,,H (d()fs-i) основной и ( ах)(з)И (ay)(s) вспомогательной сеток,

В режиме четной редук щи формиро- вание кодов адреса ячеек узлов 103 и 104 оперативной памяти в режиме записи массива параметров а и b совпа дает с формированием кодов адреса в режиме нечетной редукции, отличаются только коды констант, считываемь е с второго выхода узла 97 паьмти команд., С выхода регистра 5 на входы управления мультиплексоров 116 и 117 поступает сигнал, по которому выходы ре-.- гистров 110 и 115 подключают к шине 144 данных. При формировании кодов адреса ячеек у злов. 126-129 оперативной памяти по сигналу с шестого выхода узла 118 памяти команд, 105 содержимое регистра 142 через мультиплексор 123 поступает на вход сумматора 122 и далее. По сил налу с пятого выхода узла 118 памяти команд информационные входы коммута1 ора 139 .подключаются к шине 43 данных л ршформационные входы

.коммутатора 140 - к первому информационному входу мультиплексора 141 к шине 43 данньпсс Затем осу1дествляется запись информации четной редукции в регистры 115, 131-138,По сигналу с выхода регистра 4 на вторых выходах уз лов 97 и 118 памяти команд-формируется код константы (0,0), По сформированно му коду адреса с выхода узла 103 опе;ративной памяти в регистр 106 записывается параметр (a j)(s.ijj с выхода узла 104 оперативной памяти в регистр 111 - параметр (b - )(s.,t, с выхода узла 128 оперативной памяти регистр 115 параметр (а 0{s-5) с выхода узла 129 оперативной памяти в регистр 137 - параметр (a,j ) jg,.. Содержимое регистра 4 увеличивается на единицу, выбирается код константы (-С,С) и (С,-С) и по сформированному адресу с выходов уз- - лов 103 и 104 оперативной памяти, в

регистры 107 и 112 записываются параметры (а - )(.5.,5И ()(SM) соответственно, а с выхода узла 128 оперативной памяти Б регистр 136 записывает- - ся параметр ( ) (.), В регистр 4 добавляется единица, выбирается код константы (СрС) и (-С,-о/ и по сфорQ0 5

-

0

0

мированному адресу с выходов узлов 103 и- 104 оперативной памяти в регистры, 108 и 113 записываются параметры (a )j.,jH ( )(5,j соответственно, с выхода узла 129 оперативной памяти в регистр 138 - параметр (s-i; Содержимое регистра 4 увеличивается на единицу. При формировании кода адреса код конечного адреса с выхода регистра 142 через мультиплексор 123 поступает на второй вход.сумматора 122, По сформированному адресу и коду константы (-С, С) с выхода узла 127 оперативной памяти в регистр 133 записывается параметр (d )5.t) « Содержимое регистра 4 увеличивается на единицу, выбирается константа (С,-С) и с выхода узла 126 оперативной памяти в регистр 131 записывается параметр ( )(s) Увеличивается содержимое регистра 4 на единицу и по константе (-С,-С) с выхода узла 126 оперативной памяти в регистр 132 записывается параметр ( ()

По первому системному такту с выходов регистров информация по одним каналам шины 43 данных поступает на соответствующие входы регистра 3,а по другим каналам шины 43 - на входы сумматора 15. По второму системному такту информация с выходов регистра 3 записывается в регистр 8 и осуществляется операция деления в делителях 37-40 задержанной на один такт входной информагщи с каналов шины 43 данных на суммарный код с выхода сумматора 15, По третьему системному такту информаид я с выходов регистра 8 записывается в регистр 9 и осуществляется операция умножения информации с выхода регистра 8, задержанной на два такта относительно информации в каналах шины 43 данных, на код с выходов делителей 37-40. Результат умножения с выходов умножителей 28-30, 32-34, 23-25, 36, 26 и 27 поступает на вторые входы сумматоров 17-22, 10-12, 16,13 и 14. С выходов регистра 9 информация, задержанная на три такта отиоснтельно информапд и в каналах шины 43 , поступает на первые входы сумматоров 19,22,18,21,17 и 20 и 16. По базовому адресу, хранящемуся стеках 99 и 124, формиру ют код адреса узлов 103 и 104 оперативной памяти с кодом константы (С,-С). По этому адресу с вьгхоля узлов 103 и

111413642

104 оперативной памяти в регистры 109 данных в узел и 114 записываются параметры 1 ( )(5.„ и ()f,., соответственно. Увеличивается содержимое г регистра 4 на единицу, ..формируется код адреса с кодом константы (С,-С) И с выходов узлов 103 и 104 оперативной памяти в регистры 110 и 115 за12

писывакугся параметры (а ) (-О Ю и (Ь )($.j соответственно и с - выхода узла 127 оперативнсэй памяти в регистр 134 - параметр (d у )(.,). Информация с вькодов регистров 109- 11), 115 и 134 поступает на первые ts входы сумматоров 12.14,11,13 и 10 соответственно. По четвертому системно- му такту на выходах сумматоров 17-22, 10-12, 15, 13 и 14 и на выходах умно03 оператниной памяти записывается параметр () (si в узел 104 оперативной памяти - пара метр () (51 и в узел 127 оперативной памяти - параметр ( )(jj Содержимое регистра 4 увеличивается на единицу и формируется код адреса с константамт (С,-С) и (-С,-С), По сформированному коду адреса с тины 45 данных в узел 103 оперативной памяти- записывается параметр () (j) , в узел 104 оперативной памяти - параметр ( )(jj , в узел 126 оперативной памяти - параметр () Cyi в узел 127,оперативной памяти - параметр

(а% ) fci ив узел 129 оперативной памяти - параметр (fl y )(s) Содержимое регистра 4 увеличивается жителей 31 и 35 формируются параметры20 на единицу, выбирается код константы

укрупненной сеточной области четной редукции, которые поступают на соответствующие входы мультиплексоров 105 и 130.

Запись результатов четной редуктщи 25 в узлы 103, 104, 126-129 памяти осуществляется по базовому адресу i,j,

(-С,-С) и по сформированному коду адреса с 45 шины данных в узел 103 оперативной памяти записывается параметр (а - ) (s в узел 104 оперативной памяти - параметр ( )($) По окончании записи результатов четной редукции в узлы 103, 104, 126-129 памяти содержимое регистра 5 увеличивается на единицу и устройство рабохранящемуся в стековых регистрах 99 ,и 124, по четвертому тактовому сигналу. Массивы параметров а и b записы- 30тает как было описано, вьтолняя оче- ваются по адресам основных массивовредную редукцию. После вьтолнения за- занятых ячеек памяти, а параметры а ,данного числа редукций в узлах 103, а, d, dy записываются по адресам,104, 126-129 памяти хранятся парамет35

сдвинутым на величину N основного массива занятых ячеек памяти

При формировании кодов адреса узлов 126-129 оперативной памяти с выхода регистра 142 через мультиплексор 123 на второй вход сумматора 122 поступает код константы, равный вели-до чине основного массива занятых ячеек памяти.

По сигналу из регистра 4 на вторые выходы узлов 97 и 118 памяти команд поступают коды констант (-С,С) и 45 (С,-с) соответственно, по которым формируется код адреса узлов 103, 104, 126 и 128 оперативной памяти,

По сигналу записи с шины 45 данных в узел 103 оперативной памяти записы- п

(9)

В узел

вается параметр (а J )

104 оперативной памяти - параметр

( ) (5) в узел 126 оперативной

памяти - параметр

,

. J-C)

(51

И Б

ры груоьк сеток для организации итерационного процесса многосеточного типа реализуемого на R-сетках или для решения задачи теории поля на других устройствах вычислительной системы.

Формула изобретения

Устройство для вычисления параметров сеток для решения разностных уравнений, содержащее первьй и второй блоки управления, первьй регистр, с первого по пятый сумматоры и с пер-, вого по пятьпЧ умножители, причем информационный вход параметров исходной сетки устройства подключен к первым входам задания режима первого и второго блоков управления, с первого . по четвертый выходы первого блока управления и первый выход второго бло- ка управления подключены соответственно к первым входам сумматоров с первого по пятый, выходы которых подключены соответственно к второму входу задания режима второго блока упузел 128 оперативной памяти - параметр ( ) (51 Содержимое регистра 4 увеличивается на единицу, выбирается код константы (С,С) и (-С,С) и по сформировантюму коду адреса с ишны 45

12

данных в узел

03 оператниной памяти записывается параметр () (si в узел 104 оперативной памяти - пара метр () (51 и в узел 127 оперативной памяти - параметр ( )(jj Содержимое регистра 4 увеличивается на единицу и формируется код адреса с константамт (С,-С) и (-С,-С), По сформированному коду адреса с тины 45 данных в узел 103 оперативной памяти- записывается параметр () (j) , в узел 104 оперативной памяти - параметр ( )(jj , в узел 126 оперативной памяти - параметр () Cyi в узел 127,оперативной памяти - параметр

(а% ) fci ив узел 129 опе(-С,-С) и по сформированному коду адреса с 45 шины данных в узел 103 оперативной памяти записывается параметр (а - ) (s в узел 104 оперативной памяти - параметр ( )($) По окончании записи результатов четной редукции в узлы 103, 104, 126-129 памяти содержимое регистра 5 увеличивается на единицу и устройство работает как было описано, вьтолняя оче- редную редукцию. После вьтолнения за- данного числа редукций в узлах 103, 104, 126-129 памяти хранятся парамет35

до 45

п

р

ры груоьк сеток для организации итерационного процесса многосеточного типа реализуемого на R-сетках или для решения задачи теории поля на других устройствах вычислительной системы.

Формула изобретения

Устройство для вычисления параметров сеток для решения разностных уравнений, содержащее первьй и второй блоки управления, первьй регистр, с первого по пятый сумматоры и с пер-, вого по пятьпЧ умножители, причем информационный вход параметров исходной сетки устройства подключен к первым входам задания режима первого и второго блоков управления, с первого . по четвертый выходы первого блока управления и первый выход второго бло- ка управления подключены соответственно к первым входам сумматоров с первого по пятый, выходы которых подключены соответственно к второму входу задания режима второго блока уп13

равления, второму входу задания режима первого блока управления, третьему входу задания,режима первого блока управления, четвертому входу задания режима первого блока управления и пятому входу задания режима первого блока управления, второй, третий, четвертый и пятый выходы второго блока управления и пятый выход первого блока управления подключены соответственно к первому - пятому информаи ионным входам первого регистра, выходы с первого по пятый умножителей подключены соответственно к вторым входам с первого по пятый сумматоров, отличаю одееся тем, что, с 11,елью повышения быстродействия, Б него введены с второго по седьмой регистры, с шестого по тринадцатый сумматоры, с шестого по четырнадцатый умножители и с первого по четвертый делители, причем инфор- мационньй вход параметров исходной сетки устройства подключен к информационным входам с второго по пятьш .регистров, управляющий вход устройства подключен к первым входам режима первого и второго блоков управления и входам записи - считьшания регистров с второго по пятьм, выход второго.ре- гистра подключен к, вторым входам режима первого и второго блоков управления, выход третьего регистра подключен к третьим входам первого и второго блоков управления, выход четвертого регистра подключен к четвертым входам режима первого и второго блоков управления5 выход пятого регистра подключен к пятому входу режима второго блока управления, с шестого по двенадцатьш выходы первого блока управления и с шестого по девятый выходы второго блока упр.з.вле- ПИЯ подключены соответственно к шестому - шестнадцатому информационным входам первого регистра, с первого по четвертый вьгходы которого подключены соответственно к первому - четвертому информационным входам шестого регистра и соответственно к первым входам с первого по четвертый делиелей, с второго по пятый выходы втоого блока управления и пятый выход ервого блока управления подключены оответственно к первому- пятому ходам шестого сумматора, информаионный выход которого подключен к торым вход.ам с первогс ло четвертый

еояо - аеа- - м

Ш

(5

20

25

41364214

делителей, с пятого по шестнадцатый выходы первого регистра подключены соответственно к пятому - шестнадцатому информационньм входам шестого регистра, с первого по десятый выходы которого подключены соответственно к первому - десятому информационным входам седьмого регистра, первый, второй и третий вьтходы которого подключены соответственно к пятому входу режима, шестому входу режима первого, блока управления и шестому входу режима второго блока управления, выход первого делителя подключен к первым входам с шестого по девятый умножителей,, выход второго делителя подключен к первым входам с десятого по тринадцатьй умножителей, выход третьего делителя подключен к первым входам с первого по третий умножителей., выход четвертого делителя подключен к первым входам четвертого, пятого и четырнадцатого умножителей, выход четьфнадцатого умножителя подключен к первому входу седьмого сумматора, выход которого подключен к третьему информационному входу второго блока управления, одиннадцатый выход шестогб регистра подключен к второму входу четырнадцатого умножителя, двенадца тый выход шестого регистра подключен к; вторым входам девятого и десятого

умножителей, тринадцатьй выход шестого регистра подключен к второму входу шестого умножителя, четырнадцатьй выход шестого регистра подключен к вторым входам первого и тринадцатого умножителей, пятнадцатьй выход шестого регистра подключен к вторым входам, восьмого, двенадцатого, третьего и пятого умножителей, шестнадцатьй выход шестого регистра подключен к вторым входам седьмого, одиннадцатого, второго и четвертого умножителей, выходы шестого, седьмого, восьмого, десятого, одиннадцатого,и двенадцатого умножителей подключены соответственно к первым входам сумматоров, с восьмого по тринадцатьв, четвертьй выход седьмого регистра подключен к второму входу десятого сумматора, пятый выход седьмого регистра подключен к второму входу тринадцатого сумматора, шестой выход седьмого регистра подключен к второму входу девятого сумматора, седьмой выход седьмого регистра подключен к второму входу двенадцатого сумматора, восьмой выход

30

35

40

45

50

55

15

седьмого регистра подключен к второму входу восьмого сумматора, девятый выход седьмого регистра подключен к второму входу одиннадцатого сумматора, десятый выход седьмого регистра подключен к второму входу седьмого сумматора, выходы с восьмого по тринадцатый сумматоров, девятого и тринадцатого умножителей подключены соот ветственно к четвертому информацион

управления

216

ному входу второго блока управлетш, шестому и седьмому входам задания режима первого блока управления, пятому входу задания режима второго блока управления, босьмому и девятому входам задания режима первого блока управления, шестому и седьмому входам задания режима второго блока

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для решения уравнений математической физики | 1986 |

|

SU1363260A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для расчета параметров множества грубых сеток в отношении к исходной сетке при решении уравнений математической физики. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит первый и второй блоки управления, с первого по седьмой регистры с первого по тринадцатый сумматоры, с первого по четьфнадцатый умножители, с первого по четвертый делители. 6 ил. i О)

Фиг. f

Ч

Фиг. 2

4

4J «

Фиг.

entfei-(S-i/l) .ц,ина т - атаю шит.

iDui.S

фа.

Редактор Л. Пчолинская

Составитель В. Смирнов

Техред Л.Олийнык Корректор М. Пожо

Заказ 3787/52

Тираж 704

ВПИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

ay

d

Фаг. 6

Подписное

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1980 |

|

SU926667A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Романцов В.П | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-07-30—Публикация

1986-09-11—Подача