Изобретение относится к вычислительной технике и может быть исполь зовано в системах для решения дифференциальных уравнений в частных производных итерационным методом.

Целью изобретения является повышение быстродействия устройства за счет снижения затрат времели на повторное формирование массива исходных данных при повторных решениях со сдвигом моделируемой сеточной области.

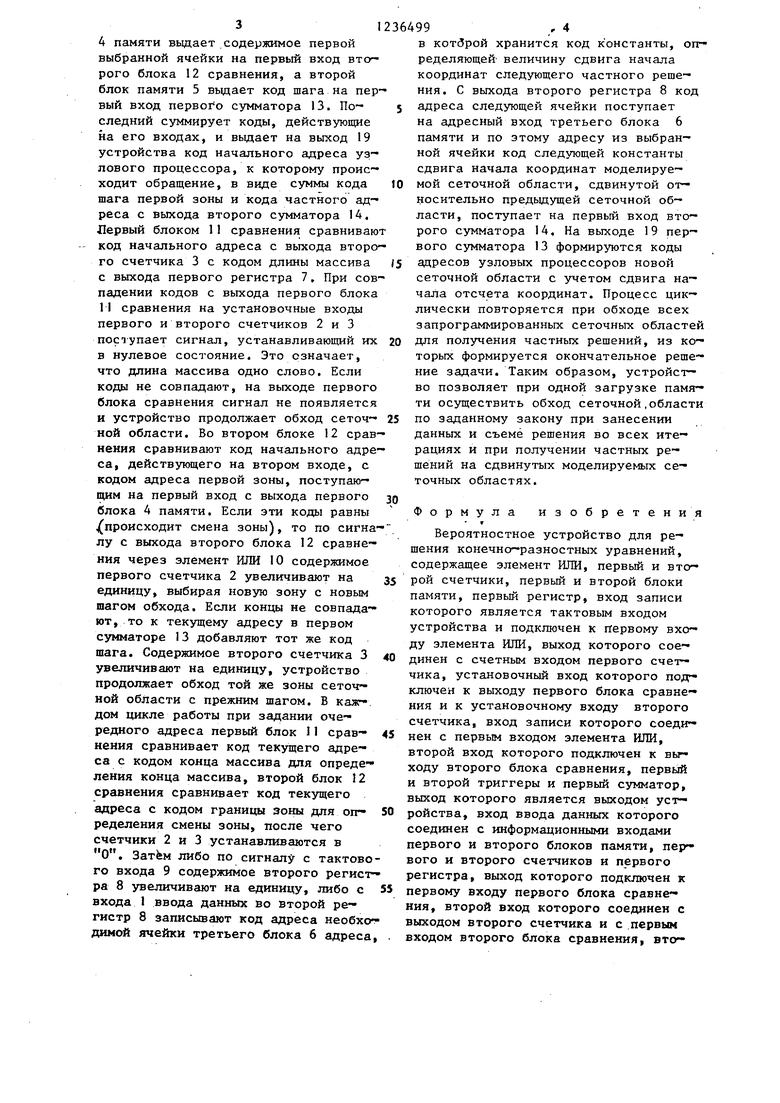

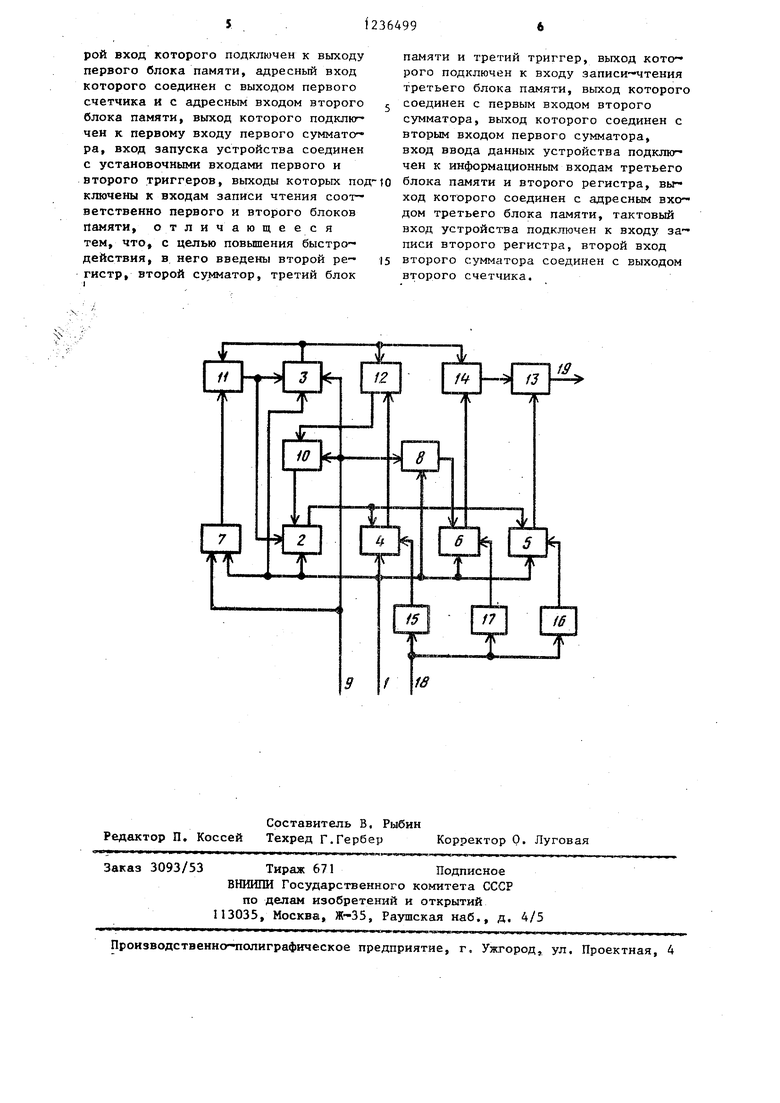

На чертеже изображена схема устройства.

Устройство содержит вход 1 ввода данных, первый счетчик 2, второй счетчик 3, первый 4, второй 5, третий 6 блоки памяти, первый 7 и второй 8 регистры, тактовый вход 9 уст ройства, элемент ИЛИ 10, первый II, второй 12 блоки сравнения, первый 13 второй 14 сумматоры, первый 15, второй 16, третий 17 триггеры, вход 18 запуска устройства, выход 19 устройства.

Устройство работает следующим образом.

По сигналу записи, поступающего с тактового входа 9 на вход записи первого регистра 7, код длины массива с входа 1 ввода данных записьшают в первый регистр 7. С входа 18 запуска на входы первого 15, второго 16 и третьего 17 триггеров поступает сигнал, устанавливающий первый триггер 15 и соответственно первый блок 4 памяти в режим записи, а второй 16, третий 17 триггеры и второй 5s, третий 6 блоки памяти в режим чте ния. По нулевому адресу, поступгающе- му с выхода первого счетчика 2 на адресный вход первого блока памяти А, в него записьтают с входа 1 ввода данных адрес первой зоны. Затем по счетному входу с тактового входа 9 через схему ИЛИ 10 содержимое первого счетчика 2 увеличивают на единицу и выбирают следующую ячейку первого блока 4 памяти. В выбранную ячейку записывают адрес следующей зоны и процесс повторяется до полной записи адресов всех зон сеточной модели. После записи адресов зон в первый блок 4 памяти первый счетчик 2 устанавливают в нулевое состояние первый триггер 15 в режим чтения, а второй триггер 16 - в режим записи,и осуществляют запись информации во

364992

второй блок 5 памяти. По нулевому адресу, поступающему с выхода перво- го счетчика 2, на адресный вход второго блока памяти 5 с входа 1 ввода

5 данных в выбранную ячейку второго блока памяти 5 записывают код щага обхода первой зоны. Затем содержимое первого счетчика 2 увеличивают на единицу и в следующую ячейку второго

to блока 5 памяти записывают код шага следующей зоны. Процесс циклически повторяется до полной загрузки второго блока 5 памяти. Затем второй триггер 16 устанавливают в режим ния, первый счетчик 2 и второй регистр 8 в нулевое состояние, а третий триггер 17 и соответственно третий е)лок 6 памяти - в режим записи. . По нулевому адресу, поступающему с

20 выхода второго регистра 8 на адресный вход третьего блока 6 памяти, с входа 1 ввода данных записьшают в выбр 1нную ячейку памяти третьего блока 6 памяти код первой константы

25 сдвига адресов начальных точек отсче та координат моделируемой области узловых процессоров. Затем содержи-- мое второго регистра увеличивают на единицу и с входа I ввода данных в

30 очередную выбранную ячейку третьего блока 6 памяти записывают ко следуку щей константы. Процесс циклически - повторяется до полной загрузки всех кодов констант в ячейки третьего бло

JJ ка 6 памяти. Затем третий триггер 17 устанавливают в режим чтения, а второй триггер 8- в нулевое состояние, после чего устройство настроено и готово к: обходу сеточной области.

40 По входу записи второго счетчика 3 записьтают код начального адреса. С выхода второго счетчика 3 код начального адреса поступает на вторые входы первого 11, второго 12 блоков

45 сравнения и второго сумматора 14, По коду начального адреса с выхода второго регистра 8 код первой константы из первой ячейки третьего бло ка 6 памяти поступает на первый вход

50 второго сумматора 14, на выходе которого формируется код частного адреса первого узлового процессора: первой сеточной области, поступающий на второй вход первого сумматора 13.

55 С выхода первого счетчика 2 код нулевого адреса поступает на адресные входы первого 4 и второго 5 блоков памяти. По этому адресу первый блок

4 памяти вьщает содержимое первой выбранной ячейки на первый вход вто рого блока 12 сравнения, а второй блок памяти 5 вьщает код шага на первый вход первого сумматора 13. По- следний суммирует коды, действующие на его входах, и вьщает на выход 19 устройства код начального адреса узлового процессора, к которому происходит обращение, в виде суммы кода шага первой зоны и кода частного адреса с выхода второго сумматора 14. Лервый блоком 11 сравнения сравнивают код начального адреса с выхода второго счетчика 3 с кодом длины массива с выхода первого регистра 7, При совпадении кодов с выхода первого блока 11 сравнения на установочные входы первого и второго счетчиков 2 и 3 поступает сигнал, устанавливающий их в нулевое состояние. Это означает, что длина массива одно слово. Если коды не совпадают, на выходе первого блока сравнения сигнал не появляется и устройство продолжает обход сеточ- ной области. Во втором блоке 12 сравнения сравнивают код начального адреса, действующего на втором входе, с кодом адреса первой зоны, поступающим на первый вход с выхода первого блока 4 памяти. Если эти коды равны происходит смена зоны), то по сигналу с выхода второго блока 12 сравнения через элемент ИЛИ 10 содержимое первого счетчика 2 увеличивают на единицу, выбирая новую зону с новым шагом обхода. Если концы не совпадают, то к текущему адресу в первом сумматоре 13 добавляют тот же код шага. Содержимое второго счетчика 3 увеличивают на единицу, устройство продолжает обход той же зоны сеточной области с прежним шагом. В каждом цикле работы при задании очередного адреса первый блок 11 срав- нения сравнивает код текущего адреса с кодом конца массива для опреде- ления конца массива, второй блок 52 сравнения сравнивает код текущего адреса с кодом границы зоны для оп ределения смены зоны, после чего счетчики 2 и 3 устанавливаются в

О . Затем либо по сигналу с тактового входа 9 содержимое второго регист ра 8 увеличивают на единицу, либо с входа 1 ввода данных во второй регистр 8 записывают код адреса необхог- ДИМОЙ ячейки третьего блока 6 адреса,

в котЗрой хранится код к онстанты, определяющей- величину сдвига начала координат следующего частного решения. С выхода второго регистра 8 код адреса следующей ячейки поступает на адресный вход третьего блока 6 памяти и по этому адресу из выбранной ячейки код следующей константы сдвига начала координат моделируемой сеточной области, сдвинутой относительно предьщущей сеточной области, поступает на первый вход второго сумматора 14. На выходе 19 первого сумматора 13 формируются коды адресов узловых процессоров новой сеточной области с учетом сдвига начала отсчета координат. Процесс циклически повторяется при обходе всех запрограммированных сеточных областе для получения частных решений, из которых формируется окончательное решение задачи. Таким образом, устройство позволяет при одной загрузке памяти осуществить обход сеточной .област по заданному закону при занесении данных и съеме решения во всех итерациях и при получении частных решений на сдвинутых моделируемых сеточных областях.

Формула изобретени

Вероятностное устройство для решения конечно-разностных уравнений, содержащее элемент ИЛИ, первый и второй счетчики, первый и второй блоки памяти, первый регистр, вход записи которого является тактовым входом устройства и подключен к Первому входу элемента ИЛИ, выход которого соединен с счетным входом первого счетчика, установочный вход которого под- ключей к выходу первого блока сравне- ния и к установочному входу второго счетчика, вход записи которого соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу второго блока сравнения, первый и второй триггеры и первый сумматор, выход которого является выходом устройства, вход ввода данных которого соединен с информационными входами первого и второго блоков памяти, пер вого и второго счетчиков и первого регистра, выход которого подключен к первому входу первого блока сравнения, второй вход которого соединен с выходом второго счетчика и с первым входом второго блока сравнения, вто

рой вход которого подключен к выходу первого блока памяти, адресный вход которого соединен с выходом первого счетчика и с адресным входом второго блока памяти, выход которого подклкг чен к первому входу первого суммато ра, вход запуска устройства соединен с установочными входами первого и второго триггеров, выходы которых по ключены к входам записи чтения соответственно первого и второго блоков яамяти, отличающееся тем, что, с целью повьшения быстродействия, в него введены второй ре- гистр, второй сумматор, третий блок

памяти и третий триггер, выход которого подключен к входу записи-чтения третьего блока памяти, выход которого соединен с первым входом второго сумматора, выход которого соединен с вторым входом первого сумматора, вход ввода данных устройства подклкг- чеи к информационным входам третьего блока памяти и второго регистра, выход которого соединен с адресньм входом третьего блока памяти, тактовый вход устройства подключен к входу записи второго регистра, второй вход второго сумматора соединен с выходом второго счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обхода узлов сеточной области | 1984 |

|

SU1168965A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1149278A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Вероятностное устройство для решения уравнения Лапласа | 1983 |

|

SU1091172A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для решения уравнений математической физики | 1986 |

|

SU1363260A1 |

| Устройство для анализа параметров графа | 1986 |

|

SU1532942A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1095190A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах для решения дифференциальных уравнений в частных производных итерационным методом. Цель изобретения - повышение быстродействия устройства за счет снижения затрат времени на повторное формирование массива исходных данных при повторных решениях со сдвигом моделируемой сеточной области. Цель изобретения -достигается за счет введения в устройство регистра, сумматора, блока памяти и триггера с соответствующими функциональными связями меяг- ду ними и известными блоками устройства. Устройство позволяет при одной загрузке памяти осуществить обход сеточной области по заданному закону при занесении данных и съеме решений во всех итерациях и при ползгчении частных решений на сдвинутых моделируемых сеточных областях. 1 ил. (Л

19,

18

Составитель В, Рыбин Редактор П. Коссей Техред Г.Гербер Корректор Q. Луговая

3093/53

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушска1Я наб., д. 4/5

Производственно -полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Вероятностное устройство для решения конечно-разностных уравнений | 1972 |

|

SU477418A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обхода узлов сеточной области | 1984 |

|

SU1168965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-07—Публикация

1984-11-20—Подача