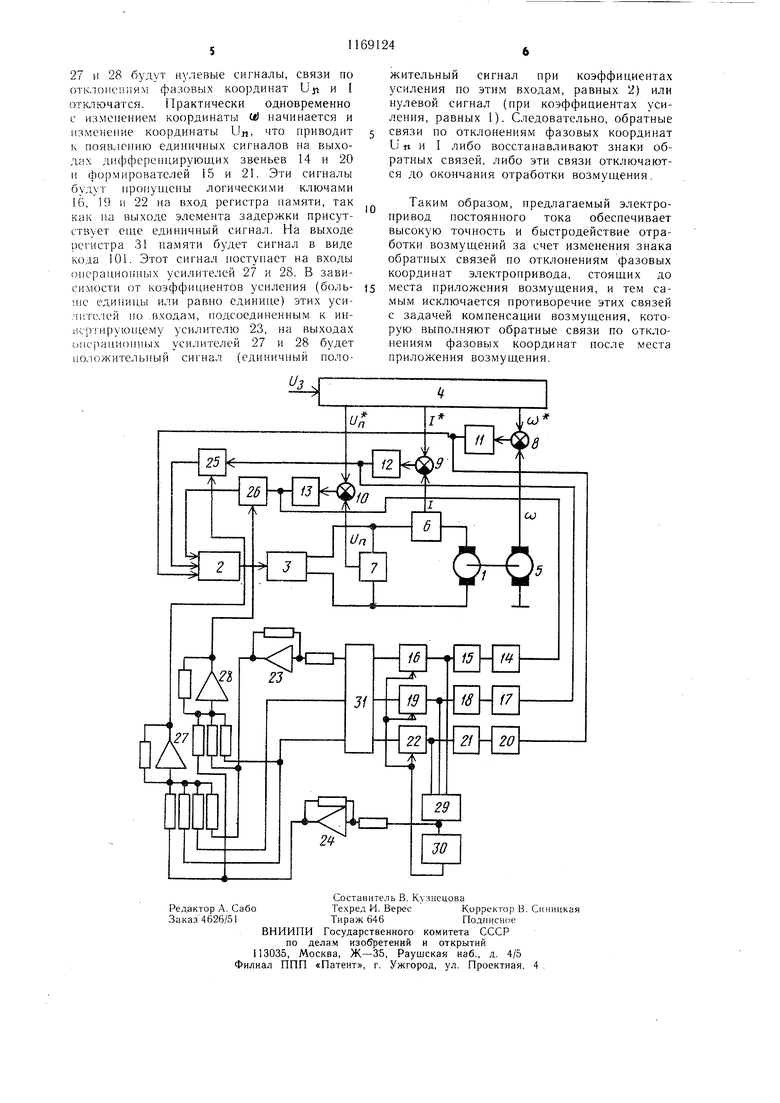

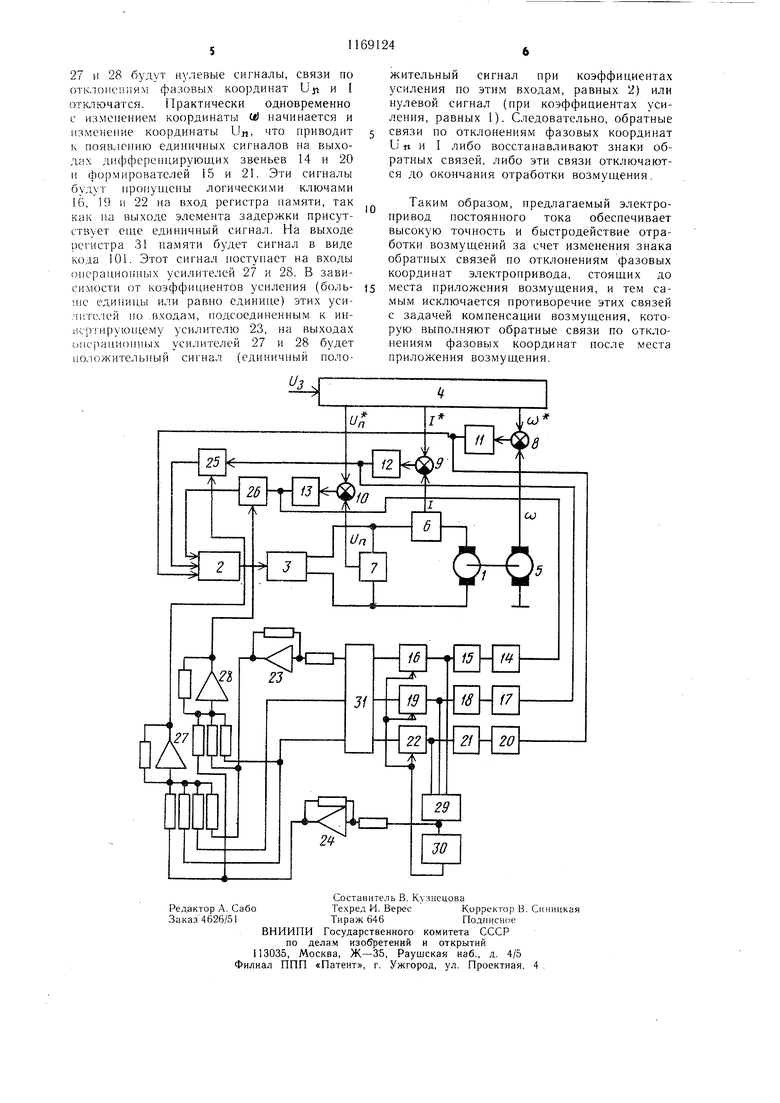

Изобретение относится к электротехнике и может быть использовано при создании систем электроприводов для металлургии, химической промышленности, машиностроения. Цель изобретения - повышение точности и быстродействия электропривода. На чертеже представлена блок-схема электропривода. Электропривод содержит электродвигатель 1, последовательно соединенные регулятор 2 и подключенный к якорной цепи электродвигателя тиристорный преобразователь 3, задатчик желаемых фазовых координат электропривода, выполненный в виде модели 4 электропривода, датчик 5 частоты вращения, датчик 6 тока якоря и датчик 7 напряжения, блоки 8-10 сравнения, вычитающие входы которых соединены соответственно с выходами датчиков 5-7 частоты вращения, тока якоря и напряжения, а суммирующие входы - с соответствующими выходами модели 4 электропривода, при этом выходы блоков 8-10 сравнения подключены ко входам усилителей И -13 соответственно, выход первого из которых соединен с входом регулятора 2. Электропривод содержит также три цепи, состоящие: первая - из последовательно соединенных дифференцирующего звена 14, формирователя 15 прямоугольных импульсов и логического ключа 16, вторая - из дифференцирующего звена 17, формирователя 18 импульсов и логического ключа 19, третья - из дифференцирующего звена 20, формирователя 21 импульсов и логического ключа 22. Кроме того, электропривод содержит инвертирующие усилителя 23 и 24, блоки перемножения 25 и 26, операционные усилители 27 и 28, последовательно соединенные логический элемент ИЛИ-НЕ 29 и элемент 30 задержки, а также регистр 31 памяти с тремя разрядами, входы каждого разряда которого через указанные три цепи подключены к выходам усилителей 11 -13, выход первого разряда регистра памяти через инвертирующий усилитель 23, а выход третьего разряда непосредственно связаны с входами операционных усилителей, входы которых соединены также с выходом инвертирующего усилителя 24, выход второго разряда регистра памяти связан с входом операционного усилителя 27, а выходы операционных усилителей 27 и 28 подключены к входам блоков 25 и 26 перемножения, вторые входы которых соединены с выходами усилителей 12 и 13, а их выходы - с входами регулятора 2, при этом вход инвертирующего усилителя 24 подключен к выходу логического элемента ИЛИ,-НЕ 29, входы которого соединены с выходами формирователей 15, 18 и 21 прямоугольных импульсов, а выход элемента 30 задержки подключен к управляющим входам Логических ключей 16, 19 и 22. Электропривод работает следующим образом. До подачи задающего сигнала Ui на вход модели 4 желаемые значения U, I, f, фазовых координат электропривода равны нулю, текущие значения фазовых координат электропривода, измеряемые датчиком 7 напряжения, датчиком 6 тока и датчиком 5 частоты вращения, также равны нулю. Следовательно, и на выходах усилителей 11 -13 сигнал равен нулю. Это обеспечивает нулевые сигналы на выходах дифференцирующих звеньев 14, 17 и 20 и на выходах формирователей 15, 18 и 2 прямоугольных импульсов. Нулевые сигналы с выходов формирователей 15, 18 и 21 поступают на входы логического зл«.гмента ИЛИ-НЕ 29, на выходе 1с;м-г-р-:,:;.. появляется единичный сигнал. 3oi лп ничный сигнал проходит через элемент 30 задержки и поступает на управ. иющне входы логических ключей 16, 19 и 22, которые при этом позволяют нулевым сшналом с формирователей 15, 18 и 21 поступить на входы разрядов регистра 31 па.мяти. На выходе регистра памяти, следовательно, в каждом разряде записаны нулевые сигналы. Эти нулевые сигналы поступают на входы операционных усилителей 27 и 28 (коэффициент усиления равен единице по всем ходам за исключением входов, подсоединенных к инвертору 23), не вызывая изменения их состояния. Кроме того, на входы операционных усилителей 27 и 28 поступает сигнал через инвертор 24 с выхода элемента ИЛИ-НЕ 29, т.е. на входы операционных усилителей 27 и 28 поступает единичный отрицательный сигнал. Этот сигнал, пройдя операционные усилители 27 и 28, поступает на вторые входы блоков перемножения 25 и 26, т.е. на вторые входы блоков перемножения поступают единичные положительные сигналы. Следовательно, на вход регулятора 2 поступает суммарный нулевой сигнал. После подачи задающего сигнала Uj в модели 4 формируются желаемые значе ния Un, ty фазовых координат электропривода. Это формирование осуществляется с запаздыванием при дв окении входного сигнала от входа модели к выходу. Указанное выше обстоятельство приводит к тому, что в момент вре.мени начала изменения желаемой фазовой координаты U« изменение других фазовых координат 1 и jAj отсутствует. В результате этого в момент начала изменения фазовой коорди-наты Ua на выходе усилителя 13 появляется сигнал отклонения первой координаты электропривода / Un от желае.мой

фазовой координаты UJI . Этот сигнал дифференцируетсядифференцирующим

звеном 14. Сигнал с выхода дифференцирующего звена 14 поступает на формирователь 15 импульсов, на выходе которого формируется единичный сигнал. В этот момент времени на выходе усилителей 12 и 11 изменений сигналов не будет. Следовательно, на выходах формирователей 18 и 21 импульсов нулевые сигналы. На входах элемента ИЛИ-НЕ 29 при этом будет сигнал в виде кода 100, а на выходе - сигнал, равный нулю. Этот сигнал поступает на управляющие входы логических ключей 16, 19 и 22 через некоторое время, определяемое временем задержки элемента 30 задержки.

Так как до появления нулевого сигнала на управляющих входах логических ключей 16, 19 и 22 присутствовал единичный сигнал, то сигнал в виде кода 100 с формирователей 15, 18 и 21 импульсов поступает на входы разрядов регистра 31 памяти. Через время задержки элемента задержки 30 на управляющие входы логических ключей 16, 19 и 22 поступает нулевой сигнал и сигналы с формирователей 15, 18 и 21 импульсов на входы регистра 30 памяти не поступают. На выходе регистра 30 памяти в первом разряде записана единица, а во втором и третьем - ноль. Это приводит к тому, что на входы операционных усилителей 27 и 28 подается с инвертирующего усилителя 23 единичный отрицательный сигнал. На все остальные входы операционных усилителей 27 и 28 поступают нулевые сигналы. Благодаря этому на выходах операционных усилителей 27 и 28 будут единичные положительные сигналы, которые поступают на вторые входы блоков перемножения 25 и 26. Следовательно, в этом случае сигналы отклонений фазовых координат от желаемых фазовых координат электропривода, усиленные усилителями 11 -13, поступают на вход регулятора 2 без изменения своего знака. Отработка задающего сигнала осуществляется при использовании всех фазовых координат электропривода, что обеспечивает высокие качественные показатели воспроизведения задающего сигнала. По окончании отработки входного сигнала на выходе дифференцирующих звеньев 14, 17 и 20 будут нулевые сигналы, которые поступают через формирователи 15, 18 и 21 импульсов на входы логических ключей 16, 18 и 22 и ,на входы логического элемента ИЛИ- НЕ 29. На выходе логического элемента ИЛИ-НЕ 29 появляется е;ии ичный сигнал, который через элемент 30 задержки поступает на управляющие входы логических ключей 16, 19 и 22. На входы регистра 31 памяти поступает сигнал в виде кода 000, который и записывается в регистре. На вторые х()Д1м б.кжов псромпожонпн 25 и 26 иоступаш, как и прежде, единичный п()Л()Ж11Т0. спгиа.ч. T;iK к;;1ч с sinхода логического элемент; П. НЕ через инвсрто 24 на входы o;iep;ii,i oii;:;j усилителей 27 и 28 поступает единииы; отрицатсльныи снгна..

Рассмотрим работу лсктроприво.та при отработке внещнего воздействия (ст;:0тического момента нагрузки на ва.чу ,I,B ;гателя). Это воздействие первонача.пьно вызывает изменение отклонения фазов.ч координаты It/ от желаемой фазовой координаты Gtft электропривода, которое через усилитель 1 и дифсЬерениирмощее звено 20 поступает на формирователь 2 импульсов. На выходе формировате.чя 21 появляется единичный сигнал, is этот момент времени на выходах формирователей 15 и 18 будут нулевые сигналы, так как 1:;ме0 нение фазовых координат Un и 1 начинается спустя некоторое время пос.пе иача.ла изменения UJ. Сигналы с выходов фор.мирователей 15, 18 и 21 через логические ключи 16, 19 и 22 поступают на входы регнет5 ра 31 памяти. Проход сигналов с формирователей 15. 18 и 21 через ключн 16. 19 и 22 возможен, так как на унравляюнхнх входах последних будет еще eдинич il IЙ сигнал, который станет равным нулю через время задержки эле.мента 30 задержки.

0 В регистре 31 памяти записывается при этом сигнал в виде кода 001. На выходах операционных усилителей 27 и 28 будп единичный отрицательный сигнал, так как на их входы с выхода третьего разряда регистра .31 памяти поступает единичный

5 положительный сигнал. Единичные отрицательные сигналы, поступающие на вторые входы блоков перемножения 25 н 26, изменяют знак обратных связей по отклонениям фазовых координат IJn и I. Это приQ водит к тому, что при набросе нагрузки фазовые координаты U п н 1 нарастают форсированно н устанавливаются на свои.х предельных положительных значениях (прп сбросе нагрузкн фазовые координаты UH и i убывают форсированно н устанав,1ИБаются на ср.опх предельных отряцателы;ых 311аче пях). Как только отклонение фазопой коррдпнаты w достигнет максимального значения, на выходе .4;:;| : epeiiщппющего звена 20 и на йыходс фор.чирюватс,1я 21 Г|;)я«,1яуотся 11у,евые cm ii;i,.

Это 1р1 НОДИТ к тому, что на L-U)l,Xn-It ,li)niческ1)1-(1 э.-1емеита ИЛИ - ИГ. 29 ,и-т е,in 1 5Ч|1ын о.игпа., К:) черс:-- иннср: мр шUIUM eH,i:Tv,i); 2-1 ioeTyi;;Ur :;ii ..i,-; операционных ти,111те,1ей 27 и 26, на входы 5 которых также поступает ел;1мнч; ый iio,4(iжнтс.чьный сигна,:; е вых().л,и г|1етье:ч) ра,ряда регистра М памяти, Ь i)e.,i T:rrv этого на выходе (операционных еилите.;ей

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЛЕ СИНХРОНИЗАЦИИ | 2003 |

|

RU2233501C1 |

| РЕЛЕ СИНХРОНИЗАЦИИ | 2003 |

|

RU2231848C1 |

| РЕЛЕ СИНХРОНИЗАЦИИ | 2003 |

|

RU2248638C2 |

| Измеритель временных интервалов | 1985 |

|

SU1307444A1 |

| Электропривод постоянного тока | 1983 |

|

SU1100697A1 |

| Преобразователь кода в скорость вращения вала | 1988 |

|

SU1599991A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Система контурного управления промышленного робота | 1986 |

|

SU1430256A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА, содержащий электродвигатель и последовательно соединенные регулятор и подключенный к якорной цепи электродвигателя тиристорный преобразователь, задатчик желаемых фазовых координат электропривода, выполненный в виде мох1ели электропривода, лТатчики частоты вращения, тока якоря и напряжения на якоре электродвигателя, три блока сравнения, вычитающие входы которых соединены соответственно с выхода.ми датчиков частоты вращения, тока якоря и напряжения на якоре электродвигателя, а суммирующие входы - с соответствующими выходами модели электропривода, при этом выход каждого блока сравнения подключен к входу соответствующего усилителя, выход первого из которых соединен с входом регулятора, отличающийся тем, что, с целью повышения точности и быстродействия, в него введены три цепи, каждая из которых состоит из последователь 10 соединенных диффереи и1рую1цего звена, формирователя прямоугольных импульсо15 и логического ключа, два инвертирующих усилителя, два блока перемножения, два операционных усилителя, последовательно соединенные логический элеме1гг ИЛИ-НЕ и элемент задержки, а также регистр памяти с тре.мя разрядами, входы каждого разряда которого через указанные три цепи подключены к выходам уси.:м1те,1ей, выход первого разряда регистра памяти черен первый инвертирующий усилите:1ь, а выход i третьего разряда непосредственно связаны с входами операционных усилителей, входы которых соединены также с выходом второго инвертирующего уси,1нтеля, выход второго разряда регистра памяти связан с входом одного из операционных усилителей, а выходы операционных усилителей подключены к входам блоков перемноже)« ния, вторые входы которых соединены по рознь с выходами второго и третьего усилителей, а их выходы - с входами регулятора, при этом вход второго инвертирующего уси,тителя подключен к выходу элемента Ю 4 ИЛИ - НЕ, входы которого соединены с выходами формирОБате,1ей прямоугольных импульсов, а выход элемента задержки подключен к управляющим входам логических ключей.

| Гарнов В | |||

| К-, Рабинович Б | |||

| Б., Вишневецкий Л | |||

| М | |||

| Унифицированные системы автоуправления электроприводом в металлургии | |||

| М., «Металлургия, 1971,-с | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Жиляков В | |||

| И | |||

| Исследование особых режимов релейных систем управления | |||

| Известия ВУЗОВ | |||

| «Электромеханика, 1983, № 8, с | |||

| . | |||

Авторы

Даты

1985-07-23—Публикация

1983-12-07—Подача