n-разрядного регистра сдвига, последовательный выход которого соеданен с вторыми входами второго и третьего сумматоров, выход последнего соединен с последовательным входсв4 третьего п-разрядного регистра сдвига, параллельньй выход которого вместе с параллельным выходом первого п-разрядного регистра сдвига подключен к блоку сравнения кодов, выход которого подключен к- первому входу пятого логического элемента И, связанного через блок задержки с установочным входом распределителя .импулсов, с вторьми входами первого и второго логических элементов И и со счетным входом счетчика, выход генератора импульсов соединен с переключающим входом распределителя импульсов, нулевой выход которого подключен к управляющим входам первого и.второго блоков совпадения и к установочным входам блоков формирования кода, выходы распределителя пульсов с первого по п-й через п цепей из последовательно соединенных дифференцирующей цепочки и одновибратора подключены к п входам логического элемента ИЛИ, выход которого соединен с входами управления сдвигом п-2-разрядных регистров сдвига, п-разрядных регистров сдвига, п-разрядного реверсивного счетчика-регистра сдвига и с синхронизирующими входами блоков формирования кода, n+1-й выход распределителя импульсов подключен к второму входу пятого логического элемента И, выходк управляющим входам третьего и четвертого логических элементов И и третьего блока совпадения, п+З-й выход - к установочным входам п-разрядного реверсивного счетчика-регистра сдвига, второго п-разрядного регистра сдвига и счетчика, выход которого подключен к информационному входу третьего блока совпадения, выход которого соединен с входом информационных разрядов регистра, выход которого через последовательно соединенные цифроаналоговый преобразователь, блок масштабирования и блок ограничения связан с вторым входом регулятора скорости.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1972 |

|

SU458004A1 |

| Устройство для формирования изображений на экране электронно-лучевой трубки | 1989 |

|

SU1665403A2 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

| Устройство для решения игровых задач на вычислительных сетях | 1982 |

|

SU1104522A1 |

| Генератор векторов для системы отображения графической информации | 1974 |

|

SU525980A1 |

| Линейный интерполятор | 1989 |

|

SU1674064A1 |

| Коррелятор | 1986 |

|

SU1339584A1 |

| Устройство для формирования символов на экране электронно-лучевой трубки | 1984 |

|

SU1251061A1 |

| Устройство для сжатия и восстановления информации | 1983 |

|

SU1149295A1 |

1. ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА, содержащий электродвигатель постоянного тока с усилителем мощности, входом подключенным к регулятору скорости, один КЗ входов которого связан через масштабирования с цифроаналоговым преобразователем, a к другому входу подключен датчик скорости, соединенный с рабочим механизмом, связанным входом с электродвигателем постоянного тока, выходом - с цифровым датчиком координаты, отличающийся тем, что, с целью повышения быстродействия и точности останова рабоче- .го механизма, в него введены блок ограничения, три блока совпадения, два блока формирования кода, логический элемент НЕ, три сумматора, блок сравнения кодов, пять логических элементов И, блок задержки,.счетчик регистр, генератор импульсов, распределитель импульсов, логический элемент ИЛИ, три п-разрядных регистра сдвига, п-разрядный реверсивный счетчик-регистр сдвига, п цепей из последовательно соединенных дифференцирующей цепочки и одновибратора, два п-2-разрядных регистра сдвига и задатчик координаты, причем знаковые выходы задатчика координаты и цифрового датчика координаты подключены соответственно к командному входу первого блока формирования кода и через логический элемент НЕ ккомандному входу второго блока формирования кода, a их информационные выходы - к информационным входам соответственно первого и второго бло ков совпадения, выходы которых соединены с параллельными входами соответственно первого и второго n-2-разg рядных регистров сдвига, последовательные выходы которых подключены к информационным входам соответствующих блоков формирования кода, выходы которых подключены к первому сумматору, вьпсодом соединенному с последовательным входом первого п-разрядногр регистра сдвига, прямой и инверсный выходы знакового разряда которого подключены к первым входам соответственно первого и второго, Од третьего и четвертого логических элементов И, выходы первых двух из коСО торых соединены соответственно с вы читающим и суммирующим входами п-разрядного реверсивного счетчика-регщ; ра сдвига, выходы других двух - соответственно с единичным и нулевым входами знакового разряда регистра, последовательный выход п-разрядного реверсивного счетчика-регистра сдвига соединен с его же йоеледЬвaтельным входом и с первым входом второго сумматора, выход которого подключен к первому входу третьего сумматора и к последовательному входу второго

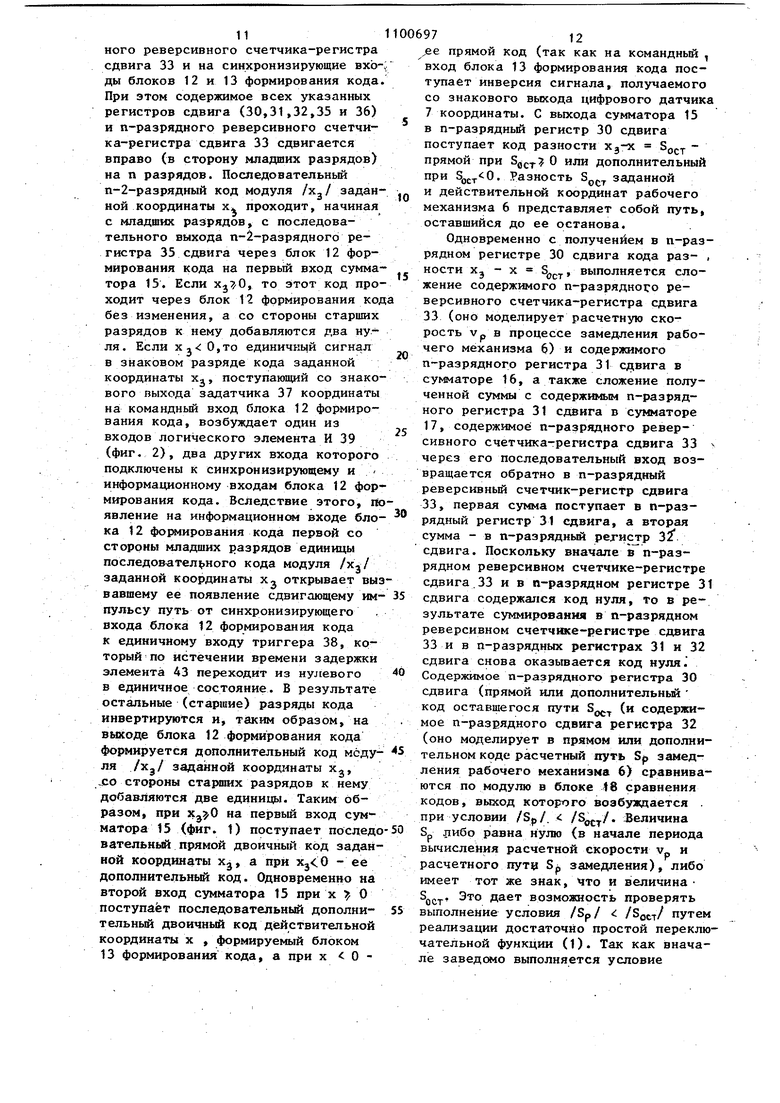

Изобретение относится к электротехнике и может быть использовано для координатного управления приводом, в частности электроприводом ра бочих механизмов в машиностроении, приборостроении, металлургии. Известна цифровая система автома тического останова стана, содержаща блоки измерений длины полосы и блок измерений скорости, подключенные к входам блока сравнения, выход которого через блок выходных преобразователей подключен к входу органа, управлшощего скоростью стана. В про цессе замедления блок сравнения кон ролирует одновременность появления сигналов, соответствующих некоторым дискретным расчетным значениям скорости и длины полосы С11. Недостатками системы являются возможные значительные отклонения процесса замедления от равнозамедлен ного движения, оптимального в смысле быстродействия, и невысокая точность останова. Эти недостатки обусловлены дискретностью измерений (при фиксированных значениях числа витков полосы на барабане моталки), а также релейным характером управления скоростью. Наиболее близким к изобретению по технической сущности является электропривод постоянного тока, содержащий электродвигатель постоянного тока с усилителем мощности, входом подключенные к регулятору скорости, один из входов которого связан через блок масштабирования с цифроаналоговым преобразователем, а к другому входу подключен датчик скорости, соединенный с рабочим механизмом, связанньм входом с электродвигателем постоянного тока, выходом- с цифровые датчиком координаты С 2. Недостатками этого электропривода также являются возможные значительные 3 отклонения процесса замедления от оп тимального в смысле быстродействия равнозамедленного движения и относительно невысокая точность останова Эти недостатки, обусловленные ограни ченной возможной точностью используе мого аналогового нелинейного преобразователя, не позволяют применять электропривод в случаях, когда требуется быстродействие и высокая точность останова рабочего механизма. Цель изобретения,- повьппение быст родействия и точности останова рабочего механизма. Поставленная цель достигается тем, что в электропривод постоянного тока, содержащий электровдигатель постоянного тока с усилителем мощности, входом подключенным к регулятору скорости, один из входов которо го связан через блок масштабирования с цифроаналоговым преобразователем, а к другому входу подключен датчик скорости, соединенный с рабочим механизмом, связанньм входом с электродвигателем постоянного тока, выходом - с цифровым датчиком координаты введены блок ограничения, три блока совпадения, два блока формирования кода, логический элемент НЕ, три сумматора, блок сравнения кодов, пять логических элементов И, блок задержки, счетчик, регистр, генератор импульсов, распределитель импуль сов, логический элемент ИЛИ, три п-разрядных регистра сдвига, п-разрядный реверсивный, счетчик - регистр сдвига, п цепей из последовательно соединенных дифференцирующей цепочки и одновибратора, два n-2-разрядных регистра сдвига и задатчик координаты, причем знаковые выходы задатчика координаты и цифрового датчика координаты подключены соответственно к командному входу первого блока формирования кода и через логический -элемент НЕ - к командному входу второго блока формирования кода, а их информационные выходы - к информационным входам соответственно первого и второго блоков совпадения, выходы которых соединены с: параллельньвш входами соответственно первого и второго n-2-разрядных регистров сдаига, последовательные выходы которых подключены к информационным входам соответствующих блоков формирования кода, выходы которых подклю974чеиы к первому сумматору, выходам соединенному с последовательным входом первого п-разрядного регистра сдвига, прямой и ннверсный выходы знакового разряда которого подключены к первым входам соответственно первого и второго, третьего и четвертого логических злементов И, выходы первых двух из которых соединены соответственно с вычитающим и суммирующим входами п-разрядного реверсивного счетчика-регистра сдвига, выходы других двух - соответственно с единичным и нулевые входами знакового разряда регистра, последовательный выход п-разрядного счетчика-регистра сдвига соединен с его же последовательным входом и с первым входом второго сумматора, выход которого подключен к первому входу третьего сумматора и к последовательнo fy входу второго п-разрядного регистра сдвига, последовательный выход которого соединен с вторыми входами второго и третьего сумматоров, выход последнего соединен с последовательные третьего п-разрядного регистра сдвига, параллельный выход которого вместе с параллельным выходом первого п-разрядного регистра сдвига подключен к блоку сравнения кодов, выход которого подключен к первому входу пятого логического элемента И, связа1нного через блок задержки с установочным входом распределителя импульсов, с вторыми входами первого и второго логических элементов И и со счетным входом счетчика, выход генератора riftjпульсов соединен с .переключающим входом распределителя импульсов, нулевой выход которого подключен к управляющимвходам первого и второго блоков совпадения и к установочным входам блоков формирования кода, выходы распределителя импульсов с первого по-п-й через п целей из последовательно соедашенных дифференцирующей цепочки и одновибратора Р подключены к д входам логического элемента ИЛИ, выход которого соединен с входами управления сдвигом п-2-разрядньк регистров сдвига,п-разрядных регистров сдвига,ti-разрядного реверсивного счетчика-регистра сдвига и с синхронизирующими входами блоков формирования кода, ri+1-й выход распределителя импульсов подключен к второму входу пятого логического элемента И, n+2-й выход - к управляющи входам третьего и четвертого логических элементов И и третьего блока совпадения, п+3-и выход - к установочным входам п-разрядного реверсив ного счетчика-регистра сдвига, второго п-разрядного регистра сдвига и счетчика, выход которого подключен к информационному входу третьего блока совпадения, выход которого подключен к -информационному входу третьего блока совпадения, выход ко торого соединен с входом информационных разрядов регистра, выход которого через последовательно соединенные цифроаналоговый преобразователь, блок масштабирования и блок ограничения связан с вторым входом регулятора скорости. На фиг. 1 приведена функциональная схема электропривода постояннйго тока; на фиг. 2 - схема блока формирования кода; на фиг. 3 - схема блока сравнения кодов. Электропривод постоянного тока содержит электродвигатель 1 постоянного тока (фиг. 1) с усилителем мощности, входом подключенным к регулятору 2 скорости, один из входов которого связан через блок 3 масштабирования с цифроаналоговым преобразователем 4, а к другому входу подключен датчик 5 скорости, соединенный с рабочим механизмом 6, связанны входом с электродвигателем 1, выходом - с цифровым датчиком 7 координаты. Электропривод также содержит блок 8 ограничения, три блока 9, 10 и 11 совпадения, два блока 12 и 13 форформирования кода, логический элемен НЕ, 14, три сумматора 15, 16 и 17,блок 18 сравнения кодов, пять логических элементов И 19-23, блок 24 задержки, счетчик 25, регистр 26, генератор 27 импульсов, распределитель 28 импульсов, логический элемент ИЛИ 29,три п-разрядных регистра 30, 31 и 32 сдви га, п-разрядный реверсивный счетчикрегистр сдвига 33, п цепей из после „„ , .. .л., HWV.J1C довательно соединенных дифференцирующей цепочки и одновибратора 34, два / riTALr rTOTTr tJtrtr ТЛ лттттлв- ЯЧ - ч л л .n-2-разрядных регистра 35 и 36 сдвига задатчик 37 координаты. Знаковые выходы задатчика 37 координаты и цифрового датчика 7 координаты подключены соответственно к командному входу первого блока 12 формирования кода и через логический элемент НЕ 14, к 6976 командному входу второго блока 13 формирования кода, а их информационные выходы - к информационным входам соответственно первого и второго блоков 9 и 10 совпадения, выходы которых соединены с параллельными входами соответственно первого и второго n-2-разрядных регистров 35 и 36 сдвига, последовательные выходы которых подключены к информационным входам соответствующих блоков 12 и 13 форм фования кода, выходы которых подключены к первому сумматору 15, выходом соединенному с последовательным входам первого п-разрядного регистра сдвига, прямой и инверсньй выходы знакового разряда которого подключены к первым входам соответственно первого 19 и второго 20, третьего 21 и четвертого 22 логических элементов И, выходы первых двух из которых (т.е. элементов 19 и 20) соединены соответственно с вычитающим и суммирующим входами п-разрядного реверсивного счетчика-регистра сдвига 33, выходы других двух логических элементов И 21 и 22 соединены соответственно с единичным и нулевым входами знакового разряда регистра 26. Последовательный выход -разрядного реверсивного счетчикарегистра сдвига 33 соединен с его же последовательным входом и с первым входом второго сумматора 16, ш.1ход которого подключен к первому входу третьего сумматора 17 и к последовательному входу второго п-разрядного регистра 31 сдвига, последовательный выход которого соединен с вторыми входами второго и третьего сумматоров 16 и 17, выход последнего соединен с последовательным входом третьего п-разрядного регистра 32 сдвига, параллельный выход которого вместе с параллельным выходом первого п-разрядного регистра 30 сдвига подключен к блоку 18 сравнеия кодов, выход которого подключен первому входу пятого логического лемента И 23, связанного через блок лемента и 23, связанного через б 4 задержки и установочным входом - аспределителя 28 импульсов, с втоьми входами первого и йторогологиеских элементов И 19 и 20 и со счетым входом счетчика 25, выход генераора 27 импульсов соединен с переклюающим входом распределителя 28 имульсов, нулевой выход которого подлючен к управляющим входам первого 10 совпадения и второго блоков и к установочным входам блоков 12 и 13 формирования. Выходы распределителя 28 импульсов с первого по п-й через п цепей из последовательно сое диненных дифференцирующей цепочки и одновибратора 34 подключены к п входам логического элемента ИЛИ 29, выход которого соединен с входами управления сдвигом n-2-разрядных регистров 35 и 36 сдвига, п-разрядных регистров 30, 31 и 32 сдвига, п-разрядного реверсивного счетчика-регистра сдвига 33 и с синхронизирующими входами блоков 12 и 13 формирования кода, n+1-й выход распределителя 28 Импульсов подключен к второму входу пятого логического элемента И 23, (п+2)-й выход - к управляющим входам третьего и четвертого логических элементов И 21 и 22 и третьего блока 11 совпадения, (п+3)-й выход - к установочным входам п-разрядного реверсивного счетчика-регистра сдви га 33, второго п-разрядного регистра 31 сдвига и счетчика 25, вьгход которого подключен к информационном входу третьего блока 11 совпадения, выход которого соединен с входом информационных разрядов регистра 26 выход которого через последовательно соединенные цифроаналоговый преобразователь 4, блок 3 масштабирования и блок,В ограничения связан с вторым входом регулятора 2 скорости. Блок формирования 12(13) кода со держит триггер 38 .(фиг. 2), три логических элемента И 39, 40 и 41, ло гический элемент НЕ 42, элемент 43 задержки и логический элемент ИЛИ 44 Блок 18 сравнения кодов может быть выполнен, например, в виде ком бинационной логической схемы, реали зующей переключательную функцию («2 24 2 2 2 2hVhV«3 3)- . -KHV..VlVl) «iS(«2 V( Vh )- -4%HV(VlWVl4H)n4)--)) v()4 3-4-r .a,5 - прямые и 1 7 2 2 инверсные двоичные сигналы н первом входе блока 18 сравнения кодов, подключаемом к параллельному выходу первого п-разрядного регистра 30 7 8 сдвига сигналы на входе знакового разряда); bi,b, bj, Ь2,...Ь„, прямые и инвесрные двоичные сигналы на втором входе блока 18 сравнения кодов, подключаемом к параллельному выходу третьего п-разрядного регистра 32 сдвига (Ь, В - сигналы на входе знакового разряда); с - сигнал на выходе блока 18 сравнения кодов. Блок 18 сравнения кьдов (фиг. 3) содержит три логических элемента И 45, 46 и 47, два логических элемента ИЛИ 48 и 49, логические схемы разрядов с второго по пг1-;й, А, ... ,А, составленные из п-2 групп 50 по. шесть логических элементов И каждая и п-2 групп 51 по три логических элемента ИЛИ каждая, а также два логических элемента И 52 и 53. Регулятор 2 скорости (фиг. 1) может быть выполнен в виде пропорционально-интегрального регулятора. Блок 3 масштабирования выполнен, например, в виде потенциометра. Цифроаналоговый преобразователь 4 выполнен, например, в виде преобразователя прямого двоичного нормального кода (со знаком) в электрическое напряжение. Цифровой датчик координаты может быть выполнен, например, в виде последовательного соединения преобразователя линейного или углового перемещения в двоично-десятичный рефлексный код, преобразователя двоичнодесятичного рефлексного кода в двои но-десятичньй и преобразователя двоично-десятичногр кода в прямой двоичный нормальный код (со знаком). Если на выходе преобразователя перемещения формируется непосредственно на прямой двоичньй нормальный код, то преобразователи кодов отсутствуют. Блок 8 о-граничения может быть выполнен в виде диодного ограничителя. ; Первые два блока 9 и 10 совпадет. ния содержат по п-2 логических элементов И (где п - максимальное число разрядов в двоичном представлении разности заданной и действительной кординат со знаковым разрядом), тре тий блок 11 совпадения содержит 2(т-1) логических элементов И (где m - максимальное число разрядов в двоичном представлении максимальной расчетной скорости со знаком). Сумматоры 15, 16 и 17 выполнены, например, в виде одноразрядных комби национных сумматоров последовательных кодов с задержкой переноса. Счетчик 25 выполнен, например, в виде т-1-разрядного двоичного счетчи Регистр 26 выполнен, например, в виде га-разрядного регистра. Распределитель 28 импульсов выполнен, например, в риде последовательного соединения счетчика и деши ратора с числом выходов, не меньшим п+4, п-разрядный реверсивный счетчик регистр сдвига 33 выполнен, найример в виде реверсивного счетчика на 1К-триггерах, дополнительно оснащенного цепями сдвига содержимого вправо (в сторону младших разрядбв). Задатчик 37 координаты выполнен, например, в виде последовательного срединения группы Декадных переключателей, группы шифраторов и преобразователя двоично-десятичного кода в прямой двоичный нормальный код (со знаком). Электропривод постоянного тока работает следующим образом. Перед пуском электродвигателя 1, ; приводящего в движение рабочий механизм 6, с помощью задатчика 37 координаты устанавливают заданную ко ординату Хд рабочего механизма 6. При подаче питания (цепи питания на фиг. 1 не показаны) на знаковом и ин формационном выходах задатчика 37 координаты формируется параллельньй прямой двоичный нормальный код заданной координаты х (со знаковым разрядом), а на знаковом и информационном выходах цифрового датчика 7 координаты - параллельный прямой двоичный нормальный код действительной координаты X (со знаковьо разрядом) . Одновременно начинает работать генератор 27 импульсов, вызывая изменение состояний распределителя 28 импульсов. После включения питания n-2-разрядные регистры 35 и 36 сдвига, блоки 12 и 13 формирования кода, п-разрядные регистры 30, 31 и 32 сдвига, п-разряднЫй реверсивный счетчик-регистр сдвига 33, счетчик 25, регистр 26 и распределитель 28 импульсов могут оказаться в произвольных начальных состояниях. Однако по истечении времени, не превышающего длительности наиболее продолжительного периода вычислений расчетной скорости и расчетного пути замедления рабочего механизма 6, распределитель 28 импульсов обязательно оказывается в состоянии п+3, которому соответствует наличие на его (п+3)-м выходе сигнала, устанавливающего п-разрядный регистр 31 сдвига, п-разрядный реверсивный счетчикрегистр сдвига 33 и счетчик 25 в нулевые состояния, после чего распределитель 28 импульсов переходит в свое нулевое состояние. Для того, чтобы переходный процесс при включении электропривода не оказывал влияния на работу электродвигателя 1,не обходимо, с учетом реальной инерционности электродвигателя 1 с усилителем мощности и рабочего механизма, выбрать достаточно высокую рабочую частоту генератора 27 импульсов (например, порядка десятков или сотен кГц), и тогда время переходного процесса будет достаточно малым (например, порядка десятков или единиц мс). По истечении времени переходного процесса начинается нормальный режим работ, который удобно рассматривать, начиная с нулевого состояния распределителя 28 импульсов, причем все регистры (26, 30, 31, 32, 35 и 36), п-разрядный реверсивный счетчик-регистр сдвига 33, счетчик 32 и блоки 13 и 12 формирования кода также находятся в нулевых состояниях. При переходе распределителя 28 импульсов в нулевое состояние на его нулевом выходе появляется сигнал, который вводит с информационных выходов задатчика 37 координаты и цифрового датчика 7 координать соответственно в n-2-разрядные регистры 35 и 36 сдвига, параллельные прямые двоичные нормальные коды модулей /Xj/ и /X/ заданной и действительной координат X, и х (без знаковых разрядов), а также устанавливает блоки 12 и 13 формирования кода в нулевые состояния. Следующие п импульсов генератора 27 импульсов вызывают последовательное появление сигналов на п выходах распределителя 28 импульсов, начиная с первого по 4-й выход. Эта серия . п импульсов через п цепей 34 и логический элемент ИЛИ 29 поступает на входы управления сдвигом регистров . сдвига 30, 31, 32, 35, 36, п-разряднего реверсивного счетчика-регистра сдвига 33 и на синхронизирующие вхо-; ды блоков 12 и 13 формирования кода. При этом содержимое всех указанных регистров сдвига (30,31,32,35 и 36) и п-разрядного реверсивного счетчика-регистра сдвига 33 сдвигается вправо (в сторону младших разрядов) на п разрядов. Последовательный n-2-разрядный код модуля /Xj/ заданной координаты х проходит, начиная с младших разрядов, с последовательного выхода n-2-разрядного регистра 35 сдвига через блок 12 формирования кода на первый вход сумматора 15. Если ,/0, то этот код проходит через блок 12 формирования код без изменения, а со стороны старших разрядов к нему добавляются два нуля. Если х,; О,то единичной сигнал в знаковом разряде кода заданной координаты х, поступающий со знакового выхода задатчика 37 координаты на командный вход блока 12 формирования кода, возбуждает один из входов логического элемента И 39 (фиг. 2), два других входа которого подключены к синхронизирующему и информационному входам блока 12 формирования кода. Вследствие этого, появление на информационном входе блока 12 формирования кода первой со стороны младших разрядов единицы последовательного кода модуля заданной координаты х открывает вызвавшему ее появление сдвигающему импульсу путь от синхронизирующего . входа блока 12 формирования кода к единичному входу триггера 38, который по истечении времени задержки элемента 43 переходит из нулевого в единичное состояние. В результате остальные (старшие) разряды кода инвертируются и, таким образом, на выходе блока 12 формирования кода формируется дополнительный код медуля /Xj/ заданной координаты х, JCO стороны старших разрядов к нему добавляются две единицы. Таким образом, при на первый вход сумматора 1 5 (фиг . 1) поступает последо нательный прямой двоичный код заданной координаты Xj, а при - ее дополнительный код. Одновременно на второй вход сумматора 15 при х 0 поступает последовательный дополнительный двоичный код действительной координаты X , формируемый блоком 13 формирования кода, а при х О прямой код (так как на командный , вход блока 13 формирования кода поступает инверсия сигнала, получаемого со знакового выхода цифрового датчика 7 координаты. С выхода сумматора 15 в п-разрядньй регистр 30 сдвига поступает код разности Xj-x прямой при SOCT О или дополнительный при SQJ.. Разность S, заданной и действительной координат рабочего механизма 6 представляет собой путь, оставшийся до ее останова.

Одновременно с получением в п-разрядном регистре 30 сдвига кода раз- , кости Xj - X ,, выполняется сложение содержимого п-разрядного реверсивного счетчика-регистра сдвига 33 (оно моделирует расчетную скорость VP в процессе замедления рабочего механизма 6) и содержимого п разрядного регистра 31 сдвига в сумматоре 16, а также сложение полученной суммы с содержимым п-разрядного регистра 31 сдвига в сумматоре 17, содержимое п-разрядного реверсивного счетчика-регистра сдвига 33 через его последовательный вход возвращается обратно в п-разрядный реверсивный счетчик-регистр сдвига 33, первая сумма поступает в п-разрядный регистр 31 сдвига, а вторая сумма - в п-разрядный pejrncjrp 32. сдвига. Поскольку вначале в п-разрядном реверсивном счетчике-регистре сдвига.33 и в п-разрядном регистре 3 сдвига содержался код нуля, то в результате суммирования в п-разрядном реверсивном счетчике-регистре сдвига 33 и в п-разрядных регистрах 31 и 32 сдвига снова оказьшается код нуля. Содержимое п-разрядного регистра 30 сдвига (прямой или дополнительный код оставшегося пути S (и содержимое п-разрядного сдвига регистра 32 (оно моделирует в прямом или дополнительном коде расчетный путь Sp замедления рабочего механизма 6) сравниваются по модулю в блоке 48 сравнения кодов, выход которого возбуждается . при условии /Sp/. . Величина SP рибо равна нулю (в начале периода вычисления расчетной скорости v и расчетного путц Sp замедления), либо имеет тот же знак, что и величинаSQJ,, Это дает возможность проверять выполнение условия /Sp/ /SOCT/ путем реализации достаточно простой переключательной функции (1). Так как вначале заведсмо выполняется условие S(,g О, то условие / /Sp/ О также заведомо вьтолняется. Поэтому после вьшолнения операций суммирования в первом цикле вычислений возбуждается выход блока 18 сравнения кодов , подключенный к первому входу логического элемента И 23, На этом .заканчивается первый цикл вычислений. Очередной импульс генератора 27 импульсов переводит распределитель 28

импульсов в состояние п+1, в котором возбуждается его выход, подключенный к второму входу логического элемента И 23. В результате на выходе логического элемента И 23 появляется сигнал, который по истечении времени задержки блока 24 заде ки устанавливает распределитель 28 импульсов в нулевое состояние и одновременно поступает на счетный вход счетчика 25, а также на суммирующий (при SOCT 0) вычитающий (при Sj,-.. 0) вход п-разрядного реверч -1

сивного счетчика-регистра сдвига 31. Таким образ еж, в счетчике 25 оказывается прямой двоичный код с единственной единицей в младшем разряде, а в п-разрядном реверсивном счетчикерегистре сдвига 33 - прямой (при Sgj,j.70) или дополнительный (при ) двоичньй код единйщ младшего разряда.

С установки распределителя 28 импульсов в нулевое состояние начинается второй цикл вычислений, который вьтолняется так же, как и первый, с тем отличием, что в его начале счетчик 25 содержит прямой код модуля единигйй младшего разряда, а п-разрядный реверсивный счетчик-регистр сдвига 33 - прямой или дополнительный код единицы младшего разряда (в зависимости от знака 8, ).Вследствие этого в конце второго цикла вычислений в п-разрядных регистрах

содержимое п-разрядного реверсивного счетчика-регистра сдвига 31 увеличивается или уменьшается на единицу, а распределитель 28 импульсов снова переходит в нулевое состояние.

С установки распределителя 28 импульсов в нулевое состояние начинается третий цикл вычислений. В его начале счетчик 25 содержит прямой код числа 2 (без знакового разряда), п-разрядный реверсивный счетчик-регистр сдвига 33 - прямой или дополнительньй код числа 2 (со знаковым разрядом), п-разрядные регистры 31 и 32 сдвига - прямой или,дополнительный код числа 1. В конце третьего цикла вычислений в п-разрядном регистре 31 сдвига оказывается прямой или дополнительньй код числа 3, а п-разрядном регистре 32 сдвига прямой или дополнительный код числа 4. Если, при этом по-прежнему выполняется условие /SP/ /SQ(,/, то содержимое счетчика 25 и содержимое п-разрядного реверсивного счетчикарегистра сдвига 33 изменяются на единицу, а распределитель 28 импульсов снова переходит в нулевое состояние.

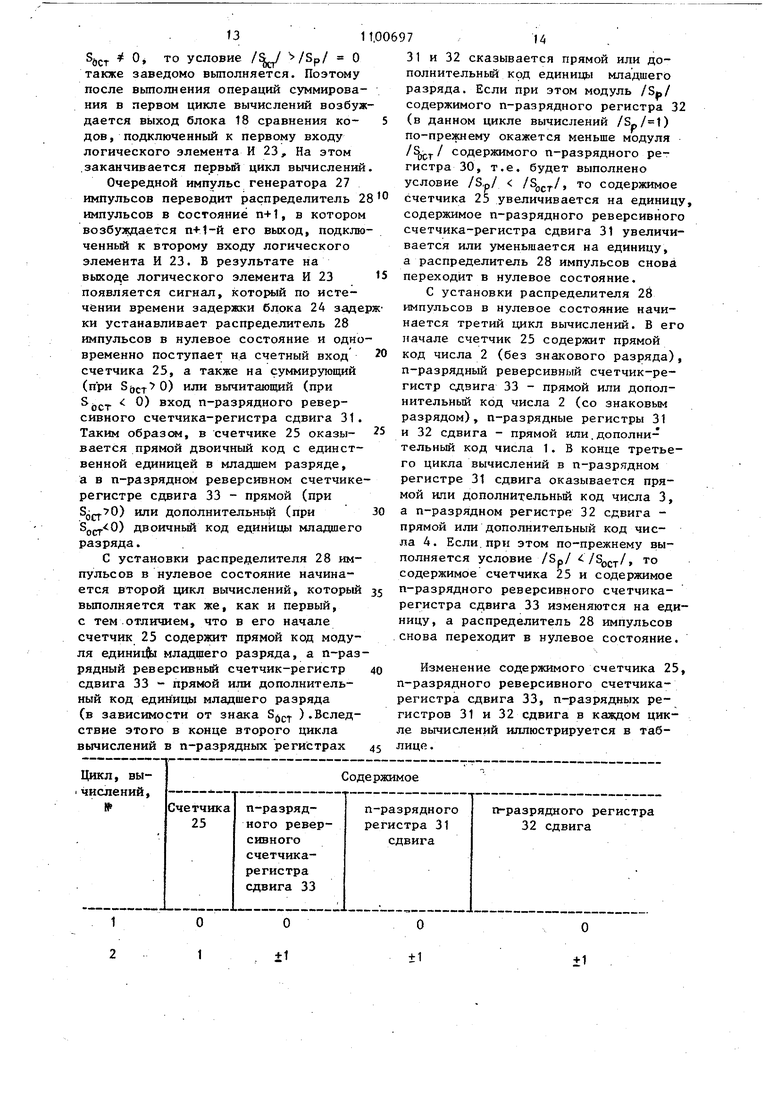

Изменение содержимого счетчика 25, п-разрядного реверсивного счетчикарегистра сдвига 33, п-разрядных регистров 31 и 32 сдвига в каждом цикле вычислений иллюстрируется в таблице. 31 и 32 сказывается прямой или дополнительный код единицы младшего разряда. Если при этом модуль /S,/ содержимого п-разрядного регистра 32 (в данном цикле вычислений ) по-прежнему окажется меньше модуля содержимого п-разрядного регистра 30, т.е. будет выполнено условие IS.nl /SOCT содержимое счетчика 25 увеличивается на единицу. Таким образом, в конце казвдрго цикла пыЧислений модуль содержимого п-разрядного регистра 32 сдвига представляет собой Точный квадрат содержимого счетчика 25 (или п-разрядного реверсивного снетчика-реги стра сдвига 33). Тем самым моделируется квадратичная зависимость межд расчетной скоростью v и расчетным путем Su замедления, необходимая для обеспечения равнозамедленного движения рабочего механизма 6. Точность моделирования этой зависимости определяется числом разрядов в дпоичном представлении величин v- и Sp В соответствии с квадратичной зависимостью между УрИ SP число т-1 разрядов счетчика 25 может быть выбрано равным -у- с округлением до ближайшего- большего целого числа. Описанные циклы вычислений повто.ряются до тех пор, пока вьшолняется условие /SP/ J /SOCT/. при этом содер жимое счетчика 25 (прямой код модуля /VP/ расчетной скорости v-), содержимое п-разрядного реверсивного счетчика-регистра сдвига 33 (прямой или дополнительный код расчетной скорости ур), содержимое п-разрядного регистра 31 сдвига и содержимое п-разрядного регистра 32 сдвига (пря мой или дополнительный код расчетного пути SP замедления) монотонно изменяются. После вьтолнения цикла вычислений, в конце которого условие /SP / оказывается невьшолненным, первый вход логического элемента И 23 не возбуждается и сигнал с (п+1)-го выхода распределителя 28 импульсов на его установочный вход не происходит. В результате распределитель 28 импульсов переходит в свое (п-2)-е состояние. Сигнал с (п+2)-го выхода распределителя 28 импульсов вьшодит прямой код модуля /VP/ расчетной скорости Vp из счетчика 25 в информационные разряды регистра 26, а код знака расчетной скорости VP, совпадающего со знаком оставшегося пути . - из знакового разряда п-разрядного регистра 30 сдвига в знаковый разряд регистра 26. Таким образом, в регистре 26 формируется прямой код расчетной скорости VP со знаковым разрядом. Под действием очередного импульса генератора 27 импульсов распределитель 28 импульсов переходит в состояние п+3. Сигнал с п+З-го выхода распределителя 29 импульсов устанавливает п-разрядный регистр 31 сдвига, п-разрядный реверсивный счетчик 25 в нулевые состояния. На зтом заканчивается первый период вычислений, и распределитель 28 импульсов переходит в свое нулевое состояние, начи

нается второй период вычислений. После окончания второго периода вычислений выполняется третий период и т.д.

В каждом периоде вычислений в регистр 26 вводится код расчетной скосоответствующей текущему РОСТИ Vr значению оставшегося пути 8.,;.Этот код преобразуется цифроаналоговым преобразователем 4 в аналоговую величину, которая масштабируется (умно жается на постоянный коэффициент) в блоке 3 масштабирования и затем огра ничивается в блоке 8 ограничения. До тех пор, пока оставшийся путь и соответственно расчетная скорость VP достаточно велики, с выхода блока 8 ограничения на второй вход регулятора 2 скорости поступает постоянный сигнал, соответствующий максимальной заданной скорости v. и регул тор 2 скорости обеспечи1вает поддержание действительной скорости v на уровне . По мере уменьшения оставшегося пути Spp наступает момент. .начиная с которого монотонно уменьшакяцийся (по модулю) сигнал с выхода блока 3 масштабирования про содит на второй вход регулятора 2 скорости без ограничения. Этот момент являетс моментом начала замедления. В процес се замедления, регулятора 2 скорости обеспечивает изменение действительной скорости V в соответствии с изм нением управляющего сигнала на его втором входе. Тем саьам, реализуется квадратичная зависимость между дейст вительной скоростыо V и оставшимся путем (jf необходимая для реализаци равнозамедленного движения. По мере уменьшения оставшегося пути SMOHOTOHHO уменьшается количество циклов вычислений в каждом очередном периоде вычислений. Когда оставшийся путь S,. становится равны кулю, очередной и все последующие периоды вычислений содержат единственный цикл вычислений, так как при SP сг° ,0 выход блока 18 сравнения кодов не возбуждается и распределитель импульсов 28 из состояния п+1 переходит только в состояние п+2. В каждсм из этих вырожденных периодов вычислений в регистр 26 вводится код нуля,в результате чего на второй вход регулятора 2 скорости поступает нулевой сигнал. Происходит останов

рабочего механизма 6, после чего система может быть выключена.

Таким образом, моделируется квадратичная зависимость между расчетной скоростью VP и расчетным путем S

Р

замедления /Si, / В процессе замедления на втором входе регулятора 2 скорости формиру-, ется управляющий сигнал v,, пропорциональньй расчетной скорости v где К - масштабный коэффи1 иент. С другой стороны, действительная скорость V и оставшийся путь S при равнозамедленном движений связаны соотношением v -2а2оет где а - замедление. В процессе замедления устройство обеспечивает изменение действительной скорости V в соответствии с изменением управляющего сигнала v ,т.е. , , при SP SocT . С учетом V о. V, этого из формулы (2)-(4) следует соотношение 2sign-S c-r Таким образом, величина замедления а зависит от масштабного коэффициента К и может быть установлена настройкой блока 3 масштабирования. Использование изобретения в различных отраслях прс 1ьшшенности обеспечит получение значительного техникоэкономического эффекта. С его помо1цью за счет приближения процесса замедления к оптимальному в смысле быстродействия рг внозамедленному движению и повышения точности останова рабочего механизма быть сокращена лительность рабочих операций и, тем самым, увеличена производительность технологического оборудования. спользование изобретения позволит граничить динамические перегрузки ехнологического оборудования путем оддержания величины замедления а заданном допустимом уровне, тем амым улучшаются характеристики наежности оборудования.

ftv a /fwi/ /)f

Jf

fVfnr}90tfVJH/JOJfAfft1ft/f/

yarftfj fffffvjft t/

ufKtmpf ffUt/ffff ifft/

Лго

w

«H IBMB

«/

.Z

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Филатов А.С | |||

| Электропривод и автоматизация реверсивных станов холодной прокатки | |||

| М., Металлургия, 1973, с | |||

| СПОСОБ ПОЛУЧЕНИЯ ЧИСТОГО ГЛИНОЗЕМА И ЕГО СОЛЕЙ ИЗ СИЛИКАТОВ ГЛИНОЗЕМА, ПРОСТЫХ ГЛИН И. Т.П. | 1915 |

|

SU280A1 |

| Аппарат для электрической передачи изображений без проводов | 1920 |

|

SU144A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство автоматического точного останова электропривода | 1970 |

|

SU482219A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1984-06-30—Публикация

1983-03-05—Подача