Изобретение относигся к импульс-ной технике, а именно к акалого-.дискреткым устройствам.

Известен преобразоваталь цифрово- 5 го кода в частоту, содержащий генератор импульсов эталонной частоты, управляемые делители частоты, схему сравнения, источник образцового временнсгп интервала у. счетчик импуль- IQ сов 1J,

Работа преобразователя заключается 3 подсчете счетчиком п течение заданного зременкого интервала числа импульсов, коступаюшик на его счетный . вход с второго управляемого делителя частоты, и выдачи образовавшегося в счетчике кода на первый упразляеь ый делитель частоты, на выходе которого получают пос.ледовательность . -.-, сов, следующих с частотой, пропорциональной преобразуемому коду.

Недостатком известного преобразователя является низкое быстродайс-гвие jустано ление частоты при иэмене:-:ги величины преобразуемого кода; так как требуется определенное .ремя для набора счетчиком импульсов кода, соответствующего новому значению преобра- . эуемого кода.

Наиболее близким техническим решением к изобретений является также преобразователь цифрового кола в частоту следован1 Я импульсов, содеркащий регистр памяти, счетчик импульсов, динамический триггер, генератор эталонной и допо.г ительной частоты, схему запрета и делитель эталонной частоты. Принцип действ -:я преобразователя заключается к запрете определенного числа импульсов эталон}Юй частоты 2.

Недостат ;ом известного преобразователя является низкая точность преобразования кода в частоту следования импульсов за счет неравномерного, распределения импу.пьсов выходной последовательностт во времени.

Цель изобрете:-:ия - noBHLiieHHe точности преобразования кода в частоту на .основе улучшения распределения импульсов выходной последовательности во времени.

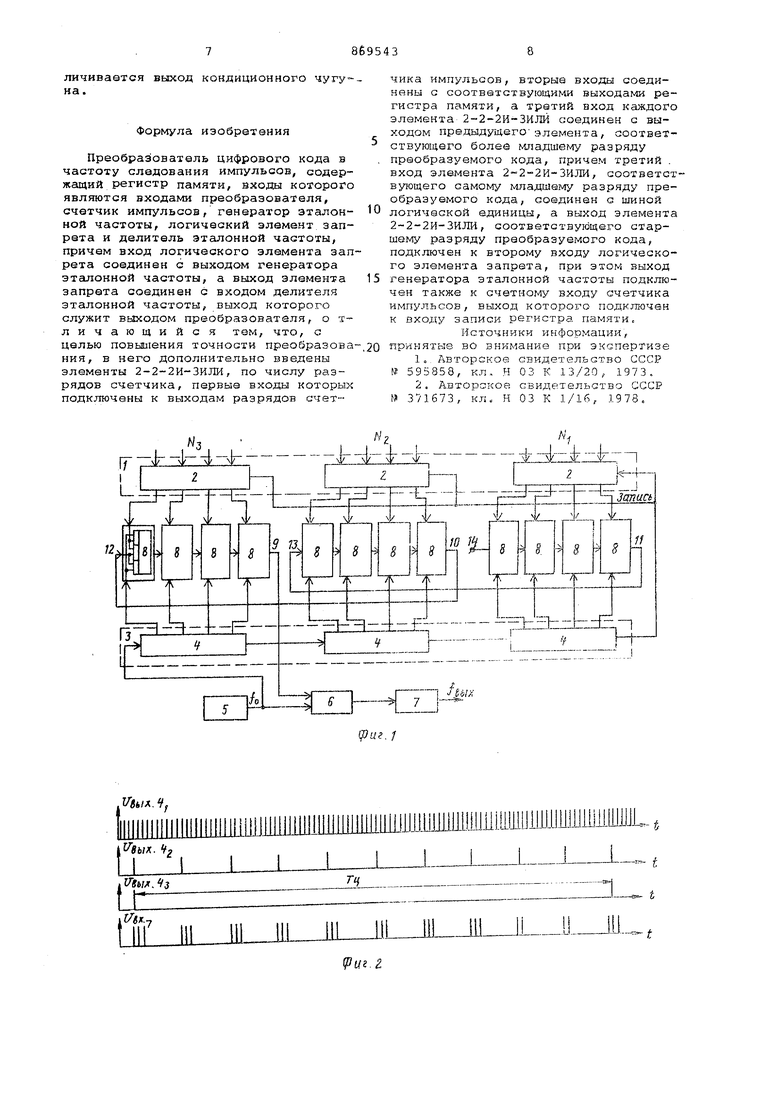

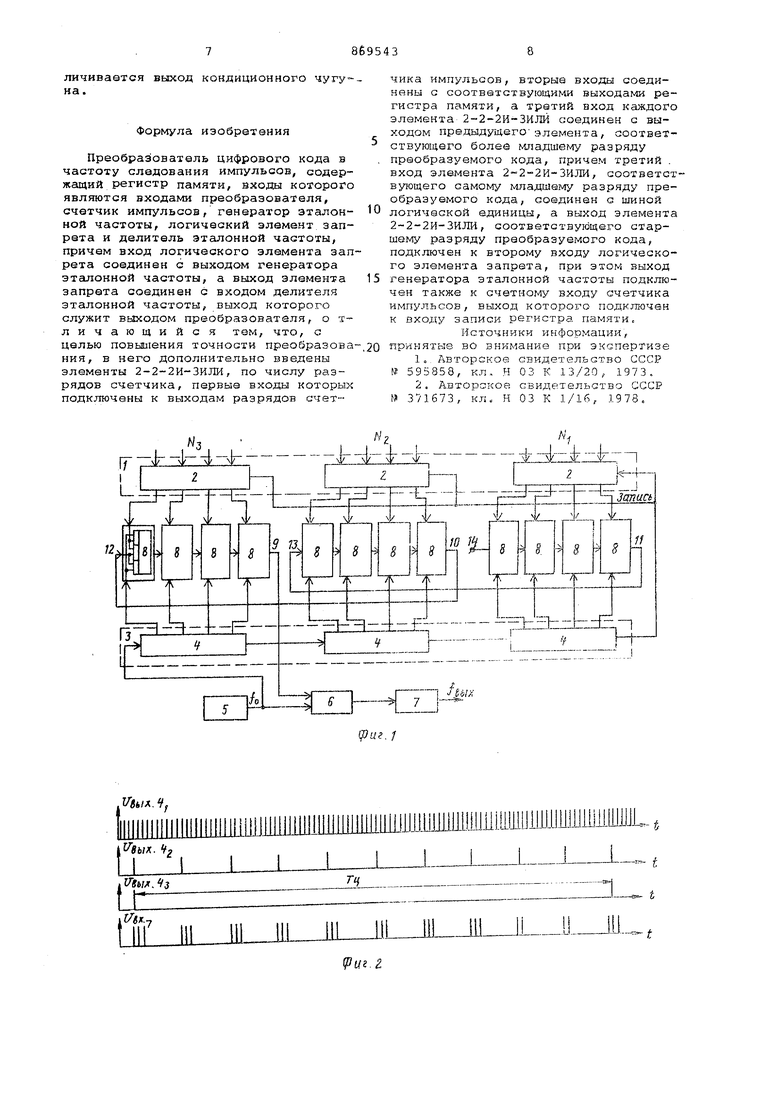

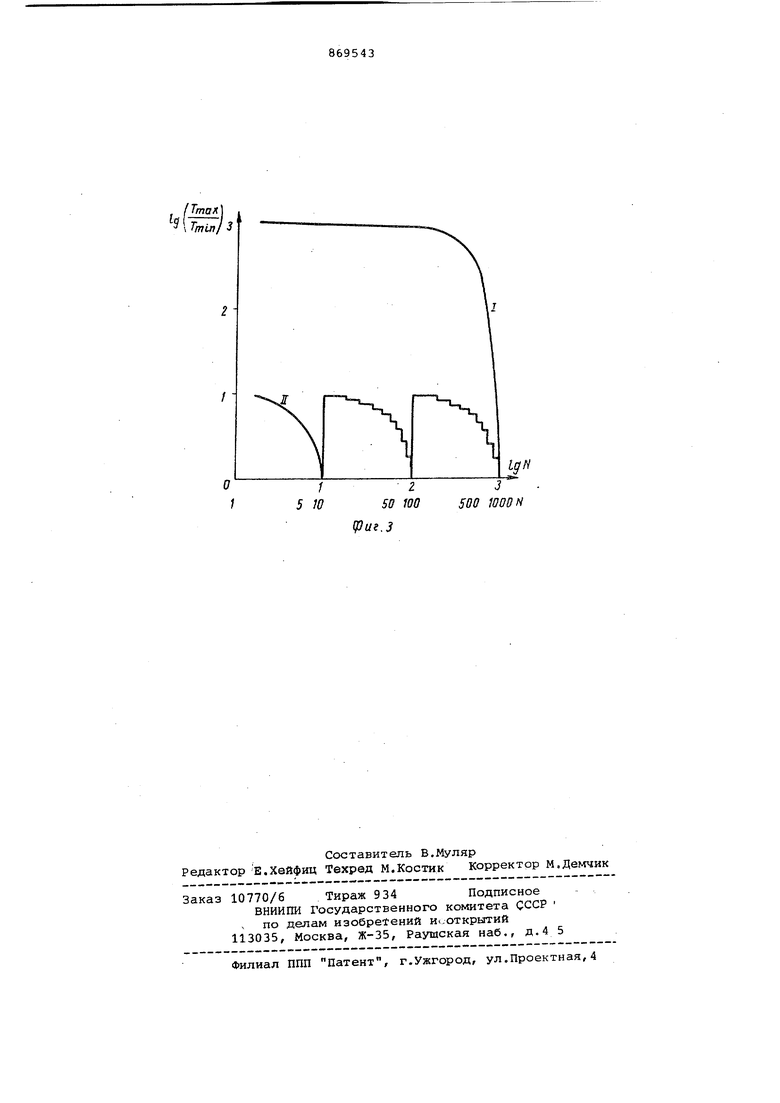

Цель достигается тем,.что в преобразователь цифрового кода в часто: у сле..павания импульсов, содержащий регистр памяти , входы которого являются входами преобразователя, Счетчик им пульсов, генератор эталонной частоты, логический элемент запрета и далитвль эталонной частоты, причем вход логического элемента запрета соединен с выходом генератора эталонной частоты а выход элемента запрета соединен с входом делителя эталонной частоты, выход которого служит выходом преобразователя, введены элементы 2-2-2ИЗИЛИ по числу разрядов счетчика, пер вые входи которых подключены к выходам разрядов счетчика импульсов, вто рые входы соединены с соотватствутощи Ми выходами регистра памяти, а трети Эход каждого элемента 2-2-2И-ЗИЛИ со динен с выходом предыдущего элемент 2-2-2И-ЗИЛИ, соответствующего более младшему разряду преобразуемого код ,причем третий вход самого младшего элемента 2-2-2И-ЗР1ЛИ подк/тачеи к uni не логической единицы, а выход старш го элемента 2-2-211-ЗИЛИ соединен с вторым входом ло1 ического элемента запрета, при этом выхо,ц генератора ,эталонной частоты подключен также к входу счетчи5са импульсов, выход кото рого подктаочен к нхоцу записи регис ,тра памяти . На фиг.1 показаг-а фуик11,;ю:.-:1Л)..Г|Л я схема преобразоватяпя; фиг,2 и 3 иллюстрируют раб01у праобразоыа.ге;(я Преобразовате.пь оо.царжит (,1) регистр 1 памяти, предпазначеиньлй лл хранения преобразуемого кола s дзоично-десятичных ячейках 2,счетчик 3 импульсов, состоящий из двоично-десятичных декад 4, генератор 5 эталон ной частоты, логический элемент 6 запрета, делитель 7 эталонной частоты, предназначенный для улучшения равномерности расстановки импульсов выходной последовательности во време ни, и трехвходовые элементы 8 2-2-2И ЗИЛИ, на одни входы которых поддается обратный код N с регистра 1 памяти, на другие входы элементов 8 подается код со импульсов, вход каждого элемента 2-2-2И-ЗИЛИ соединен с выходом предыдущего элемента 2-2-2И-ЗИЛИ, соответствующего более младшему разряду преобразуемого кода. Логическая на выходе каждого элемента 8 появляется при на личии 1 на любых двух его входах, выходы 9-11 элементов 8, входы 12-14 элементов 8, Преобразуемый пар аллельный код поступает на. вход регистра 1 памяти, который является кодом всего преобра зователя кода в частоту„ Эталонная частота fo с генератора 5 подается н вход логического элемента б запрета и на счетный вход счетчика 3 импульсов, выход которого подключен к шине записи регистра 1 памяти. Обратное значение преобразуемого кода Ч младшего двоично-десятичного разряда Ы сравнивается со значением кода в старшей декаде счетчика 3 импульсов при помощи одной группы эле ментов 8, значение Й-,, сравнивается со значением кода в младшей декаде счетчика 3 импульсов при помощи другой группы элементов 8. Сигнал на выходах 9-11 элементов 8 равен нулю, если код в соответствующих декадах счетчика 3 ч (-i 1,2,3) меньше соответствующего з-начания двоичнодесятичного разряда М.; преобразуемого кеда N, подаваемого на регистр 1 памяти. Момент появления i вы-ходах 9-11 зависит от на/1ичия или отсутствия 1 соответственно на входах 12-14 элементов 8. Если на этих входах сигнал отсутствует, то появляется на выходах 9-11 при достижении кодом соответствующей лека.цы счетчика 3 ямпульсов значения - +1/ если на входах 12--14 этих элементов действует то па соответствующр х выходах 9-1. 1 появляется при Ыг-ч; Ьч Преобразователь работает следующим образом. В начале ка;кдого цикла преобразования код п счетчике 3 иг.1пу.пьсов равен пулю. На входе 12 элемента 8 сигнал отсутствует (если значения г4лалмн.1х ;;йоичпо-лесяткчны}, разрядов fvl,, и к .-, преобразуемого кола W не равнь7 .чулю) и ь:а ее .выходе с;1гнал таз;-же равен нулю. Поэтому логический элемент 6 запрета пропускает импульсы эталонной частоты о на делитель 7, По мере поступления импульсов эталонной частоты на счетный вход декады счетчика 3 импульсов код в ней начинает нарастать от О до 9. При достижении кодом младшей декзль счетчика 3 импульсов величины N.:,,+1 (где JT, - значение старшего двоично-десятичкого разряда преобразуемого кода Ы ) на выходе 9 появи .погический элемент ляется о запрета запрещает прохождение импульсов эталонной частоты fo is леса частоты ±0 код в младшей деггаде счетчика 3 импульсов становится равным нулю, на выходе 9 появляется логический О, и импульсы эталанной частоты fo снова проходят через логический элемент 6 запрета, т.е. на делитель 7 поступают пачки по fj-jj +1 импульсов, следующие с частотой (-, .10, пока на входе 12 элемента 8 не появится . С этого момента на делитель 7 поступают пачки по Nj, импульсов. на входе 12 элеПояБлениемента 8 соответствует тому, что код второй декады счетчика 3 импульсов, нарастающий с частотой Jo/I О, достиг величины Kli + 1 (если значение младшего разряда NK преобразуемого кода не равно нулю). С приходом десятого импульса частоты KOR в этой декаде счетчика 3 импульсов становится .равным нулю, на входе 12 элемента 8 поя ляется логический О,и на делитель 7 снова поступают пачки по Wa+l импульсов. Рассуждая подобным образом, можно проследить работу преобразователя далее, до окончания цикла преобразования, а именно, до обнуления счетчика 3 импульсов. Импульсом переноса старшей декады счетчика 3 импульсов в регистр 1 памяти вновь записывается значение преобразуемого кода, и цикл преобразования повторяется. Про исходит чередование пачек по Ы,, +1 и Kl, импульсов в течение одного цикла преобразования., На выходе делителя 7 эталонной частоты получают последовательность ;с более равномерно распределенными -во времени импульсами, чем у известного преобразователя. Выход делителя 7 является выходом преобразователя. В настоящем преобразователе испол зуется принцип поразрядного анализа преобразуемого кода и текущего значения кода в счетчике импульсов. Результат анализа представляет собой поразрядное разложение преобразуемого VI- разрядного двоично-десятичного кода. Принцип представления преобразуемого кода 3 виде пачек по К1 + 1 и Ыа и импульсов. следующих с частотой So/lO, позволяет равномерно распределить импульсы эталон-ной частоты по периоду преобразования, что позволяет получить на выходе делителя 7 эта лонной частоты последовательность импульсов с более высокой равномерностью распределения импульсов во времени, чем у известного преобразо вателя. Частота на выходе преобразовател равна ьык ,To Nb,---10, Т - период одного цикла преобразова N - емкость счетчика импульсов И - количество двоично-десятичныхразрядов счетчика импульсов; J - период следования импульсов эта лонной частоты; К коэффициент деления делителя эталонной частоты. Коэффициент деления К выбирают в соответствии с выражением: К-- Af где й величина изменения выходной частоты при изменении прео разуемого кода на единицу. С учетом выражения (1) формула (Т) примет вид: При изменении преобразуемого кода от О дoЫ выходная частота изменяется от О до f, где fyyi - максимальная выходная частота, соответствующая коду Ы. Фиг.2 поясняет работу преобразователя кода в частоту,у которого количество двоично-десятичных разрядов счетчика импульсов равно 3 ( ), при значении преобразуемого кодаК ,28. На фиг.2 УВЫХЛ. U(bbiX4-i Обых, мпульсные последовательности наЬыоде младшей, средней и старшей декад, четчика 3 импульсов соответственно; ул импульсная последовательность а входе делителя 7 эталонной частоы. При величине преобразуемого кода 0,28 на делитель 7 эталонной частоты поступают 3 пачки по импульсу, за ними следуют 7 пачек без импульсов, и такое распределение импульсов повторяется 8 раз, а затем следуют 2 пачки по одноь, импульсу и 8 пачек без импульсов, такое распределение импульсов повторяется 2 раза. В следующем цикле преобразование для ,28, происходит аналогнч.ным образом. Оценить неравномерность распределения импульсов во времени можно при помощи отношения Ту,(-,у /Ту-щи , гдеТ1,дх и ThTin .соответственно максимальный и минимальный врег.юнный интервал между двумя соседними импульсами последовательности, подаваемой на делитель 7 эталонной частоты. На фиг,3 приведены кривые, показывающие, как изменяется отношение Тщач/ - У известного (кривая J ) и. данного (кривая) преобразователей, имеющих емкость счетчика Nj -1000 , при изменении величины преобразуемого кода (кривые соединяют точки, соответствующие дискретным значениям кода). Из графика видно, что у данного преобразователя максимальное отношение Туу,о)(, / Т nii и не превышает 10, в то время как у известного преобразователя .( /Т юип ); достигает величины 999, т.е. после деления выходная импульсная последовательность у данного преобразователя будет более равномерно распределена во времени. Использование данного преобразователя в качестве узла устройства для дозирования позволяет повысить точ- . ность дозирования сыпучих материалов например кокса в доменном производстве. При повьгшении точности дозирования улучшается тепловой режим доменной печи, экономится топливо, уналичиваатся выход кондиционного чугуна.

Формула изобретения

Преобразователь цифрового кода в частоту следования импульсов, содержащий регистр памяти, входы которого являются входами преобразователя, счетчик импульсов, генератор эталонной частоты, логический элемент запрета и делитель эталонной частоты, причем вход логического элемента зап рета соединен с выходом генератора эталонной частоты, а выход элемента запрета соединен с входом делителя эталонной частоты, выход которого служит выходом преобразователя, о тличающийся тем, что, с целью повышения точности преобразования, в него дополнительно введены элементы 2-2-2И-ЗИЛИ, по числу разрядов счетчика, первые входы которых подключены к выходам разрядов счетчика импульсов, вторые входы соединены с соответствующими выходами регистра памяти, а третий вход каждого элемента 2-2-2И-ЗИЛИ соединен с выходом предыдущегоэлемента, соответствующего более MJsaflmsMy разряду преобразуемого кода, причем третий . вход элемента 2-2-2И-ЗИЛИ, соответствующего самому младшему разряду преобразуемого кода, соединен с шиной логической единицы, а выход элемента 2-2-2И-ЗИЛИ, соответствующего старшему разряду преобразуемого кода, подключен к второму входу логического элемента запрета, при этом выход генератора эталонной частоты подключен также к счетному входу счетчика импульсов, выход которого подключен к входу записи регистра памяти,

ИсточЕ1ики информации f 20 принятые во внимание при экспертизе

1,Авторско© свидетельство СССР № 595858, к.п, Н 03 К 13/20, 1973.

2.Авторское свидетельство СССР № 371673, кл. Н 03 К 1/16, 1978,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь цифрового кода в частоту следования импульсов | 1983 |

|

SU1169170A1 |

| Устройство для измерения температуры | 1982 |

|

SU1081438A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Цифро-аналоговый преобразователь с автоматической коррекцией нелинейности | 1980 |

|

SU930651A2 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1980 |

|

SU970354A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1977 |

|

SU898417A2 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

.. f, тштт тжттш I I l StlJt. Чз ттттттт т1,, ., ZIIIJ 1ZZZI fe jLj jiу и.„,

Авторы

Даты

1983-01-15—Публикация

1980-04-10—Подача