J

ч чэ

ч

CN ГО

Изобретение относится к радиотехнике и вычислительной технике и может использоваться в системах передачи дискретной информации различного назначения.

Известно устройство для преобразования троичного кода в двоичный, содержащеедетекторы импульсов, преобразователи уровня, элементы И, элементы И, элементы ИЛИ и элементы НЕ, которое обеспечивает преобразование троичного кода (+1; 0; -1) в двоичный код (1; 0) по заданному алгоритму (2Т ) с восстановлением номинальной скорости передачи символов исходной двоичной последовательности,

Недостатком известного технического решения является то, что оно не обеспечивает возможности декодирования многопо- зиционных временных кодов с детерминированным сдвигом импульсов внутри тактового интервала Т, что не позволяет использовать его, например, при деко дировании многопозиционных сигналов.

Наиболее близким к заявляемому является преобразователь четырехпозиционно- го временного кода в двоичный код, содержащий первый и второй детекторы импульсов, генератор импульсов, двоичный счетчик, первый-пятый элементы ИЛИ, преобразователь уровня, элемент запрета, выделитель тактовой частоты, первый-третий элементы НЕ, умножитель частоты, первый- третий элементы задержки и первый-чет- вертый элементы И, который обспечивает декодирование разнополярных четырехпо- зиционных сигналов с одинаковой длительностью импульсов (Т2/2) в тактовом интервалеТ2 2Т1, где Ti -длительность тактового интервала исходной двоичной последовательности.

Существенным недостатком известного устройства является то, что оно не обеспечивает возможности декодирования разно- полярных четырехпозиционных сигналов с различной длительностью импульсов (Т2/2 иТ2)с раздельным чередованием полярно- стей импульсов по их длительности.

Цель изобретения - расширение области применения преобразователя путем обеспечения приема сигналов с различной длительностью импульсов в результате изменения алгоритма декодирования.

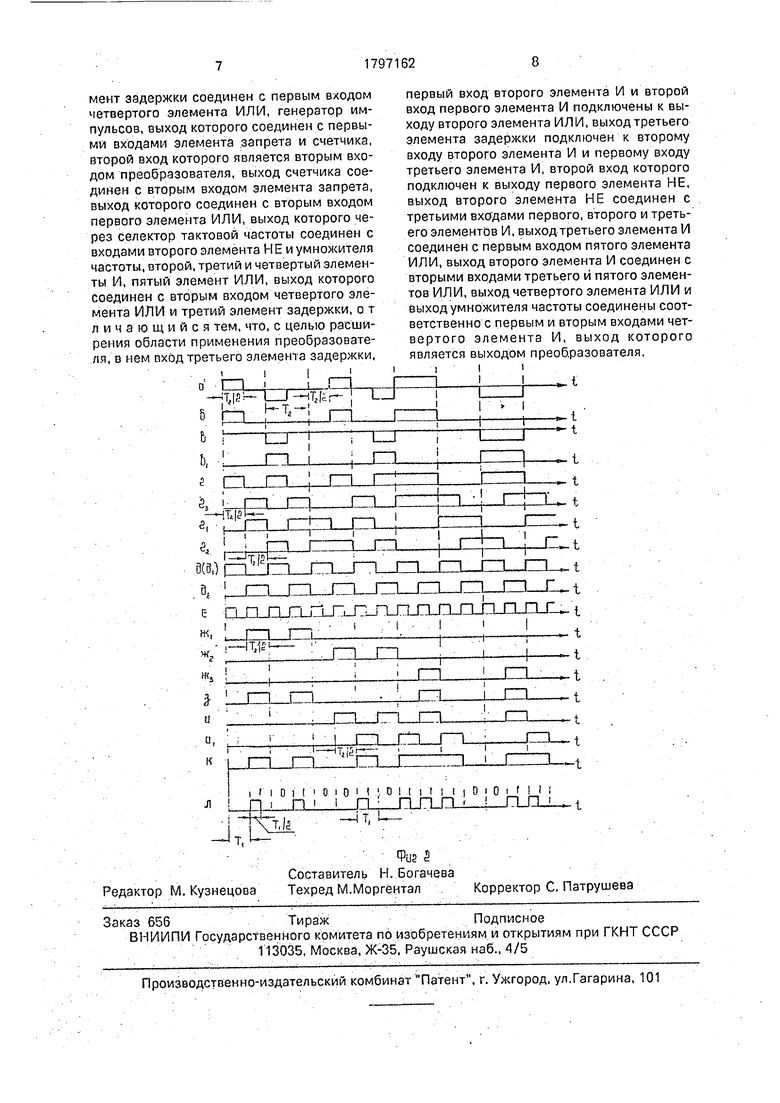

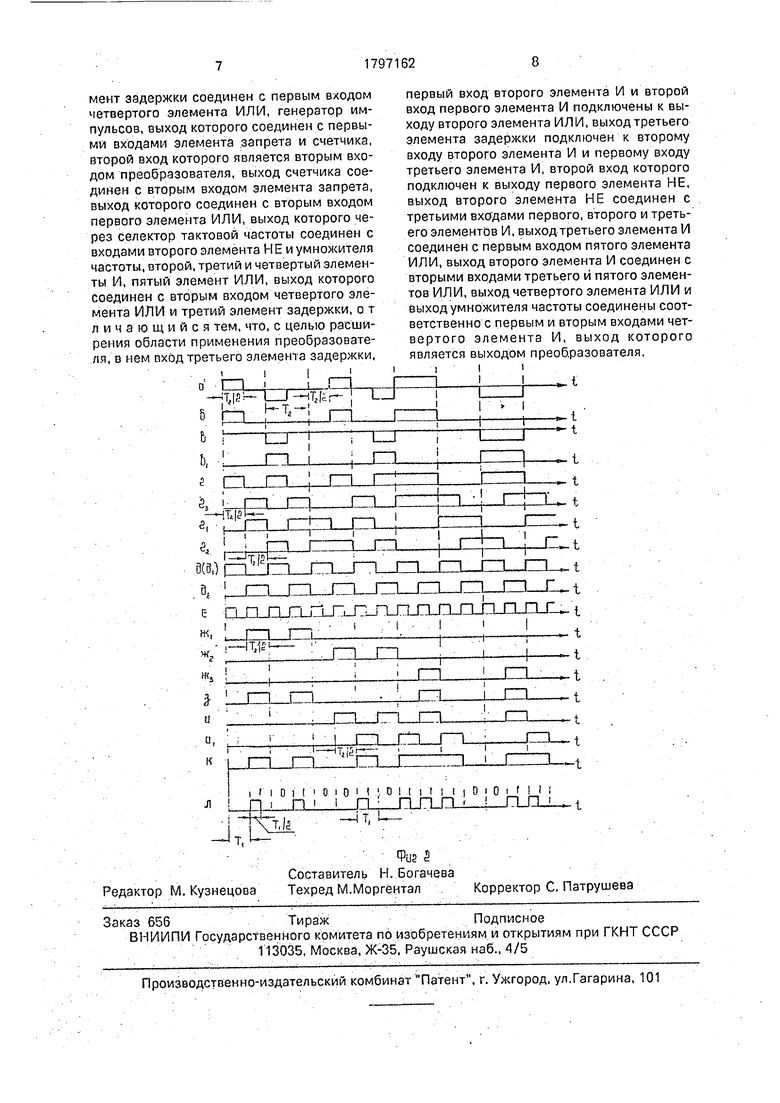

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - Беременные диаграммы.

Предлагаемый преобразователь содержит (фиг. 1) детекторы 1 и 2 импульсов, генератор 3 импульсов, двоичный счетчик 4, первый элемент 5 ИЛИ, преобразователь б уровня, элемент 7 запрета, селектор 8 тактовой частоты, второй элемент 9 ИЛИ, второй элемент 1Q НЕ, умножитель 11 частоты, первый элемент 12 НЕ, третий и первый элементы 13.14 задержки, третий, первый и

второй элементы 15,16,17 И, пятый и третий элементы 18 и 19 ИЛИ, второй элемент 20 задержки, четвертые элементы 21 и 22 ИЛИ и И.

Преобразователь четырехпозиционно0 го временного кода в двоичный код работает следующим образом.

После включения электропитания преобразователя сигнал начального сброса, вы- работанный внешним устройством,

5- устанавливает двоичный счетчик 4 в исходное состояние путем подачи единичного потенциала на его установочный вход. При этом с выхода генератора импульсов 3 через последовательно соединенные открытый

0 элемент запрета 7 и элемент ИЛИ 5 на вход выделителя тактовой частоты (ВТЧ) 8 поступает последовательность тактовых импульсов с длительностью Т2/2, следующих с номинальной тактовой частотой

5 (фиг. 2, д), которая обеспечивает запуск и синхронизацию ВТЧ,

С выхода генератора 3 последовательность тактовых импульсов поступает одновременно на вход двоичного счетчика 4,

0 который после окончания установленного счета импульсов переполняется и единичным потенциалом со своего выхода, поступающим на инверсный вход элемента запрета 7, закрывает последний, что пред5 отвращает прохождение через него импульсов с выхода генератора и обеспечивает работу ВТЧ в автономном режиме.

Перед началом приема информационного массива на вход устройства поступает

0 синхросигнал тактовой частоты с длительностью импульсов Т2/2 (меандр), передние фронты импульсов в котором совпадают с началом тактового интервала Т2, что обеспечивает работу ВТЧ в режиме синхронизации

5 входной последовательностью импульсов, поступающей на вход устройства.

При этом равнополярный четырехпози- ционный сигнал с длительностью импульсов Т2/2 и Т2, следующих с номинальной такто0 вой частотой F2, сформированный по заданному алгоритму (2В 1Т) и передние фронты импульсов в котором совпадают с началом или с серединой тактового интервала Т2 (фиг, 2, а) поступает на входы детекторов

5 импульсов 1 и 2, с помощью которых разделяется соответственно на последовательности положительных (фиг. 2, б) и отрицательных (фиг, 2, в) импульсов, а также поступает через элемент ИЛИ 5 на вход селектора тактовой частоты 8 и обеспечивает

его работу в режиме синхронизации входной последовательностью импульсов.

Затем последовательность положительных импульсов с выхода детектора 1 (фиг. 26) поступает к первому входу элемента ИЛИ 9, а последовательность отрицательных импульсов с выхода детектора 2 подается ко входу преобразователя уровня б, обеспечивающего преобразование отрицательных импульсов (фиг. 2, в) в положительные (фиг. 2, BI)C выхода которого последние поступают ко второму входу элемента ИЛИ 9, на выходе которого формируется однопо- лярный сигнал (фиг. 2, г), который поступает через элемент НЕ 12 (фиг, 2, п) к первому входу элемента И 15, а через последовательно соединенные элементы НЕ 12 и элемент задержки 14 на величину Та/2 (фиг. 2, га) - к первому входу элемента И 16.

Сигнал с выхода элемента ИЛИ 9 (фиг. 2, г) ко второму и первому входам элементов И 15 и 17 поступает соответственно через элемент задержки 13 на величину Та/2 (фиг. 2, гз), а ко вторым входам элементом И 16 и 17 непосредственно, причем на третьи входы элементов 1/115-17 поступает последовательность тактовых импульсов с выхода выделителя тактовой частоты 8 (фиг. 2, Д1), через элемент НЕ 10 (фиг. 2, д-i), в результате чего на выходе элементов И 1.5-17 формируются во второй половине тактового интервала Та импульсы с длительностью Та/2 (фиг. 2, Ж1-жз).

С выхода элементов И 15 и 16 сигналы (фиг, 2, Ж1, жа) поступают соответственно к первым входам элементов ИЛИ 18 и 19, на вторые входы которых сигнал подается с выхода элемента И 17 (фиг. 2, жз), в результате чего на выходе элементов ИЛИ 18 и 19 формируются соответственно во второй половине тактового интервала Та импульсы с длительностью Та/2 (фиг. 2з, и).

.Сигнал с выхода элемента ИЛИ 18(фиг, 2, з) поступает к первому входу элемента ИЛИ 21, на второй вход которого сигнал с выхода элемента ИЛИ 19 (фиг. 2, и) подается

через элемент задержки 20 на величину Та/2 (фиг. 2, HI), причем сигнал с выхода элемента ИЛИ 21 (фиг. 2, к) поступает к первому входу элемента И 22, на второй вход которого с выхода умножителя 11 частоты 1x2 (фиг. 2, е), вход которого подключен к выходу селектора 8 (фиг. 2, д-i) подается последовательность тактовых импульсов с длительностью Ti/2, в результате чего на выходе элемента И 22 восстанавливается

исходная двоичная последовательность с длительностью импульсов Ti/2 в тактовом интервале Ti, следующих с номинальной тактовой частотой /Ti (фиг. 2, л),

Практическая реализация заявляемого

устройства выполнена, в основном, на элементах логики (И, ИЛИ, НЕ), генераторе импульсов 3, двоичном счетчике 4, селекторе тактовой частоты 8.

В качестве детекторов импульсов 1 и 2

могут быть использованы диоды, включенные соответственно в прямом и обратном направлениях.

Преобразователь уровня 6 может быть реализован на операционном усилителе с

обратной связью с использованием инвертирующего входа.

Элемент запрета 7 представляет собой двухвходовый элемент И с инвертирующим одним входом.

Элемент задержки (13, 14, 20) может

быть реализован на одновибраторе с регулируембй времязадающей цепочкой RC с

переменным резистором R, включенной в

цепи его запуска.

Таким образом, предложенное устройство для преобразования четырехпозицион- ного временного кода в двоичный код обеспечивает декодирование разнополяр- . ных четырехпозиционных сигналов с длительностью импульсов Та/2 и Та со строгим чередованием полярностей импульсов по их длительности, что расширяет его область применения, путем изменения алгоритма декодирования и соответствует достижению поставленной цели.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в четырех-позиционный временной код | 1990 |

|

SU1757104A1 |

| Преобразователь восьмипозиционного временного кода в двоичный код | 1990 |

|

SU1771070A1 |

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1646068A1 |

| Преобразователь двоичного кода в четырехпозиционный код | 1988 |

|

SU1594703A1 |

| Устройство для передачи и приема дискретной информации | 1990 |

|

SU1807579A1 |

| Устройство для двухкратного уплотнения каналов связи | 1991 |

|

SU1775871A1 |

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОМАНИПУЛИРОВАННОГО КОДА В БИНАРНЫЙ КОД | 1999 |

|

RU2163418C1 |

| Устройство для уплотнения каналов связи | 1990 |

|

SU1809544A1 |

| Преобразователь кода | 1989 |

|

SU1612376A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 1990 |

|

RU2022453C1 |

Изобретение относится к радиотехнике и вычислительной технике и может использоваться в системах передачи дискретной информации различного назначения. Уста ройство обеспечивает преобразование раз- нополярного 4-х позиционного сигнала с длительностью импульсов Т2/2 и Та со строгим чередованием полярностей импульсов по их длительности в исходный двоичный сигнал, что достигается в результате декодирования принимаемых символов по уровню, длительности и временному положению импульсов внутри тактового интервала Т2. Преобразование 4-х позиционного временного кода в двоичный код обеспечивается с помощью генератора 3 импульсов, селектора 8 и умножителя 11 тактовой частоты, элементов И 15, 16, 17,22. ИЛИ 5, 9, 18.19,21, НЕ 10, 12 элементов задержки 13. 14, 20, двоичного счетчика 4, детекторов 1, 2 импульсов, элемента запрета 7 и преобразователя 6. 2 ил. (Л С

Формула изобретён и я Преобразователь четырехпозиционио- го временного кода в двоичный код, содержащий первый и второй детекторы уровня, входы которых объединены с первым входом первого элемента ИЛИ и являются первым входом преобразователя, выход перво го детектора уровня соединен с первым входом второго элемента ИЛИ, выход

второго детектора уровня через преобразователь уровня соединен с вторым входом второго элемента ИЛИ, выход которого соединено входом первого элемента НЕ, выход которого через первый элемент задержки соединен с первым входом первого элемента И, оыход которого соединен с первым входом третьего элемента ИЛИ, выход третьего элемента ИЛИ через второй элемент задержки соединен с первым входом четвертого элемента ИЛИ, генератор импульсов, выход которого соединен с первыми входами элемента запрета и счетчика, второй вход которого является вторым входом преобразователя, выход счетчика соединен с вторым входом элемента запрета, выход которого соединен с вторым входом первого элемента ИЛИ, выход которого через селектор тактовой частоты соединен с входами второго элемента НЕ и умножителя частоты, второй, третий и четвертый элементы И, пятый элемент ИЛИ, выход которого соединен с вторым входом четвертого элемента ИЛИ и третий элемент задержки, о т ли чающийся тем, что, с целью расширения области применения преобразователя, в нем пход третьего элемента задержки,

ti | .I.,, 11 .,

i

-1т.и

Составитель

Редактор М.Кузнецова ТехредМ.Моргентал

первый вход второго элемента И и второй вход первого элемента И подключены к выходу второго элемента ИЛИ, выход третьего элемента задержки подключен к второму входу второго элемента И и первому входу третьего элемента И, второй вход которого подключен к выходу первого элемента НЕ, выход второго элемента НЕ соединен с третьими входами первого, второго и третьего элементов И, выход третьего элемента И соединен с первым входом пятого элемента ИЛИ, выход второго элемента И соединен с вторыми входами третьего и пятого элементов ИЛИ, выход четвертого элемента ИЛИ и выход умножителя частоты соединены соответственно с первым и вторым входами четвертого элемента И, выход которого является выходом преобразователя, iii

Фиг 5 Н. Богачева

гентал

Корректор С. Патрушева

| СИНТЕТИЧЕСКИЙ ПОЛИ-IGA-КОМПЛЕКС, БЕЛОК, СПОСОБ ПОЛУЧЕНИЯ КОМПЛЕКСА, СПОСОБ ТЕСТИРОВАНИЯ, СПОСОБ ЗАЩИТЫ | 1991 |

|

RU2124050C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Преобразователь четырехпозиционного временного кода в двоичный код | 1988 |

|

SU1599994A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-02-23—Публикация

1990-12-17—Подача