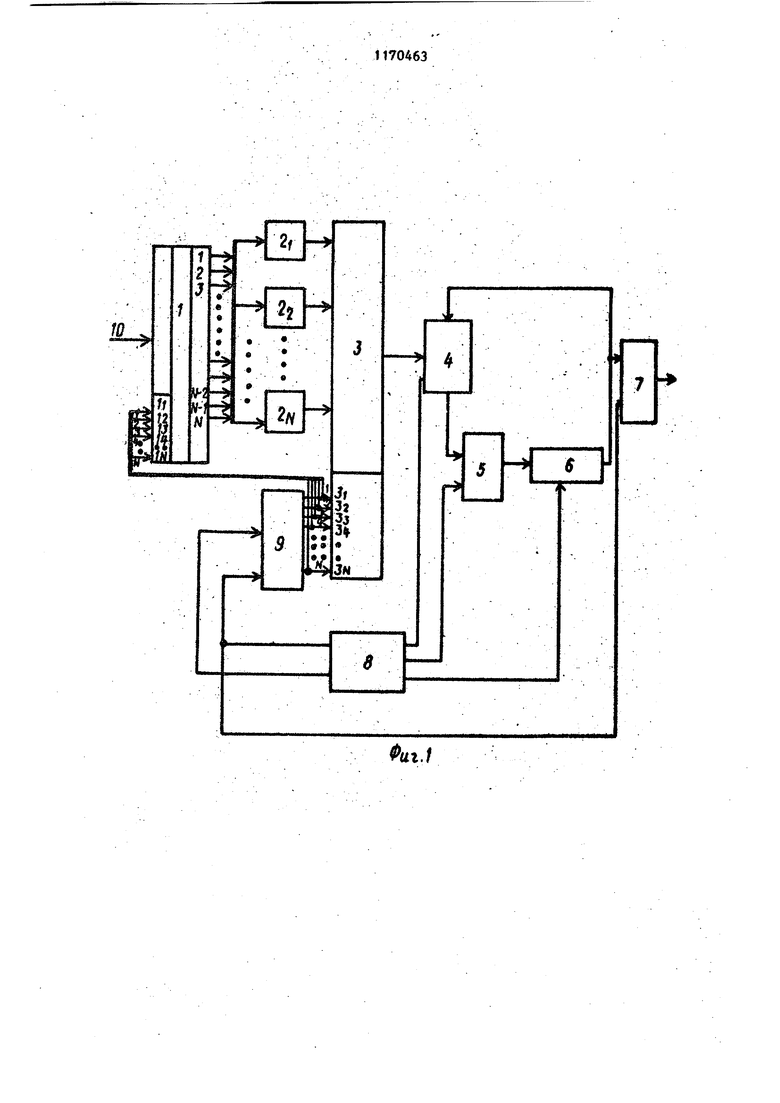

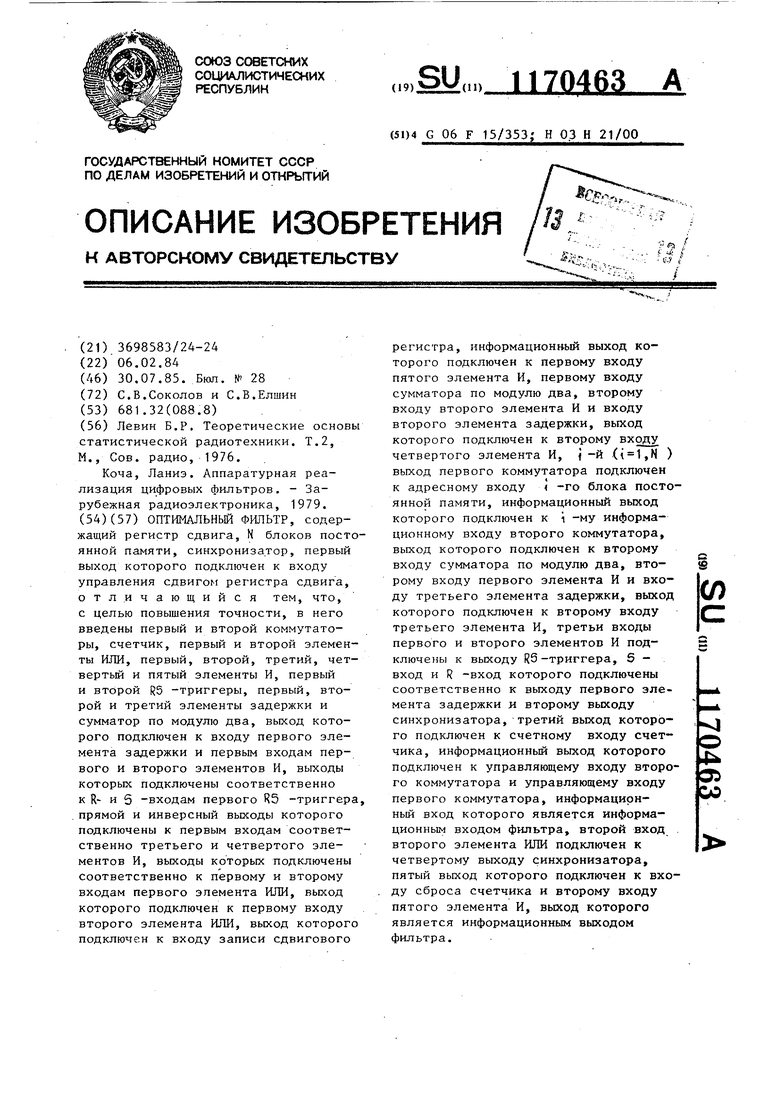

I 1 Изобретение относится к специализированной вычислительной техинке и может быть испорьзавано в стохастических оптимальных системах автоматцческого упрааления и вычисли тельных сетяХо Цель изобретения - повьппение . точности фильтрации. . . . Для синтеза оптимального фильтра используются особенности-распределения наименьшего числа .из выборки . случайных величин с произвольным распределением. , .Синтез фильтра осуществляем таким образом, чтобы случайная последова™ тельность У на входе синтезируемого фильтра с N -мерной симметрической функцией распределения Р-(У, , У2 ,.. У) бьша преобразована так, чтобы распределение процесса на выходе фи-пьтра X бьшо оптимальньм в см-ысл критерия „ „ max и В j , . . Пределы А, В,, а также функцию Р полагают известными, Р(х) е 0,rj, ,до. ,Из теории порядковых статистик известно, что .где А(, , У-,- 1-я порядковая статистика в выборке объема I так как Р - а Р()-Р(У, , У2,,..,У . Р.(УЭ У ...jy) в силу сделанных предположений (причем Р(.,.) по условиям задачи известна), то .АДРт18,В,,..8)-р,(А,А,,,. На основании данного выражения noMomj K) мультипликативного X (У, d) преобразования с последующ выделением на выходе филь ра значе ния X U достигается выполнение г 7 условия max ВJ.для вновь об разованной выходной последовательности (некоторого функционального преобразования входной последовательности) X кт1п1,Д,-4,.-. т.е. каждое значение последовательности Yj умножается на некото рута величину . Осуществляется операция покоординатного произведения 5 при этом 3 ;l --«i-l/ hi5..T-t) о I ,Т, а;;у.; При выборе значений для обеспечения max Р АД 5В уравнения для определения d имеют вид v-A .АГр (J-A IV .,,d,-dm|. -P-llr-ffl б 6-i tfmU Очевидно, что при полном преобразовании выборки объема Х1 входной последовательности У для нахождения N неизвестных значений d: необходимо N равнении, T.e.i Данные уравнения легко решаются звестными численньши-метода 1И5. т, а, ucl H--bW.(M,M,..-M, OOlL. ,..-.,cIikO,,,... -М1. . . . . : На фиг.1 изображена фу-нкциональнан схема оптимального фильтра, на фиг,2 - функциональная схема блока . выделения-наименьшего числа. Фильтр () содержит г коммутатор 1, i блоков 2., 2 , .,.s2fj постоянной памяти, коммутатор 3, блок выделения наименьшего числа 4j, элемент ИЛИ 5, сдвиговый регистр 6, элемент И 7, синхронизатор 8, счетчик 9, информационный вход 10. Блок 4 выделения наименьшего числа (фиг.2) включает первый 11 и второй 12 вход, сумматор 13 по модулю два элементы И 14 и 15, элемент 16 за держки, элемент И 1.7, элемент 18 задержки, элемент И 19, элемент задержки 20, R3-триггер 21, тактовый вход 22, R6 -триггер 23, элемент ИЛИ 24.. Фильтр работает следующим обра- зрм. Случайная пос.педовательность с известнь М распределением поступает на вход KotviMyTaTopa Nxl 1, который является одновременно входом 10 устройства. Управление коммутацией входа to осуществляется с выходов счетчика 9, на счетный вход 9 которого поступают счетные импульсы с выхода синхронизатора. На i -м выходе 3 коммутатора 1 появляется i -е значе ние входной последовательности в вы борке заданного объема N , поступа ющее на вход соответствующего блока постоянной памяти 2 . , 2,, ,, ,2 ., В блоке 2 j происходит умножение двоичного числа на величину d. С в хода 1-го блока 2j преобразованная двоичная последовательность в после довательном коде поступает на i -и вход коммутатора 3. Синхронизатор 8 выдает на счетны вход счетчика 9 выхода управляющие импульсы, период следования которых равен времени прохождения через ком мутатор 3 одного двоичного М-разрядного числа в последовательном коде. Код с выходов счетчика 9 поступа ет на управляющий вход коммутатора, определяя последовательную его коммутацию входов ,...,N. Минимальная разрядность К счетчика 9 должна быть равна К + l, где f. знак целой части числа. Кроме того, код с выхода счетчика 9 поступает на входы управления коммутацией коммутатора 1, определя соответствие коммутируемьк входов коммутатора 3 и выходов коммутатора 1 . С выхода коммутатора 3 двоичное М-разрядное число поступает последо вательным кодом на первый вход блока 4 выделения наименьшего числа На второй вход блока 4 вьщеления наименьшего числа с выхода последовательного М-разрядного сдвигового регистра -6 поступает второе М-разрядное двоичное число в последовательном коде (в начальный момент в регистре 6 записан единичный код). В блоке 4 выделения наименьшего числа происходит выбор наименьшего из двух входных чисел, при этом вы{бранное наименьшее число записывается последовательным кодом в сдвиговый регистр 6, поступая на его вход записи с выхода блока 4 выделе ния наименьшего числа через элемент .ИЛИ 5. Запись в сдвиговый регистр 6 и сдвиг записанного числа осуществляется синхронно по приходу управляющих импульсов с выхода синхрониз тора 8, период следования которых равен периоду кодовых импульсов, входных последовательностей. 634 Для записи наименьшего числа в сдвиговый регистр 6 после сравнения с ранее записанным число рабочих синхроимпульсов с выхода синхронизатора 8 должно быть равно М+т, где m - целое число-, JTij где At - период кодовых импульсов; D - .задержка сигнала в блоке 4 вьщеления наименьшего числа. После сравнения двух чисел с выхода синхронизатора 8 формируется тактовый импульс, п.оступающий на тактовый вход блока 4 вьщеления наименьшего числа: и подготавливающий его к следующему сравнению. Через время формирования Т -го импульса на выходе синхронизатора 8, где Т определяется моментом записи выбранного в N -м цикле сравнения. наименьшего числа в сдвиговый регистр 6, с выхода синхронизатора 8 формируется единичный сигнал, посту пающий на вход сброса счетчика 9 и сбрасывающий счетчик 9 в нулевое состояние, а также поступающий на вход элемента И 7-. После этого с выхода синхронизатора 8 формируется М сдвигающих импульсов, обеспечивающих прохождение записанного в регистре 6 случайного числа на выход устройства через элемент И 7. После окончания вывода числа на выходе синхронизатора 8 вновь появляется нулевой .сигнал, на пятом выходе 8j - единичный, и формируется снова М управлякяцих импульсов на выходе синхронизатора 8, обеспечивающих запись в сдвиговый регистр 6 через элемент ИЛИ 5 единичного кода, после чего процедура выбора наименьшего числа из выборки объема N повторяется. Блок 4 вьщеления наименьшего числа работает следующим образом. С входов 11 и 12 два М-разрядных двоичньгх числа поступают последова- т.ельными кодами, начиная со старших разрядов. С входа 11 разряд первого числа поступает на вход элемента И 14, на первый вход сумматора 13 по модулю два и через элемент 16 заержки на вход элемента И 17. Аналогично с входа 12 разряд второго числа поступает на вход элемента И 15, на вход сумматора 13 по модулю два и через элемент 18 заержки на вход элемента И 19.

случае неравенства разрядов с выхода сумматора: 13-по модулю два снимается единичный сигнал, поступаюпщй на входы элементов И 14 и 15 и через элемент 20 задержки на 5 -вхо R5 -триггера 21. При поступлении каждой новой пары чисел формируется тактовый импульс на тактовом входе 22, определяющий нулевое состояние R5 -триггера 21 (1 на нулевом выходе) .

Таким образом, с Того выхода элементов И 13 или 15, на вход которого поступил большой разряд (т.е. 1), снимается единичный сигнал, преводящий R5 -триггер 23 в нулевое или единичное состояние соответственно. Через время, определяемое временем от момента появления единичного сигнала на выходе сумматора 13 по модулю два до момента начала срабатывания R5 -триггера 23 на S входе R5 -триггера 21, появляется с выхода элемента 20 задержки единичный сигнал, переводящий. RS -триггер 21 в единичное состояние и запрещающий дальнейшее формирование управляющих (единичных) сигналов на входах R5-триггера 23 (время задерж в элементе задержки фактически должно быть равно времени срабатывания элемента И), тем самым на выходах элементов И 14 или 15 появляется единичный сигнал лишь, при первом по явлении неравенства разрядов,-приче на выходе того элемента И, на вход которого поступает больший разряд (1) с входа блока.

Нулевой (единичный) сигнал с одкого из выходов R5 -триггера 23 поступает на вход одного из элементов И (с единичного выхода - на вход

элемента И 17, с нулевого выхода ,на вход элемента И 19), запрещая тем самым прохождение через него последовательности, поступающей с входа 11 (12) через элемент задержки 16 (18).

Время задержки определяется интервалом времени от момента появления разряда на входе 11 (12) до момента срабатывания R5 -триггера 23 в случае несравнения разрядов.

По окончании сравнения первой пар чисел на входе 22 формируется тактовый импульс (регулируя время его формирования, получаем возможность регулировать разрядность сравниваемых чисел), переводящий RS -триггер 21 в нулевое состояние и подготавливающий тем самым разрешение на следующее формирование управляемых сигналов на входах RS -триггера 23 в случаенесравнения разрядов.

До момента несравнения р.азрядов состояние R5 -триггера 23 не имеет значения - на один из входов элемента ИЛИ 24 разрешено прохождение через элемент И 17 (19) разрядов одной из последовательностей. Выбор последовательности до момента несравнения разрядов не имеет значения. Таким образ.ом, на выходе элемента ИЛИ 24 формируется наименьшее из двух сравниваемых чисел в последовательном коде.

. Выбор числа N коэффициентов d,, j 1,2,...,Ц, рассчитанных заранее, осуществляется с учетом вьгаислнтельных затрат.

Таким образом, предлагаемый фильтр обладает большей точностью фильтрации за счет оптимизации исходной функции распределения.

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения центра массы плоской фигуры | 1985 |

|

SU1249541A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Цифровой вероятностный фильтр | 1985 |

|

SU1295507A1 |

| Цифроаналоговый преобразователь | 1983 |

|

SU1152091A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2019 |

|

RU2713624C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР | 1973 |

|

SU387370A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

ОПТИМАЛЬНЫЙ ФИЛЬТР, содержащий регистр сдвига, N блоков постоянной памяти, синхронизатор, первый выход которого подключен к входу управления сдвигом регистра сдвига, отличающийся тем, что, с целью повышения точности, в него введены первый и второй коммутаторы, счетчик, первый и второй элементы ИЛИ, первый, второй, третий, четвертый и пятый элементы И, первый и второй R5 -триггеры, первый, второй и третий элементы задержки и сумматор по модулю два, выход которого подключен к входу первого элемента задержки и первым входам первого и второго элементов И, выходы которых подключены соответственно к R- и 5 -входам первого R5 -триггера, прямой и инверсный выходы которого подключены к первым входам соответственно третьего и четвертого элементов И, выходы которых подключены соответственно к первому и второму входам первого элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ, выход которого подключен к входу записи сдвигового регистра, информационный выход которого подключен к первому входу пятого элемента И, первому входу сумматора по модулю два, второму входу второго элемента И и входу второго элемента задержки, выход которого подключен к второму входу четвертого элемента И, j -и (,N ) выход первого коммутатора подключен к адресному входу -го блока постоянной памяти, информационный выход которого подключен к i -му информационному входу второго коммутатора, выход которого подключен к второму входу сумматора по модулю два, второму входу первого элемента И и вхосл ду третьего элемента задержки, выход которого подключен к второму входу третьего элемента И, третьи входы первого и второго элементов И подключены к выходу R5-триггера, 6 - вход и R -вход которого подключены соответственно к выходу первого элемента задержки и второму выходу синхронизатора, третий выход которого подключен к счетному входу счетчика, информационный выход которого i(i)l подключен к управляющему входу второоь го коммутатора и управляющему входу со первого коммутатора, информационный вход которого является информационным входом фильтра, второй вход . второго элемента ИЛИ подключен к четвертому выходу синхронизатора, пятый выход которого подключен к входу сброса счетчика и второму входу пятого элемента И, выход которого является информационным выходом фильтра.

| Левин Б.Р | |||

| Теоретические основы статистической радиотехники | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| радио, 1976 | |||

| Коча, Ланиэ | |||

| Аппаратурная реализация цифровых фильтров | |||

| - Зарубежная радиоэлектроника, 1979 | |||

Авторы

Даты

1985-07-30—Публикация

1984-02-06—Подача