Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов различного назначения для формирования вероятностных харак теристик случайных процессов, в час ности для определения центра массы плоских фигур.

Цель изобретения - увеличение быстродействия устройства

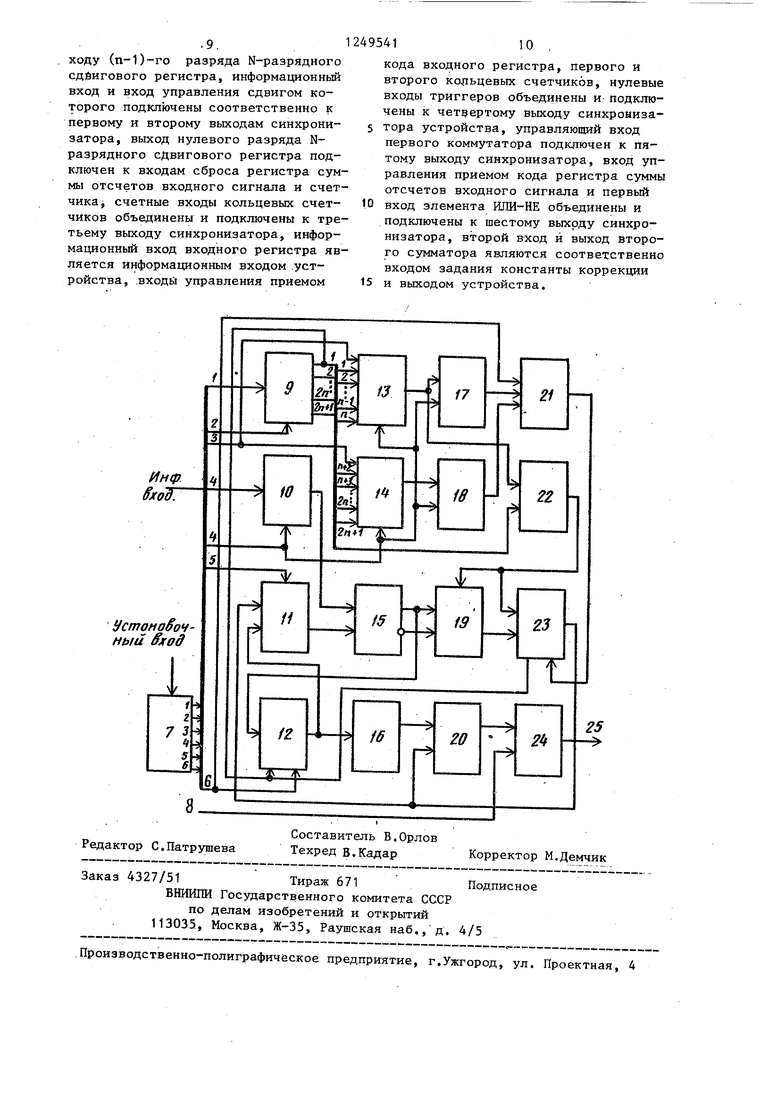

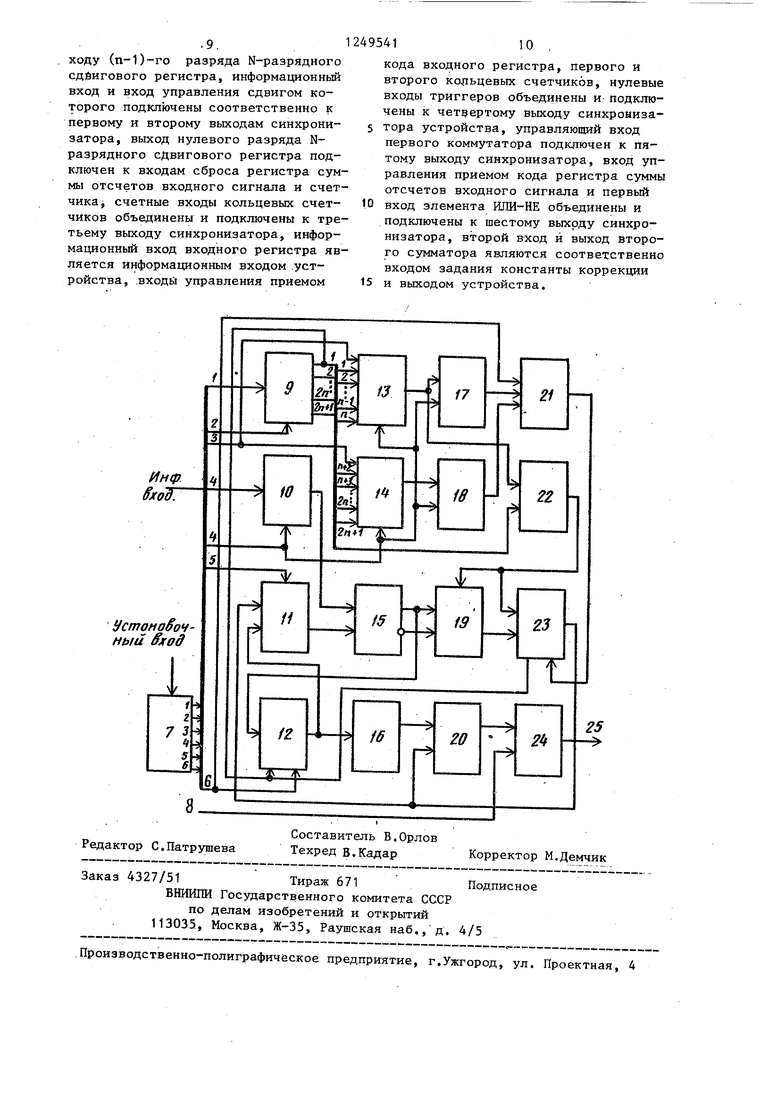

На чертеже представлена структурная схема устройства.

Устройство содержит установочный вход, информационный вход, причем работа устройства обеспечивается сигналами управления: установки 1, сдвигом .2, тактом 3, записью 4, суммированием 5, переписью 6, поступающими соответственно с одноименных выходов синхронизатора 7; вход 8 константы коррекции устройства, N-разрядный сдвиговый регистр 9, где N - число отсчетов входного сигнала (для определенности N полагается нечетным), входной регистр 10, первый коммутатор 11, регистр 12 суммы отсчетов входного сигнала, первый 13 и второй 14 кольцевые счетчики, первый сумматор 15, блок 16 памяти, первый 17 и второй 18 триггеры, второй коммутатор 19, блок 20 умножения, элемент ИЛИ-НЕ 21, элемент ИЛИ 22, счетчик 23, второй сумматор 24 и выход 2 устройства,

Сче гчики 13 и 14 выполняют роль элементов задержки по п+1 тактов

(п-0 I - 1 , через xj обозначается

целая часть действительного числа х) В соответствии с этим их разрядность составляет (п+1) бит. Вход j-ro разряда (J 0,1,,.,, п-1) кольцевого счетчика 13 подключен к выходу j-ro разряда сдвигового регистра 9, а вход (J + 1)-го разряда кольцевого счетчика 14 подключен к -выходу (n+j+1)-ro разряда сдвигового регистра 9. Выходы старшего разряда кольцевого счетчика 13 и младшего разряда кольцевого счетчика 14 подключены к единичным входам триггеров 1 и 18 соответственно, счетные вкоды счетчиков 13 и 14 объединены и подключены к выходу 3 синхронизатора Управляющие входы приема кода счетчиков 13 и 14, входного регистра 10, нулевые входы триггеров 17 и 18 объе

5 0 5 0 j

5

5

динены и подключены к выходу 4 синхронизатора 7 устройства.

Выход нулевого разряда регистра 9 подключен к входам сброса регистра 12 и счетчика 23, а выход (п-1)-го разряда подключен К второму входу элемента И 22, первый вход которого объединен с единичным входом триггера (7, а выход подключен к входу управления коммутатора 19 и счетному входу счетчика 23. Выходы триггеров 17 и 18 подключены соответственно к второму и третьему входам элемента ИЛИ-НЕ 21, выходом подключенного к управляющему входу приема кода счетчика 23.

Сумматор 15 осуществляет сложение двоичных чисел по модулю 2 , где

Ь log, (n(n-f1)()),

где bo - разрядность отсчетов вхбД™

ного сигнала, через Jx .обозначается наименьшее целое чис- ло, не меньшее х. В соответствии с этим коммутаторы 11 и 19 содержат по Ьд- двухканальных мультиплексоров, а разрядность регистров 10 и 12 и счетчика 23 составляет Ь бит..

Управляющий блок коммутатора 11 подключен к выходу 5 синхронизатора, первый информационный вход коммутатора 11 объединен с вторым входом блока 20 умножения и подключен к выходу счетчика 23. Второй информационный вход коммутатора 11 объединен с входом блока 16 памяти и подключен к .выходу регистра 12, вход управления приемом кода которого объединен с первым входом элемента ИЛИ-НЕ 21 и Iподключен к выходу 6 синхронизатора, выход коммутатора 11 подключен к второму входу сумматора 15, первым входом подключенного -к выходу входного регистра 10. Первый информационный вход коммутатора 19 объединен с информационным входом регистра 12 и подключен к прямому выходу сумматора 15. Второй информационный вход подключен к инверсному выходу сумматора 15, а выход - к информационному входу счетчика 23.

Блок 16 памяти обладает емкостью 2 слов разрядностью b () бит. В память по адресу Be 1,2,...,

-1 записывается константа

г 1 q(B) S-2.. , (,)

3

где b log, N()/, S - це- ЛЫЙ положительный масштаб, разрядность которого составляет bj бит, через х обозначается ближайшее к X целое число, т.е.

1

х, если - х, если х + -4:

Блок 20 умножения служит для полутя произведенр на -2V1, -2 + 2,..., 2 - 1J представленных в дополнительном коде. Первый вход блока 20 подключен к выходу блока 16 памяти, а выход групт пы разрядов, начиная с (Ь. -1)-го по ( 2)-ый соединен с первым входом второго сумматора 24, реализующего операцию сложения по модулю 2 где

Ь ,/(n+1)()/.

Второй вход второго сумматора 24 подключен к входу 8 константы коррекции, а выход является выходом 25 устройства.

Функция предлагаемого устройства для определения центра массы плоской фигуры заключается в вычислении величины

1 X

f S(2)

тМ

где S - положительный целый масштаб, х - i-ый отсчет входного сигнала ,1,...,bo-l.

Добавляя и вычитая в правой части (2) величину (n+1)S, характеристику jy можно представить в виде

f - + (n+1.)-S,

(3)

А -Ж::(п-1+1)х,+ (4)

л/ В z: -х ..

i:

(5)

Согласно модифицированной.лемме Евклида из теоремы делимости можно записать:

S + Q(B)-B, (6)

1249541

- |где (S 2 1 - абсолютно наименьший вычет, сравнимый с величиной по модулю В, Q(B) - величина, определяемая соотношением (1). Подставляя (6) в (3), находим:

p- 5ji i- -f.,

-, .

Q

Так как |AU , а

42

, то первое слагаеьюе в последнем

соотношении не превосходит 1/2. Пре- 15 небрегая им получаем следующее рассчитанное соотношение для искомой характеристики:

20

f-f + (. (7)

Устройство работает следующим образом.

Обработка отсчетов отдельной реализации случайного процесса, несущего информацию о наблюдаемом объекте, производится в два этапа. Первый этап занимает N циклов, i-ьш из которых соответствует отсчету х-(,2,...,N): при этом на каждом цикле в течение п+1 тактов выполняются однотипные действия.

Перед первым циклом в сдвиговый регистр 9 через установочный выход 1 синхронизатора записывается код еди- 5 ницы, содержимое нулевого разряда регистра 9 ( о 1) подается на входы сброса регистра 12 и счетчика 23, вследствие чего они обнуляются. На первом такте первого цикла по сигна- 0 лу Гг 1, поступающему с выхода 4 синхронизатора, во входной регистр 10 через информационный вход устройства принимается отсчет х, содержимые п младших и п старших разрядов регист- 5 ра 9 передаются соответственно в кольцевые счетчики 13 и 14, а триггеры 17 и 18 обнуляются. Затем на первый и второй информационные входы коммута- тора 11 подаются соответственно со держимые счетчика 23 и регистра 12 (в текущий момент нулевые), а на вход управления выхода 5 синхронизатора подается сигнал Г, 1, благодаря чему на выходе коммутатора 11

появляется содержимое регистра 12, которое поступает на второй вход сумматора 15. На первый его вход с выхода регистра 10 подается отсчет

X . в результате сумматор 15 получит- величину .О, которая с первого прямого выхода сумматора 15 поступа-. ет на первый информационный вход коммутатора 19 и записывается в регистр 12 по сигналу Гу 1, подаваемому на его управляющий вход выхода 6 синхронизатора. Обратный код величины х + 1 с второго (инверсного) выхода сумматора 15 поступает на второй информационный вход коммутатора 19, на вход управления которого подается сигнал

12495416

сумматора 15 через первый информационный вход коммутатора t1 поступит содержимое счетчика 23, т.е. величина (j-1)x . Складывая содержимое X, входного регистра 10 и число (j-1)x , сумматор 15 получит величи- которая через первый инфорну jx,

мационньй вход коммутатора 19 передается в счетчик 23. На вход уп1.0 равления коммутатором 19 и управляющий вход приема кода счетчика 23 в рассматриваемом такте соответственно поступают сигналы: Г 0, Т 1. Таким образом, по окончании

Г, Й„,,,

(8)

вырабатываемый элементом И 22 по входным величинам 6 и 6,. , поступающим соответственно с выходов п-го разряда кольцевого счетчика 13 и (n-l)-ro разряда сдвиЕового регистра 9. На данном такте Tj О, поэтому На выходе коммутатора 19 появляется величина, поданная на его информационный вход. Сформированный на выходе коммутатора 19 код поступает на информационный вход счетчика 23j однако в него записан не будет, так как на управляющий вход приема кода счетчика 23 с выхода злемента ИЛИ- НЕ 21 подается сигнал

Fg Г Vr -Vr

(9)

принимающий нулевое значение, в силу того, что на первый вход злемента, ВДИ-НЕ 21 с шестого выхода синхронизатора подан сигнал Г. 1. .(г и г - содержимое триггеров 17 и 18 соответственно) .

В конце каждого, такта по сигналу, подаваемому с выхода 3 синхронизатора на счетные входы кольцевых счетчиков 13 и 14, их содержимые сдвигаются соответственно на 1.бит влево и 1 бит вправо. Выдвинутые значения 6 и 6 старшего и младшего разрядов кольцевых счетчиков 13 и 14 поступают соответственно на единичные входы триггеров 17 и 18.

На последующих п тактах цикла работы устройства описанные действия повторяются за исключением того, что на выходы 4, 5 и 6 синхронизатора единичные сигналы не подаются (т.е. Г - r.j Г4 - 0), Согласно изложенному в ходе (j+1)-ro такта первого цикла (J 1,2,...,п) на второй вход

сумматора 15 через первый информационный вход коммутатора t1 поступит содержимое счетчика 23, т.е. величина (j-1)x . Складывая содержимое X, входного регистра 10 и число (j-1)x , сумматор 15 получит величи- которая через первый инфор

ну jx,

мационньй вход коммутатора 19 передается в счетчик 23. На вход управления коммутатором 19 и управляющий вход приема кода счетчика 23 в рассматриваемом такте соответственно поступают сигналы: Г 0, 1. Таким образом, по окончании

первого тдикла в регистре 12 сформируется код числа х, а в счетчике 23 - код числа пх,.

В конце каждого цикла по сигналу Г 1, подаваемому с выхода 2 синхронизатора, содержимое сдвигового регистра 9 сдвигается на 1 бит влево, и затем начинается очередной цикл, в течение которого выполняются описанные действия устройства.

На первом такте г-го цикла (i - 2,3,...п) сумматор 15 получает сумму первых i отсчетов входного сиг

налд.:;

гистр такта

EJX,, и она записывается в ре

12, а по окончании (n-i+2)-ro

i-ro цикла в счетчике 23 будет получена взвешенная сумма i отсчетов сигнала: 23()х„, На первом

такте i-ro цикла (i 1,2,...,п) в кольцевом сч-етчике 13 единица будет записана в (i-1)-oM разряде. Поэтому по истечении (n-i+2) также единица с выхода старшего разряда кольцевого счетчика 13 поступит на единичный вход триггера 17, вследствие чего на . всех последующих тактах цикла выходной сигнал Г элемента.ИЛИ-НЕ 21 принимает нулевое значение (9). Это приводит к блокировке записи информа- I.Jiии в счетчик 23, т.е. указанные такты i-ro цикла являются холостыми.

Во втором такте п-го цикла на первый и второй вход элемента и 22 поступают единичные сигналы ( 1), благодаря чему на управляющий вход коммутатора 19 и счетный вход счетчика 23 будет подан сигнал Fj 1 (8). В результате в счетчик 23 через второй информационный вход коммутатора 19 поступит обратный код вели0.

чины - 22 (n-i4-1)x J, формируемой в

данНбм такте на инверсном выходе

7

сумматора 15. После добавления ецы в счетчик 23 сформируется допнительный код первого слагаемого отношения (4). По окончании N-ro цикла работы устройства в регист будет получена величина В (5), а счетчике 23 - дополнительный код личины А (4), при этом в ходе п следних циклов необходимая послевательность сигналов управления писью информации в счетчик 23 выбатывается при помощи кольцевого счетчика 14 и триггера 18.

После вычисления величины А и В предлагаемым устройством может быть начата обработка отсчетов новой реализации исследуемого процесса. Одновременно с этим устройством реализуется второй этап процедуры формирования характеристики Jo (7) для текущей реализации процесса, С этой целью величина В с выхода регистра 1 подается на адресный вход блока 16 памяти, откуда по адресу В считыва- ется двоичньй код константы Q(B) (1 который с выхода блока 16 поступает на первый вход блока 20 умножения, а на второй его вход с выхода счетчика 23 подается дополнительный код числа А. Блок 20 умножения находит произведение A Q(B) и его старшая

A:Q(S)

часть (целая часть дроби

Л,-1

)

поступает на первый вход сумматора 24.35 памяти и подключен к выходу регистра

на второй вход 8 которого подается константа (п+1) S. Складывая входные величины сумматор 24 определяет искомую характеристику (7). Код величины f снимается с выхода 25 устрой- ства и на этом процесс обработки.текущей реализации исходного процесса заканчивается.

Предлагаемое устройство определяет

взвешенную сумму отсчетов, входного сигнала и осуществляет ее нормировку на сумму отсчетов, при этом обеспечивается возможность совмещения в6 времени обработки смежных реализаций исследуемого случайного процесса.

Формула изобрет-ен ия

Устройство для определения центра массы плоской фигуры, содержащее входной регистр, первый кольцевой

,8

и12

to

20

2 25 ,

счетчик, первый сумматор, первым входом подключенный к выходу входного регистра, первый триггер и элемент И, первый вход которого объединен с единичным входом первого триггера и подключен к выходу старшего разряда первого кольцевого счетчика, отличающееся тем, что, с целью увеличения быстродействия в него введены синхронизатор, N-pas- рядный сдвиговый регистр (N - число отсчетов входного сигнала), первый и второй коммутаторы, регистр суммы отсчетов входного сигнала, второй 5i кольцевой счетчик, блок памяти, второй триггер, блок умножения, элемент ИЛИ-НЕ, счетчик и второй сумма- тор, при этом входы п младших разря- дов первого кольцевого счетчика (п - целая часть величины N/2) подключены к выходам одноименных разрядов N- разрядного сдвигового регистра, входы п старших разрядов второго кольцевого счетчика подключены соответственно к .выходам п старших разрядов сдвигового регистра, а выход младшего разряда второго кольцевого счетчика подключен к единичному.входу второго триггера, первый информационный вход первого коммутатора объединен с вторым входом блока умножения и подключен к выходу счетчика, второй информационный вход первого коммутатора объединен с входом блока

30

5

0

5

суммы отсчетов входного сигнала, а выход соединен с вторым входом первого сумматора, первый информационный вход второго коммутатора объединен с входом регистра суммы отсчетов входного сигнала и подключен к прямому выходу первого сумматора, второй информационный вход второго коммутатора подключен к инверсному выходу первого сумматора, а выход - и информационному входу счетчика,счетный вход которого объединен с управляющим входом второго коммутатора и подключен к выходу элемента И, первый вход блока умножения подключен к выходу блока памяти, а выход - к первому входу второго сумматора, выходы первого и второго триггеров подключены соответственно к второму и тр етьему входам элемента ИЛИ-НЕ, выход которого подключен к входу управления приемом кода счетчика, вто- |рой вход элемента И подключен к выд

ходу (n-l)-ro разряда N-разрядного сдйигового регистра, информационный вход и вход управления сдвигом которого подключены соответственно к первому и второму выходам синхронизатора, выход нулевого разряда N- разрядного сдвигового регистра подключен к входам сброса регистра суммы отсчетов входного сигнала и счетчика, счетные входы кольцевых счетчиков объединены и подключены к третьему выходу синхронизатора, инфор- мационньй вход входного регистра является информационным входом .устройства, .входи управления приемом

Составитель В.Орлов Редактор С.Патрушева Техред В.Кадар Корректор М.Демчик

Заказ 4327/51Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

.Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

9541

10 ,

кода входного регистра, первого и второго кольцевых счетчиков, нулевые входы триггеров объединены и подключены к четвертому выходу синхрониза- 5 тора устройства, управляющий вход первого коммутатора подключен к пятому выходу синхронизатора, вход управления приемом кода регистра суммы отсчетов входного сигнала и первый 0 вход элемента ИЛИ-НЕ объединены и подключены к шестому выходу синхронизатора, второй вход и выход второго сумматора являются соответственно входом задания константы коррекции 15 и выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Цифровой фильтр | 1985 |

|

SU1244786A1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Цифровой фильтр | 1985 |

|

SU1297213A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство для вычисления преобразования Фурье-Галуа и свертки | 1985 |

|

SU1295415A1 |

| Устройство для ортогонального преобразования цифровых сигналов по уолшу-адамару | 1984 |

|

SU1234847A1 |

| Устройство для определения амплитудно-частотных характеристик объектов | 1989 |

|

SU1689876A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Коррелометр | 1981 |

|

SU1057954A1 |

Устройство относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов, определяют вэв е-е шенную сумму отсчетов входного сигнала и осуществляет ее нормировку на сумму отсчетов. Цель изобретения - увеличение быстродействия. Устройство содержит кольцевые счетчики, регистры, элементы логики, блок памяти, коммутаторы. 1 ил. а с 4 QD СЛ

| Устройство для определения площадей выбросов | 1979 |

|

SU877559A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения пло-щАдЕй ВыбРОСОВ | 1979 |

|

SU830401A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-07—Публикация

1985-02-11—Подача