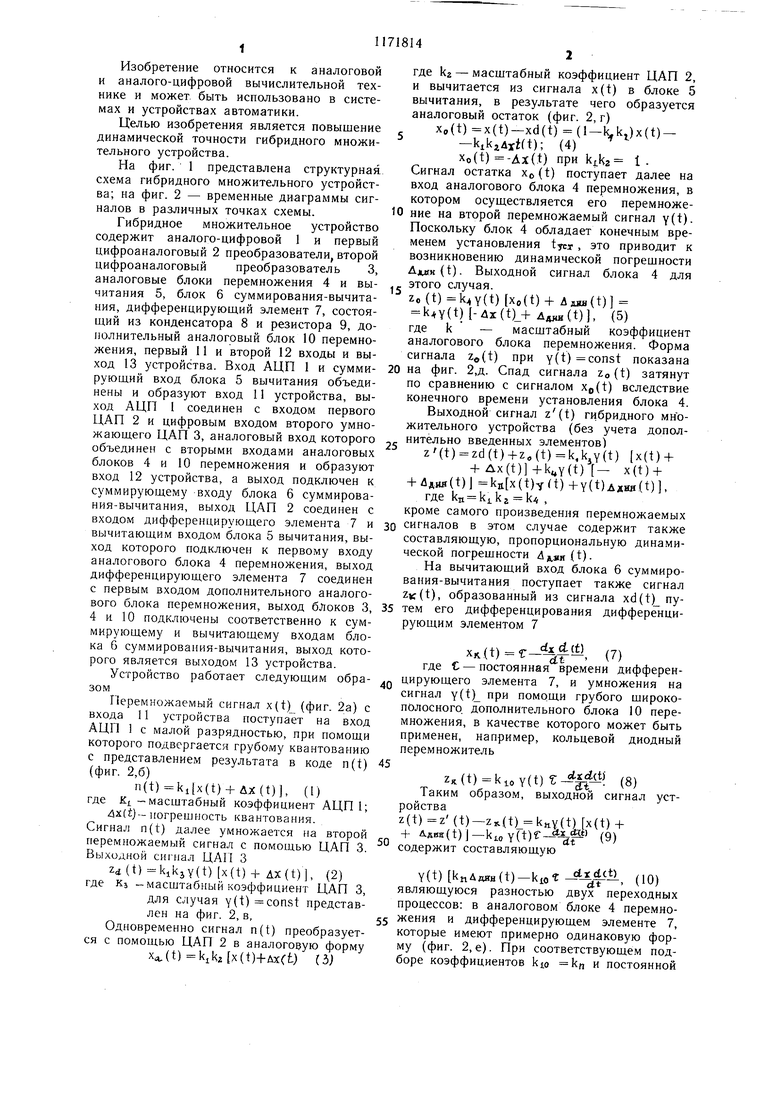

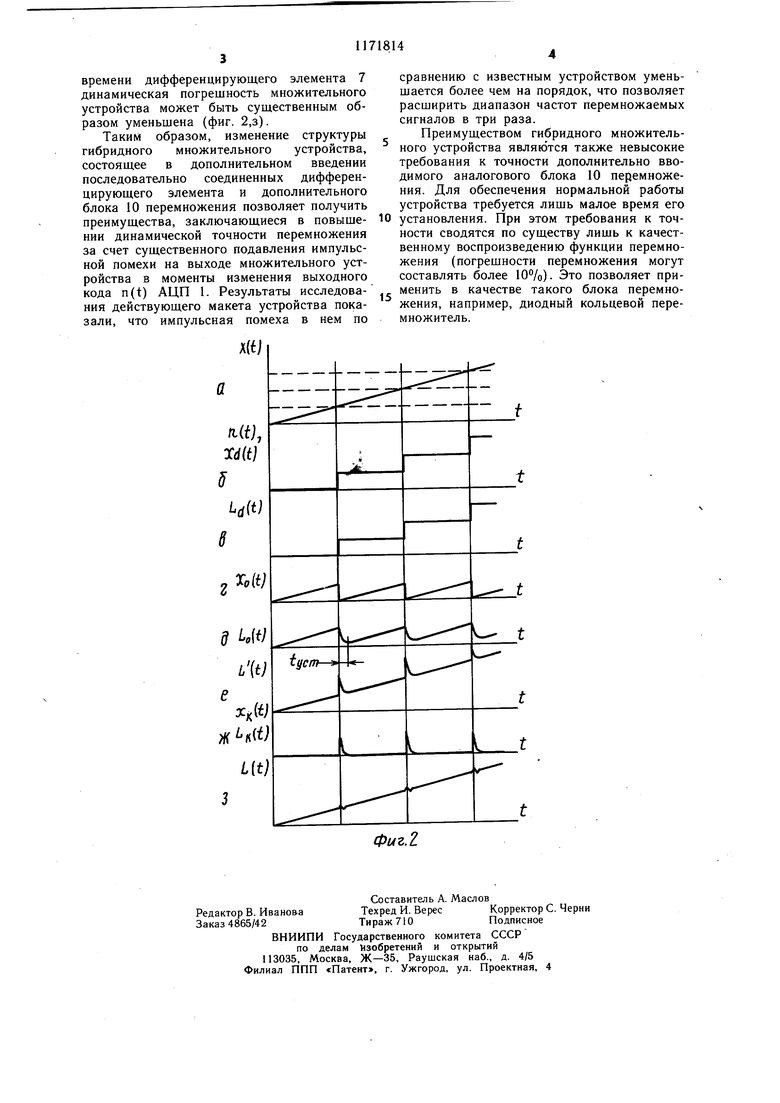

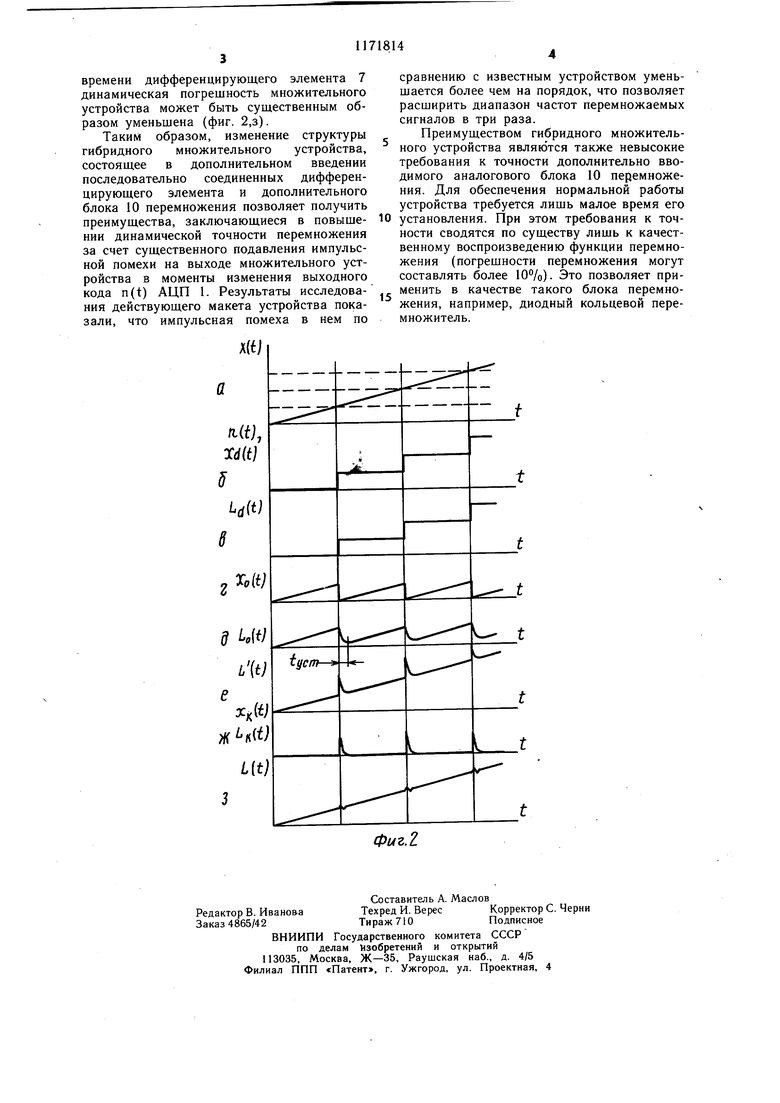

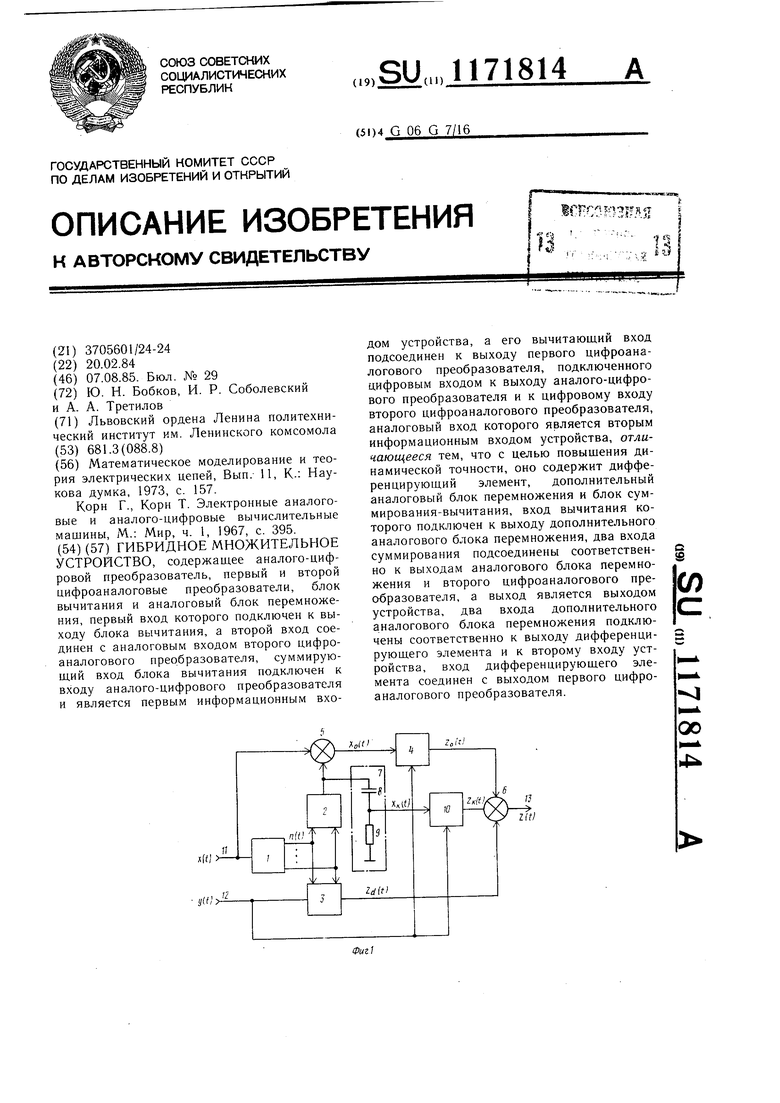

Изобретение относится к аналоговой и аналого-цифровой вычислительной технике и может быть использовано в системах и устройствах автоматики. Целью изобретения является повышение динамической точности гибридного множительного устройства. На фиг. 1 представлена структурная, схема гибридного множительного устройства; на фиг. 2 - временные диаграммы сигналов в различных точках схемы. Гибридное множительное устройство содержит аналого-цифровой 1 и первый цифроаналоговый 2 преобразователи, второй цифроаналоговый преобразователь 3, аналоговые блоки перемножения 4 и читания 5, блок 6 суммирования-вычитания, дифференцирующий элемент 7, состоящий из конденсатора 8 и резистора 9, дополнительный аналоговый блок 10 перемножения, первый 11 и второй 12 входы и выход 13 устройства. Вход АЦП 1 и суммирующий вход блока 5 вычитания объединены и образуют вход 11 устройства, выход АЦП 1 соединен с входом первого ЦАП 2 и цифровым входом второго умножающего ЦАП 3, аналоговый вход которого объединен с вторыми входами аналоговых блоков 4 и 10 перемножения и образуют вход 12 устройства, а выход подключен к суммирующему входу блока 6 суммирования-вычитания, выход ЦАП 2 соединен с входом дифференцирующего элемента 7 и вычитающим входом блока 5 вычитания, выход которого подключен к первому входу аналогового блока 4 перемножения, выход дифференцирующего элемента 7 соединен с первым входом дополнительного аналогового блока перемножения, выход блоков 3, 4 н 10 подключены соответственно к суммирующему и вычитающему входам блока б суммирования-вычитания, выход которого является выходом 13 устройства. Устройство работает следующим образомПеремножаемый сигнал x(t) (фиг. 2а) с входа I1 устройства поступает на вход АЦП 1 с малой разрядностью, при помощи которого подвергается грубому квантованию с представлением результата в коде n(t) (фиг. 2,6) n(t)(t) +u.x(t), (1) где Ki-масштабный коэффициент АЦП1; 4x(i) погрешность квантования. Сигнал n(t) далее умножается на второй перемножаемый сигнал с помощью ЦАП 3. Выходной сигнал ЦАП 3 Zd(t)kikjY(t) x(t)+ ДХ(1), (2) где Кз -масштабный коэффициент ЦАП 3, для случая Y(t)const представлен на фиг. 2, в. Одновременно сигнал n(t) преобразуется с помощью ЦАП 2 в аналоговую форму x(t)k,(t)-f-AxCt) (3j выгде kz - масштабный коэффициент ЦАП 2, и вычитается из сигнала x(t) в блоке 5 вычитания, в результате чего образуется аналоговый остаток (фиг. 2, г) x,(t)x(t)-xd(t) (l-k,k)x(t)-k.kjAjift); (4) Xo(t) -Ax(.t) при kj.k2 1Сигнал остатка Xc(t) поступает далее на вход аналогового блока 4 перемножения, в котором осуществляется его перемножение на второй перемножаемый сигнал y(i). Поскольку блок 4 обладает конечным временем установления tyci , это приводит к возникновению динамической погрешности Aju(K(t). Выходной сигнал блока 4 для этого случая. z«(t)k4Y(t)Xo(t)+ Адш,(1) k,y(t)-4x(t)+A«w.(t), (5) где k - масштабный коэффициент аналогового блока перемножения. Форма сигнала z(i) при Y(t) const показана на фиг. 2,д. Спад сигнала Zo (t) затянут по сравнению с сигналом Хд{1) вследствие конечного времени установления блока 4. Выходной сигнал z(t) гибридного множительного устройства (без учета дополнительно введенных элементов) z(t)zd(t)+z,(t)k,k,Y(t) x(t) + -f Ax(t)(t) - x(t) + + AMH(t)(t)Ya)+Y(t)A«iffl(t), где ka kj.kj k4 , кроме самого произведения перемножаемых сигналов в этом случае содержит также составляющую, пропорциональную динамической погрешности ). На вычитающий вход блока 6 суммирования-вычитания поступает также сигнал ZK(t), образованный из сигнала xd(t) путем его дифференцирования дифференцирующим элементом 7 XK(t) -z:-%-f, (7) где С - постоянная времени дифференцирующего элемента 7, и умножения на сигнал Y(t) помощи грубого широкополосного дополнительного блока 10 перемножения, в качестве которого может быть применен, например, кольцевой диодный перемножитель ZK(t)kioY(t)- |- Таким образом, выходной сигнал устройстваz(t) z (t)-z(t)kHY(t)x(t) + + As«(t)j-k,,Y(t) (9) содержит составляющую Y(t)knAAHH(t)-kioT- -i4-, (10) являющуюся разностью двух переходных процессов: в аналоговом блоке 4 перемножения и дифференцирующем элементе 7, которые имеют примерно одинаковую форму (фиг. 2, е). При соответствующем подборе коэффициентов kio kn и постоянной

времени дифференцирующего элемента 7 динамическая погрешность множительного устройства может быть существенным образом уменьщена (фиг. 2,з).

Таким образом, изменение структуры гибридного множительного устройства, состоящее в дополнительном введении последовательно соединенных дифференцирующего элемента и дополнительного блока 10 перемножения позволяет получить преимущества, заключающиеся в повыщении динамической точности перемножения за счет существенного подавления импульсной помехи на выходе множительного устройства в моменты изменения выходного кода n(t) АЦП 1. Результаты исследования действующего макета устройства показали, что импульсная помеха в нем по

сравнению с известным устройством уменьщается более чем на порядок, что позволяет расширить диапазон частот перемножаемых сигналов в три раза.

Преимуществом гибридного множительного устройства являются также невысокие требования к точности дополнительно вводимого аналогового блока 10 перемножения. Для обеспечения нормальной работы устройства требуется лишь малое время его установления. При этом требования к точности сводятся по существу лишь к качественному воспроизведению функции перемножения (погрешности перемножения могут составлять более 10%). Это позволяет применить в качестве такого блока перемножения, например, диодный кольцевой перемножитель.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое множительное устройство | 1983 |

|

SU1163335A1 |

| Множительное устройство | 1984 |

|

SU1160442A1 |

| Аналого-цифровое множительное устройство | 1984 |

|

SU1215122A1 |

| Аналого-цифровое множительное устройство | 1984 |

|

SU1280400A1 |

| Гибридное множительное устройство | 1985 |

|

SU1325521A1 |

| Амплитудно-фазовый анализатор гармоник периодических сигналов | 1986 |

|

SU1386937A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1562972A1 |

| Аналого-цифровое множительное устройство | 1980 |

|

SU883930A1 |

| Устройство для преобразования нечетких множеств | 1989 |

|

SU1695333A2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАКОПЛЕНИЯ ЭНЕРГИИ В МАТЕРИАЛЕ ПРИ ЦИКЛИЧЕСКОМ НАГРУЖЕНИИ | 1994 |

|

RU2087895C1 |

а

fid), :cd(t

S Wf

2 Ui) д ioW

L{t}

e x,(i)

(

Lit) 3

| Математическое моделирование и теория электрических цепей, Вып.- 11, К.: Наукова думка, 1973, с | |||

| Соломорезка | 1918 |

|

SU157A1 |

| Корн Г., Корн Т | |||

| Электронные аналоговые и аналого-цифровые вычислительные машины, М.: Мир, ч | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 395. | |||

Авторы

Даты

1985-08-07—Публикация

1984-02-20—Подача