ла выполняемых операций и упрощения -управляемого арифметического модули, первый вход седьмого элемента И соединен с выходом десятого элемента И, вторые входы восьмого и одиннадцатого элементов И соединены соответственно с девятым и восьмым управляющими входами управляемого арифметического модуля, пятый и шестой выходы которого соединены соответственно с выходами седьмого и второго элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный регистр сдвига | 1983 |

|

SU1176385A1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Управляемый логический модуль | 1980 |

|

SU962923A1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

| Универсальный вычислительный автомат | 1983 |

|

SU1196844A1 |

| Процессор | 1981 |

|

SU962964A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Конвейерное устройство для выполне-Ния АРифМЕТичЕСКиХ ОпЕРАций НАдМНОжЕСТВОМ чиСЕл | 1979 |

|

SU849205A1 |

| Арифметическое устройство | 1981 |

|

SU1012240A1 |

Изобретение относится к вычислительной технике и предназначено для реализации узлов и устройств цифровых вычислительных машин методами интегральной технологии со средним и большим уровнями интеграции.

Известен управляемый арифметический модуль, содержащий триггер,пер,вый управляемый логический блок, который содержит двенадцать элементов И, четыре элемента ИЛИ, четыре элемента НЕ, второй управляемый логический блок, который содержит четыре элемента И и один элемент, ИЛИ l ,.

Недостатком данного управляемого арифметического модуля являются ограниченные функциональные возможности, поэтому невозможно его использование для реализации нерегулярных устройств цифровой вычислительной машины. Кроме того, значительна сложность данного управляемого арифметического модуля. I . .

Наиболее близким техническим решением к изобретению является управляемый арифметический модуль, содержащий основной и дополнительный триггеры, тринадцать элементов И и семь элементов ИЛИ, причем выходы первого, второго, третьего и чегвертого элементов И соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с единичным входом основногЪ триггера, выходы пятого, шестого и седьмого элементов И соединены соответственно с первым, вторым и третьим входами второго элемента ИЛИ, выход которого подключен к нулевому входу основного триггера, прямой выход которого соединен с первым входом восьмого элемента И, выход которого соединен с первым входом третьех-О элемента .ИЛИ, второй вход которого подключен к выходу девято-гго элемента И, первые входы первого четвертого, третьего и десятого элементов И соединены соответственно с первым, вторым, третьим и чет вёртым управляющими входами управляемого арифметического модуля, вторые входы первого, третьего и четветого элементов И подключены соответственно к первому, второму и третье.му информационным входам управляемого арифметического модуля, первые /Ьходы пятого и шестого элементов, И соединены соответственно с вторым и третьим управляющими входами управляемого арифметического модуля, второй вход десятого элемента И соединен с первым информационным входом управляемого арифметического модуля, первые входы второго и седьмого элементов И подключены к выходу четвертого элемента ИЛИ, первый и второй входы которого подключены к выходам соотв етственно десятого и одиннадцатого элементов И, вторые входы второго и седьмого элементов И подключены соответственно к первому и второму выходам управляеMOfo арифметического модуля, а также соответственно к инверсному и прямому выходам дополнительного триггера, единичный вход которого . подключен к выходу третьего элемента ИЛИ, а нулевой вход подключен к выходу пятого элемента ИЛИ, пятый управляющий вход управляемого арифметического модуля соединен с первым входом пятого элемента ИЛИ., второй вход которого соединен с выходом двенадцатого элемента И, первый вход которого соединен с инверсным выходом основного триггера и третьим выходом управляемого арифметического модуля, второй вход двенадцатого элемента И соединен с выходом шестого элемента ИЛИ, первый вход которого соединен с шестым управляющим входом управляемого арифметического модуля и первым уходом седьмого элемента ИЛИ, седьмой и восьмой управляющие входы управляемого арифметического модуля подключены к вторым входам соответственно шестого и седьмого элементов ИЛИ,третьи входы которых соединены с выходом тринадцатого элемента И, первый вход которого соединен с девятым управляющим входом управляемого арифметического модуля и с первым входом одиннадцатого элемента И, второй вход которого соединен с вторым информационным входом управляемого арифметического модуля, четвертый информационный вход которого соединен с первым входом девятого элемен.та И, второй вход которого подключен к десятому управляющему входу управляемого арифметического модуля, пятый.и шестой информационные входы которого соединены с вторыми вхо:дами соответственно пятого и шестого элементов И, второй вход шестого элемента И соединен с вторым входом тринадцатого элемента И, одинннадцатый управляющий вход управляемого арифметического модуля соединен с четвертым входом второго элемента ИЛИ, четвертый выход управляемого арифметического модуля соединен с прямым выходом основного триггера 2

Недостатками известного управляемого арифметического модуля являются сложность и ограниченные функциональные возможности.

Целью изобретения является расширение функциональных возможностей за свет увеличения числа выполняемых операций и упрощение модуля.

Поставленная цель достигается тем, что управляемой арифметический модуль, содержащий основной и дополнительные триггеры, одиннадцать элементов И, четыре элемента ИЛИ, причем выходы первого, второго, третьего и четвертого элементов И соединены -с соответствующими входами первого элемента ИЛИ, выход которого соединен с единичным входом основного триггера, выход пятого, шестого и седьмого элементов И соединены соответственно с первым, вторым и третьим входами второго элемента ИЛИ, выход которого подключен к нулевому входу основного триггера, прямой выход которого соединен с первым входом восьмого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу девятого элемента И, первые входы- первого, четвертого, третьего и десятого элементов И соединены соответственно с первым, вторым, третьим и четвертым управляющими входами управляемого арифметического модуля, вторые входы первого, третьего и четвертого элементов И подключены соответственно к первому второму и третьему информационным входам управляемого арифметического модуля, первые входы пятого и шестого элементов И соединены соответственно с вторым и третьим управляющими входами управляемого арифметического модуля, второй вход десятого элемента И соединен с первым информационным входом управляе мого арифметического модуля, первый

вход второго, элемента И соединен с первым входом седьмого элемента И, вторые входы второго элемента И и седьмого элемента И подключзны соответственно к первому и второму вы5 ходам управляемого арифметического модуля, а также соответственно к инверсному и прямому выходам дополнительного триггера, единичный вход которого подключен к выходу третье0 го элемента ИЛИ, а нулевой вход подключен к выходу четвертого элемента ИЛИ, пятый управляющий вход управляемого арифметического модуля соединен с первым входом четвертого

5 элемента ИЛИ, второй которого соединен с выходом одиннадцатого элемента И, первый вход которого соединен с инверсным выходом основного триггера и третьим выходом упQ равляемого арифметического модуля, четвертый информационный вход которого соединен с первьлм входом девятого элемента И, второй вход котоР9ГО подключен к шестому управляюще5 му входу управляемого арифметического модуля, пятый и шестой информационные входы которого соединены с вторыми вxoдa ш соответственно пятого и шестого элементов И, седьмой управляющий вход управляемого ариф0метического модуля соединен с четвертым входом второго элемента ИЛИ, четвертый выход управляемого арифметического модуля соединен с пряглым выходом основного триггера, до5 полнительно первый вход седьмого элемента И соединен с выходом десятого элемента И, вторые входы восьмого и одиннадцатого элементов И соединены соответственно с девятым

0 и восьмым управляющими входами управляемого арифметического модуля, пятый и шестой выходы которого соединены соответственно с выходами седьмого и второго элементов И.

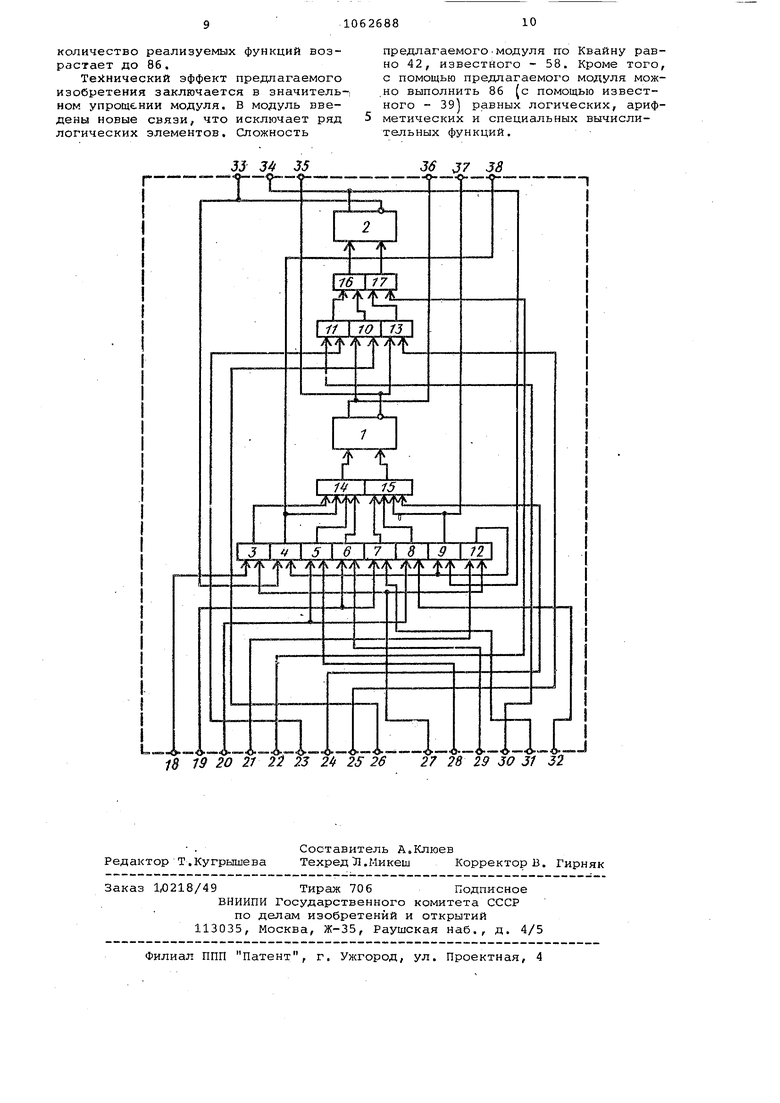

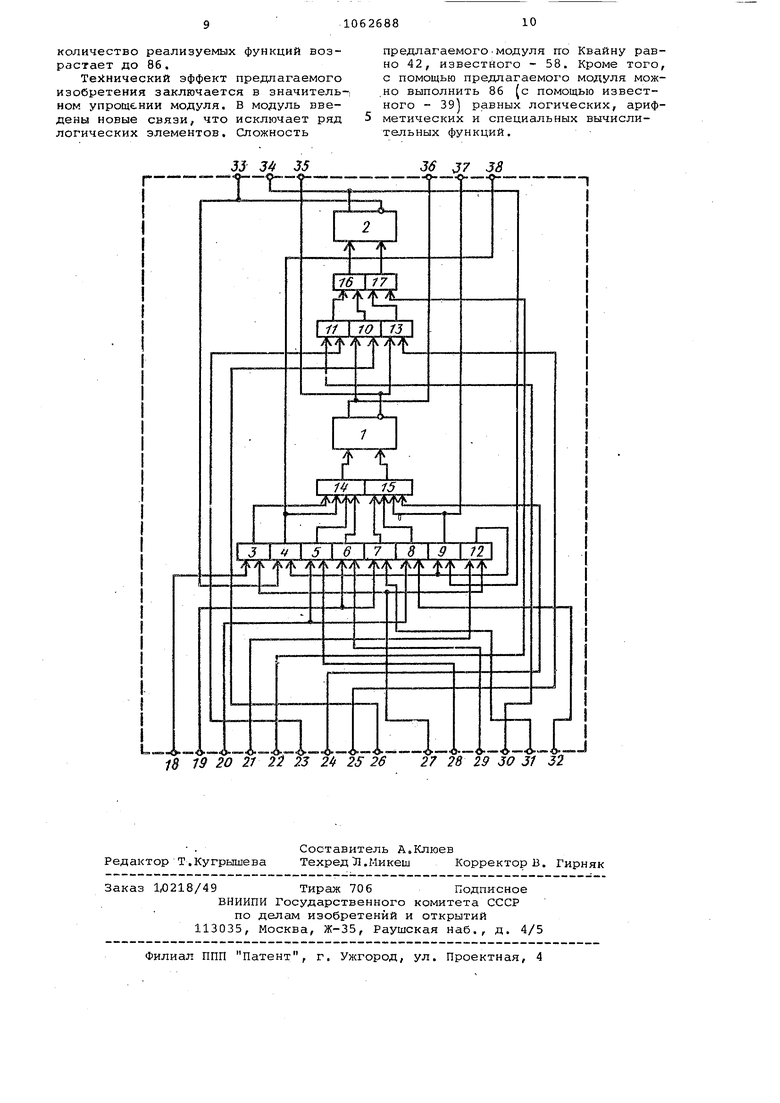

5 На чертеже представлена схема

предлагаемого управляемого арифметического модуля.

Управляемый арифметический модуль содержит основной 1 и дополнительQ ный 2 триггеры, одиннадцать элементов И 3 - 13, четыре элемента ИЛИ 14 - 17, управляющие входы 18 -26, информационные входы 27 - 32, выходы 33-38.. ,

5 На управляющие и информационные входы управляемого арифметического модуля подаются следующие сигналы: V, - Vq- управляющие сигналы (управляющие входы 18-26 0соответственно) ;

X -i-а - разряд кода X (первый информационный вход 27} ; Q + 1- содержимое соседнего

старшего разряда (второй . 5информационный вход Q 1- содержимое соседнего мла шего разряда (третий информационный вход 29) ; V, - разряд кода У- четвертый информационный вход ЗО) ; QJ-1 - содержимое соседнего младшего разряда (пятый информационный вход 31) Q;+l - содержимое соседнего ст шего разряда (шестой ин формационный вход 32) Сигнсшы УЧ-Vq обеспечивают выполнение следующих операций: V(вxoд 18) - прием операнда Xj основной триггер 1 и логическое сложе ние; V (вход 19) - сдвиг в сторону ст ших разрядов; 1(вход 20) - сдвиг в сторону мл ших разрядов; У(вход 21) - сложение nomocf2; V5{вxoд 22) - установка на нуль дополнительного тр гера 2; У(вход 23) - прием операнда дополнительный три гер 2; VJвxoд 24) - установка на нуль основного триггера Мп(вход 25) - коньюнкция содержи мых основного 1 и дополнительного 2 триггеров; Vft(вxoд 26) - дизъюнкция содержи мых основного 1 и дополнительного 2 триггеров. С помощью управляемого арифмети ческого модуля реализуются все 16 функций булевой алгебры двух переменных, некоторые функции трех и четырех переменных, функция двух самостоятельных регистров, функция двуступенчатого регистра, функция преобразования параллельного кода в последовательный и наоборот, фун ция реверсивного регистра сдвига числа, функция двоичного суммирунвд го или вычитающего счетчика, функция циклического, реверсивного реги ра сдвига, функция распространения единицы, нуля и др. Используя два и более управляемых арифметических модулей, можно реализовать и более сложные функци в частности, функции параллельного сумматора как с последовательным, так и со сквознымпереносом, функции схем контроля. Функции сравнения кодов, функции дешифратора, шиф ратора, коммутатора каналов, функции преобразования кода Грея в дво ичный и наоборот, и др. С помощью предлагаемого управля мого арифметического модуля реализуются как сингулярные булевые функции и функции двух переменньах, так и некоторые функции трех, четырех, и более.переменных. С целью иллюстрации реализации логических функций на управляемом арифметическом модуле приведено описание функционирования модуля при реализации отдельных функций. Функция поразрядной конъюнкции двух двоичных чисел выполняется следующим образом. Операнд У,- подается на Четвертый информационный вход 30, и сигналом Vu (вход 23) через девятый элемент И 11 и третий элемент ИЛИ 16 зано,сится в дополнительный триггер 2. Операнд X подается на первый информационный вход 27, и сигналом V (вход IB) через первый элемент И 3 и первый элемент ИЛИ 14 заносится в основной триггер 1. Предварительно основной 1 и дополнительный 2 триггеры соответственно сигналами VY (вход 24) и V5 (вход 22) устанавливаются в нулевое состояние. Для осуществления операции конъюнкции подается сигнал Vg (вход 25), и содержимое основного триггера 1 с инверсного выхода ч.ерез элементы И 13 и ИЛИ 17 переписывается в дополнительный триггер 2. В результате в дополнительном триггере 2 (выход 34) устанавливается логическое произведе§ ие. Последовательность выполнения функции поразрядной дизъюнкции аналогична предыдущему, но вместо сигнала Vg (вход 25) следует подать сигнал Vq (вход 26) , Функция поразрядной дизъюнкции реализуется также при подаче управляющих сигналов (вход 18) и V (вход 23) . Прямые коды Х и , подаются на первый 27 и четвертый 30 Информационные входы, и через элементы И 3, ИЛИ 14, И 11 и ИЛИ 16 подаются на прямые входы основного 1 и дополнительного 2 триггеров. В результате в основном триггере 1 получаем сумму X ; V , а в дополнительном триггере 2 -- У, , где у - содержимое основного 1 и дополнительного 2 триггеров, т.е. третий и четвертый переменные. Цалее можно получить (Х V x)v (у v У.) или(Х4 Y Х- )(R (у, V у;) и т.д. Функция сложения по mod 2 двух двоичных операндов Xj и У выполняете следующим образом. Сигналами V-j (вход 24) и (вход §2) основной 1 и дополнительный 2 триггеры устанавливаются в нулевое состояние. Сигналом Уц (вход 21) операнд х; от первого информационного входа 27 через десятый элемент И 12 подается на первые входы второго 4

и седьмого 9 элементов И, в результате чего в основном триггере 1 устанавливается сумма X, ® сложение пото(3 2). CигнaлoмVg вход 25) ( с) (вход 26) содержимое основного триггера 1 переписыкается в дополнительный триггер 2. Повторно подается сигнал N/4 (вход 21) , и второй операнд У , подаваемый с первого информационного входа .27, пройдя элементы И 12 и И 4 (или И 9) , в ;основном триггере 1 устанавливает сумму Х © У . Результат выдается на четвертом выходе 36 управляемого арифметического модуля.

Для реализации функций Пирса, Шеффера и эквивалентности производится дизъюнкция, конъюнкция и сложение по mod 2 соответственно, и результаты устанавливаются на инверсных выходах основного 1 (третий выходы модуля, выход 35) и дополнит;,ельного 2 (первый выход модуля, выход 33) триггеров.

Функция сдвига в сторону младших разрядов осуществляется за два полутакта. В первом полутакте сигналом УЗ (вход 20) парафазный код содержимого дополнительного триггера 2 (Q ;, ( { - 1} -го разряда через второй (вход 28) и шестой (вход 32) информационные входы и через третий 5 и шестой 8 элементы И переписывается в основной триггер 1 i-го разряда. Перепись из основного триггера 1 в дополнительный триггер 2 осуществляется сигналом Vg (вход 25) Mq (вход 26) .

Функция сдвига в сторону, старших разрядов осуществляется аналогично .предыдущему за два полутакта Сигналом М,2(вхоД 19) парафазный код содержимого дополнительного триггера 2 (i + l) -го разряда подается на третий (вход 29) и пятый (вход 31) информационные входы -го разряда. Открывается четвертый элемент И 6 или пятый элемент И 7 и возбуждается соответствующий вход основного триггера 1 -го разряда. Перепись в дополнительный триггер 2 осуществляется сигналом Уо(вход 25) SV,(вxoд 29) .

Счетчик работает, как обычный двухтактный суммирующий двоичный счетчик с последовательным переносо

Для создания структуры многоразрядного двоичного счетчика пятый выход 37 i -го управляемого арифметического модуля соединяется с первым информационным входом 27 (ч+ 1)-го управляемого арифметического модуля

Двоичный счет осуществляется после установки основного 1 и дополнительного 2 триггеров в нулевое состояние сигналами 24) и VjГвход 22). Импульсы счета поступают

на первый информационный вход 27 управляемого арифметического модуля первого разряда счетчика.

До начала счета на четвертые управляющие входы 21 .подается низкий

уровень синхроимпульса, а на восьмые 25 и девятые 26 управляющие входы - высокий уровень. При подаче первого импульса счета на первый информационный вход 27 младшего раз0 ряда счетчика одновременно на четвертые управляющие входы 21 поступает высокий уровень синхроимпульса, который через десятый 12 и второй 4 логические элементы И переводит ос5.НОВНОЙ триггер 1 первого-разряда счетчика из состояния О в состояние 1. За второй полупериод синхроимпульса, который подается на вось.мые 25 и девятые 26 управляющие вхоQ ды, допо1лнительный триггер 2 переходит.из состояния О в состояние 1. После подачи второго импульса счета и первого полупериода синхроимпульса основной триггер 1 первого

5 разряда счетчика переходит в состояние О. Одновременно с пятого выхода 37 управляемого арифметического модуля первого разряда счетчика высокий уровень сигнала подается на первый информационный вход 27

0 управляемого арифметического модуля . второго разряда счетчика и переводит основной триггер 1 второго разряда в состояние 1 и т.д.

Благодаря введенному в модуле шестому выходу 38, управляемый арифметический модуль работает в режиме двоичного вычитающего счетчика.

Каждый разряд двоичного h-разряд ного сумматора синтезируется на основе двух управляемых арифметических модулей М и М. Для этой цели требуется производить следующие соединения входов и выходов модулей: вто5 рой выход 34 -1-го ( 1,2,. .. ,И) управляемого арифметического модуля М соединяется с первым информационным входом 27 1 -го модуля Ы, пятый выход 37 j-го ii 1,2,. .., 1 - 1)

0 модуля М соединяется с первьом информационным входом 27 (j+. l) -го модуля М. Сумматор работает по тактам. Количество тактов зависит от количества разрядов сумматора и опреде5 ляется по формуле

Л; 3 (п + 1)

Используя один управляемый арифметический модуль в качестве разря0 да операционного устройства, возможно осуществить 76 различных арифметических и логических функций. При использовании в качестве разряда операционных устройств двух и более управляемых арифметических модулей

количество реализуемых функций возрастает до 86.

Тез1нический эффект предлагаемого изобретения заключается в значительном упрощении модуля. В модуль введены новые связи, что исключает ряд логических элементов. Сложность

JJ 34 J5

..

- о--о-- ю-™-OK™-о- О-о--о-

79 20 21 22 23 24 2S 26

/а

предлагаемогомодуля по Квайну равно 42, известного - 58. Кроме того, с помощью предлагаемого модуля можно выполнить 86 (с помощью известного - 39 равных логических, арифметических и специальных вычислительных функций.

36 J7 J8

-о--оо- О- О™ч --О-х

2 28 29 50 31 32

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 0 |

|

SU265565A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-23—Публикация

1982-10-29—Подача