1 .

Изобретение относится к радиотехнике и может найти применение в системах радиотелеграфной сйязи и пе- редачи данных.

Целью изобретения является повы шение помехоустойчивости при детектировании многочастотных сигналов.

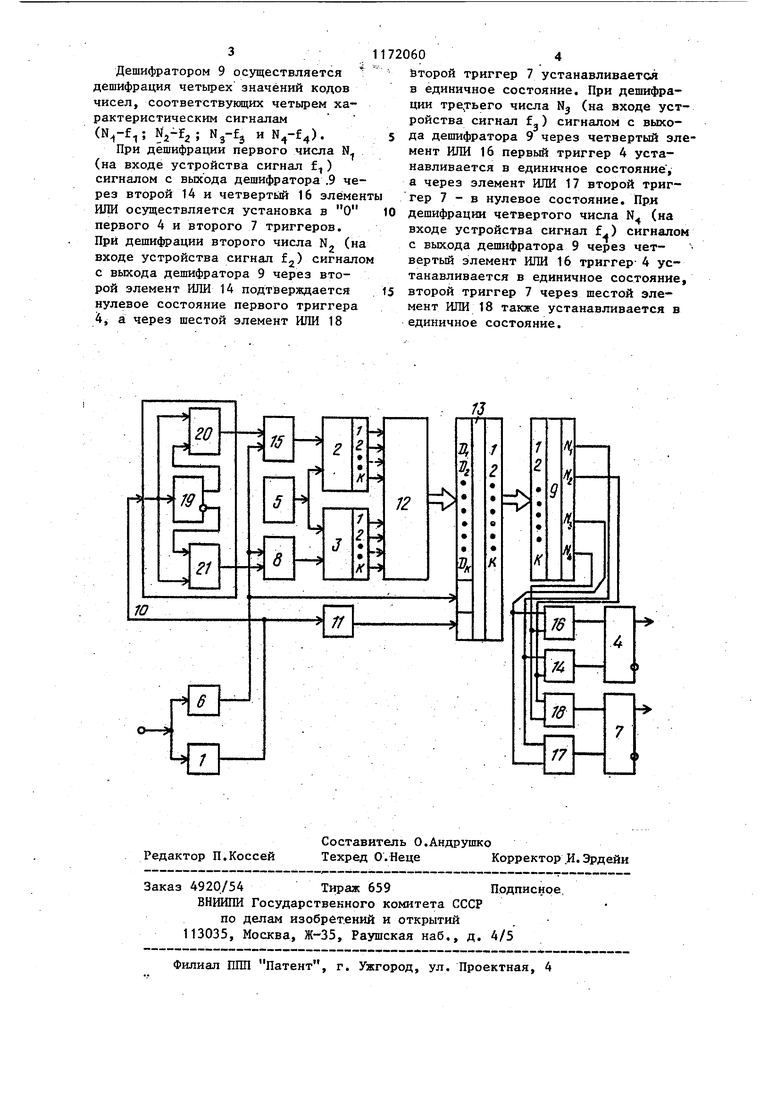

На чертеже изображена структурноэлектрическая схема устройства.

Устройство содержит формирователь 1 импульсов, первый счетчик 2, второй счетчик 3,.первый триггер 4, опорный генератор 5, пороговый блок 6, второй триггер 7, первый элемент ИЛИ 8, дешифратор 9, коммутатор 10, блок 11 задержки, блок 12 логическо го сложения, регистр 13, второй элемент ИЛИ 14, третий элемент ИЛИ 15, четвертьп1 элемент ИЛИ 16, пятый элемент ИЛИ 17 и шестой элемент ИЛИ 18, причем кoм Jyтaтop 10 выполнен в виде триггера 19 и двух элементов И 20 и 21.

Устройство работает следующим образом.

При отсутствии сигнала на входе устройства на выходе порогового блока 6 образуется сигнал единичного уровня который , устанавливает регистр 13 непосредственно, а первьш .2 и второй 3 счетчики через первый 8 и третий 15 элементы ИЛИ - в нулевое состояние. При поступлении на вход устройства сигнала, на выходе порогоззого блока 6 при наличии. сигнала на входе устройства устанавливается сигнал нулевого уровня. При этом разрешается работа первого 2 и второго 3 счетчиков, которые подсчитывают импульсы, поступающие на их так товые входы от опорного генератора 5. Из поступившего на вход устройства сигнала, представляющего собой последовательное чередование четырех характеристических сигналов, формирователем 1 импульсов вырабатывается последовательность коротких импульсов, причем каждый импульс этой последовательности соответствует точке перехода сигнала .через нуль.

Импульсы этой последовательности поступают .на вход коммутатора 10, в котором осуществляется переключение импульсов на выходы коммутатора, за счет переключения триггера 19 и соответствующего управления элементами И 20 и 21. По импульсам коммутатора 10 через первый 8 и третий 15.

720602

элементы ИЛИ осуществляется поочередная установка первого 2 и второго 3 счетчика в нулевое состояние. В результате в момент установки в 5 О первого счетчика 2, на Я-вькодах разрядов второго счетчика 3 устанавливается комбинация числа, соответствующая половине периода входного сигнала, и наоборот, при

установке в О второго счетчика

3 на 1 -выходах разрядов первого счетчика 2 будет комбинация числа, соответствующая половине периода входного сигнала. Таким образом,

осуществляется не11 рерывное преобразование половины периода входного сигнала в цифровую форму. Поскольку в Моменты установки в О первого 2 и второго 3 счетчиков

на выходах блока 12 логического сложения присутствует сигнал только с выходов одного из счетчиков 2 или 3 (один из них установлен в О), то и на шине параллельного

выхода блока 12 логического сложения формируются комбинации сигналов, являющиеся цифровым отображением половины периода присутствующего на входе устройства сигнала.

Блок 12 логического сложения состо. ит из элементов ИЛИ, подключенных входами к одноименным разрядам 1.разрядных первого 2 и второго 3 счетчиков, а выходами - к соответствующим по разряду соединительным линиям шины параллельного кода, которая представляет собой совокупHoctb соединительных линий, каждой из которых присвоен свой разряд

параллельного кода. Комбинация

двоичных сигналов в виде параллельного кода числа, отображающего длительнорть половины периода входного сигнала, записывается в регистр13

по сигналу выхода блока 11 задержки. За счет задержки записи исключаются искажения кода числа, которые могли иметь место из-за переходных процессов в блоке 12 логического сложения

и k-разрядном счетчике, устанавливаемом в нулевое состояние. После записи кода числа регистр 13 переходит в режим хранения .записанного числа, который длится половину периоцй входного сигнала. Код числа шиной параллельного кода передается из регистра 13 на входы дешифратора 9.

Дешифратором 9 осуществляется дешифрация четьфех значений кодов чисел, соответствующих четьфем характеристическим сигналам (,; и ).

При дешифрации первого числа N (на входе устройства сигнал f) сигналом с выхода дешифратора .9 через второй 14 и четвертой 16 элемен ИЛИ осуществляется установка в О первого 4 и второго 7 триггеров. При дешифрации второго числа N, (на входе устройства сигнал fj) сигнало с выхода дешифратора 9 через второй элемент ИЛИ 14 подтверждается нулевое состояние первого триггера 4 а через шестой элемент ИЛИ 18

йторой триггер 7 устанавливается в единичное состояние. При дешифрации тре -ьего числа N (на входе устройства сигнал fJ) сигналом с выхода дешифратора 9 через четвертый элемент ИЛИ 16 первый триггер 4 устанавливается в единичное состояние, а через элемент ИЛИ 17 второй триггер 7 - в нулевое состояние. При дешифрации четвертого числа N (на входе устройства сигнал f,) сигналом с выхода дешифратора 9 через четвертый элемент ШШ 16 триггер- 4 устанавливается в единичное состояние, второй триггер 7 через шестой элемент ИЛИ 18 также устанавливается в единичное состояние.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

| Устройство для программного управления | 1985 |

|

SU1267362A2 |

| Устройство для регистрации рабочих параметров транспортного средства | 1987 |

|

SU1481821A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для распределения заданий процессорам | 1989 |

|

SU1837287A1 |

1, УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ СИГНАЛОВ ДВОЙНОЙ ЧАСТОТНОЙ . ТЕЛЕГРАФИИ, содержащее коммутатор, . опорный генератор, первый счетчик, дешифратор, последовательно соединенные первый элемент ИЛИ и. второй счетчик, последовательно соединенные второй элемент ИЛИ и первый триггер, а также пороговый блок и формирователь импульсов, входы которых объединены, отличающееся тем, что, с целью повышения помехоустойчивости при детектировании многочастотных сигналов, в него введены третий, четвертый, пятьй и шестой элементы ИЛИ,блок г логического сложения, регистр, второй триггер, и блок задержки, вход которого соединен с входом коммутатора и с выходом формирователя импульсов, выходы коммутатора подключены к первым входам первого и третьего элементов ИЛИ, вторые входы которых, а также установочный вход регистра подключен к выходу порогового блока, выход третьего элемента ИЛИ подключен к установочному входу первого счетчика, выход опорного генератора подключен к тактовым входам первого и второго счетчиков, выходы которых подключены к входам блока логического сложения, выходы которого подключены к информационным входам регистра, тактовый вход которого соединен с выхо§ дом блока задержки, а выходы подключены к входам дешифратора, соответ(Л ствующие выходы которого через четвертый элемент ИЛИ подключены к втос рому входу первого триггера, а через пятьЕй и шестой элементы ИЛИ - к перс: вому и второму входам второго триггера. 2. Устройство ПОП.1, отли ч.ающееся. тем, что коммутатор N9 выполнен в виде триггера, выходы коОторого подключены к первым входам двух элементов И, вькоды которых ява ляются выходами коммутатора, входом которого является объединенные вход триггера и вторые входы элементов И,

| Детектор сигнала двоичного частного телеграфирования | 1977 |

|

SU617860A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для демодуляции фазоманипулированного сигнала | 1981 |

|

SU1054923A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-08-07—Публикация

1983-04-12—Подача