Изобретение относится к вычисли- . тельной технике и может найти применение в арифметических устройствах.

Целью изобретения является сокращение аппаратурных затрат, т.е упрощение устройства,

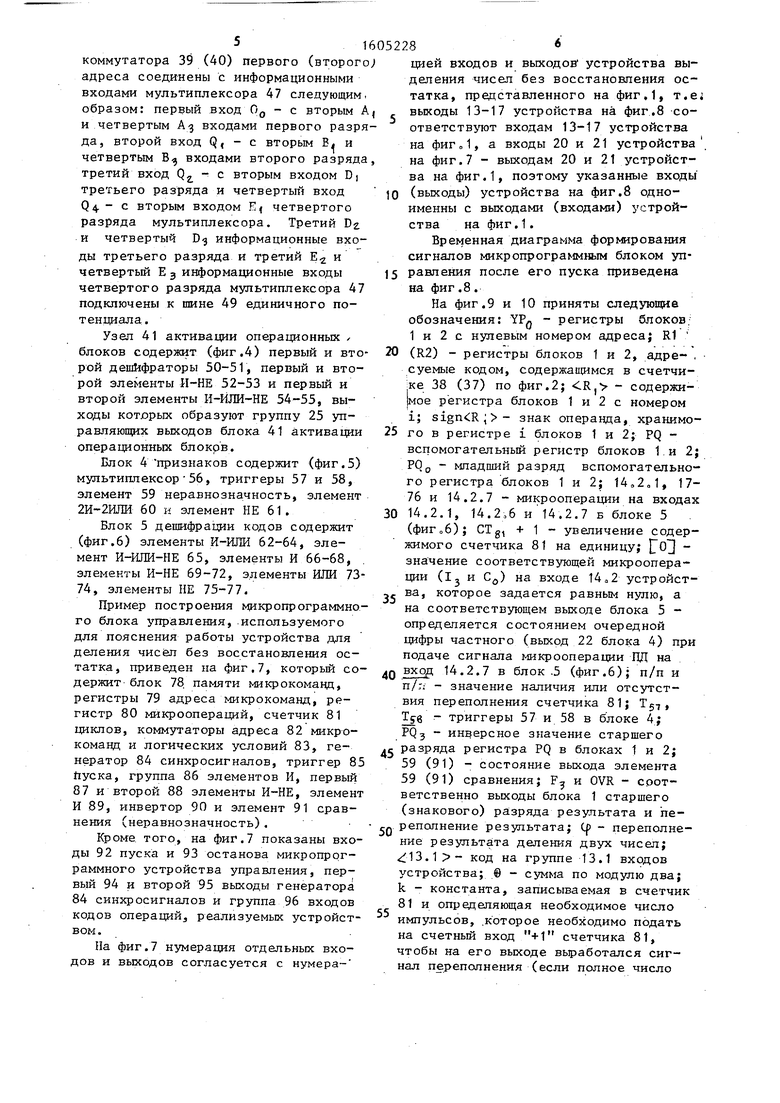

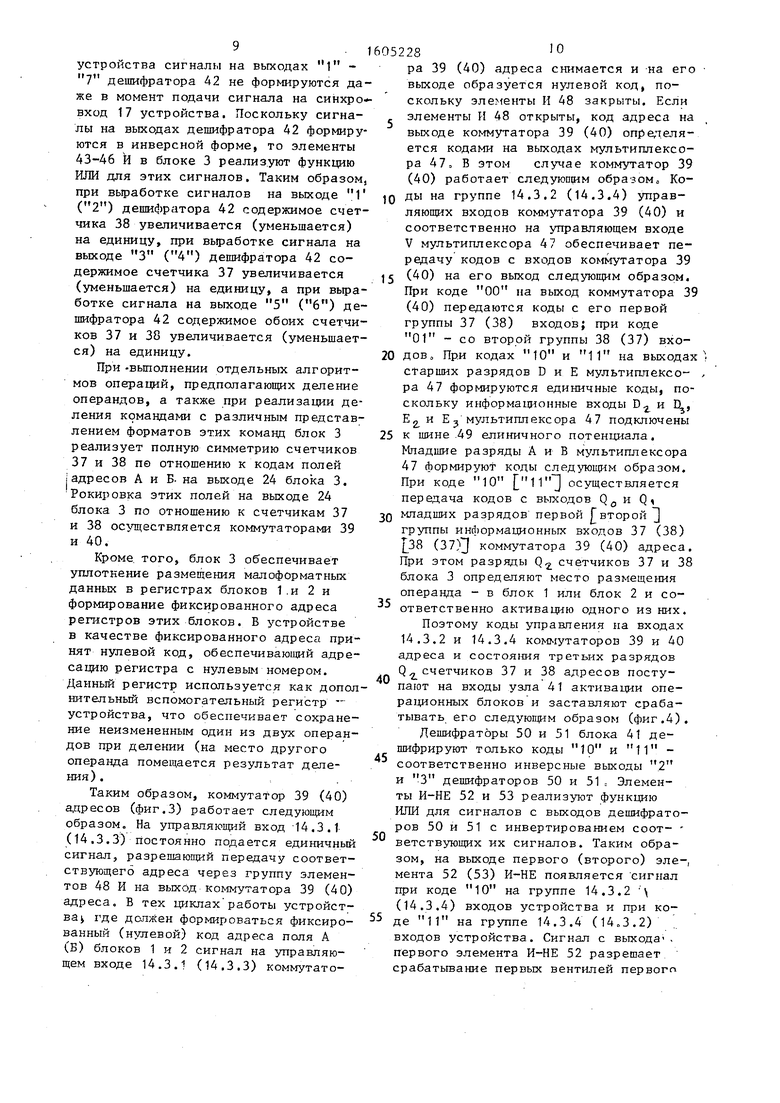

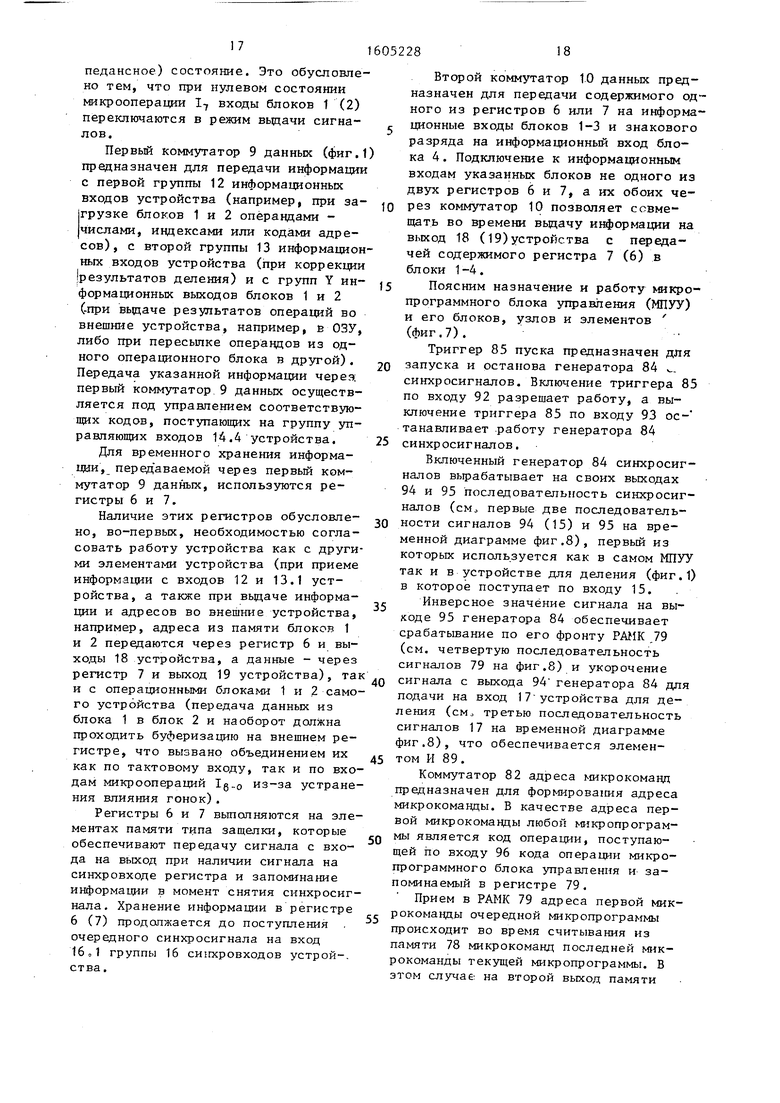

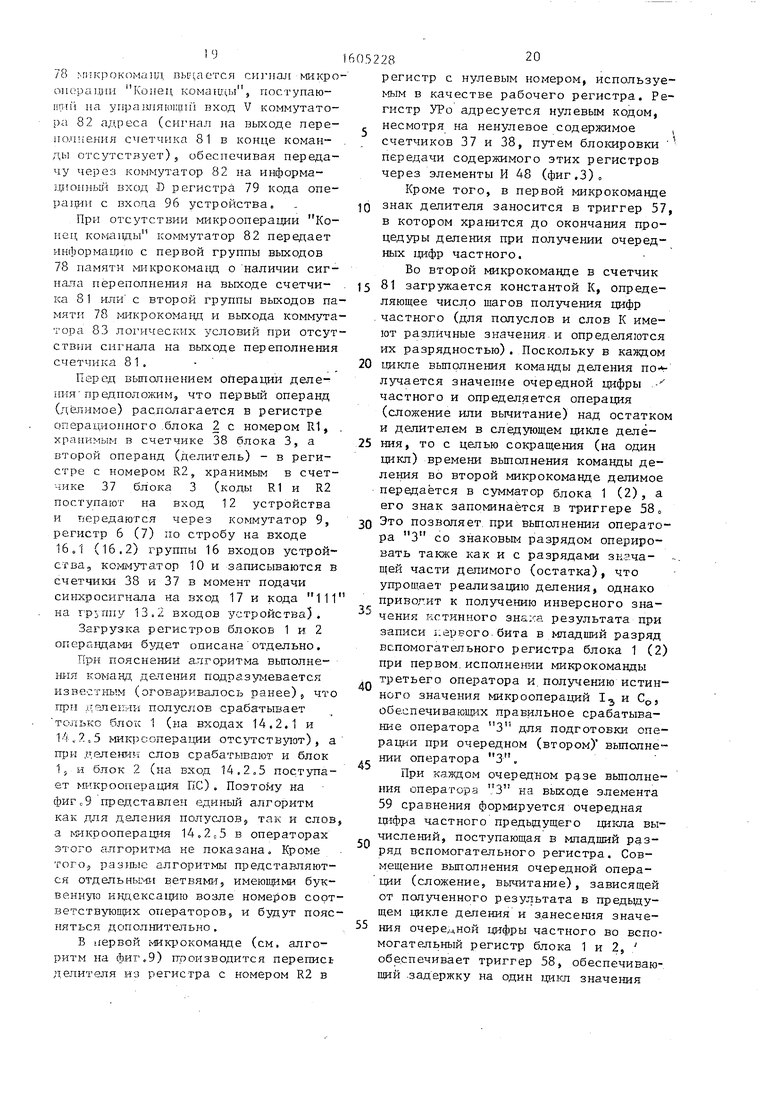

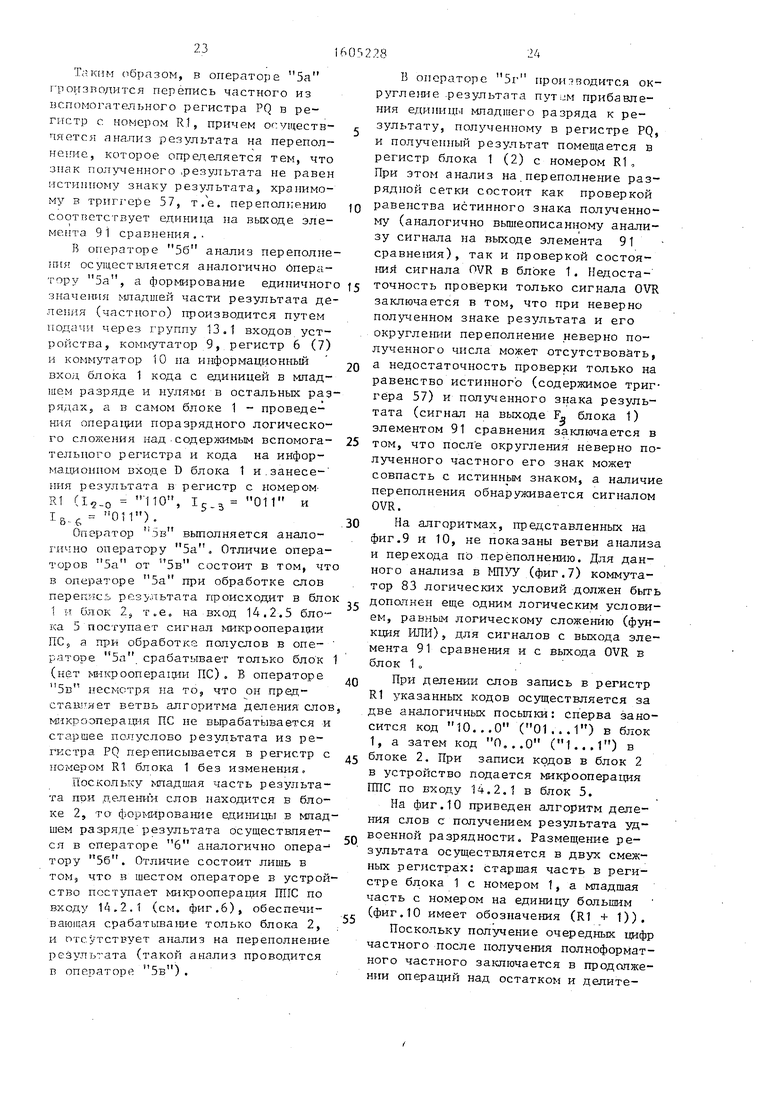

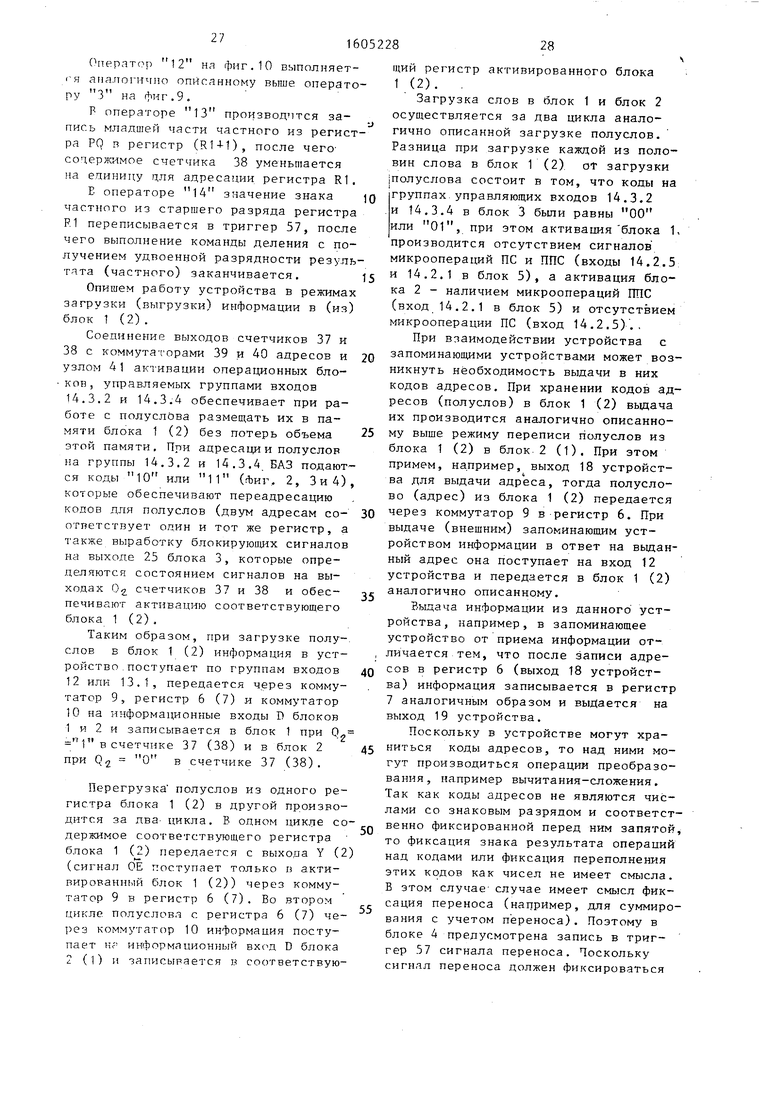

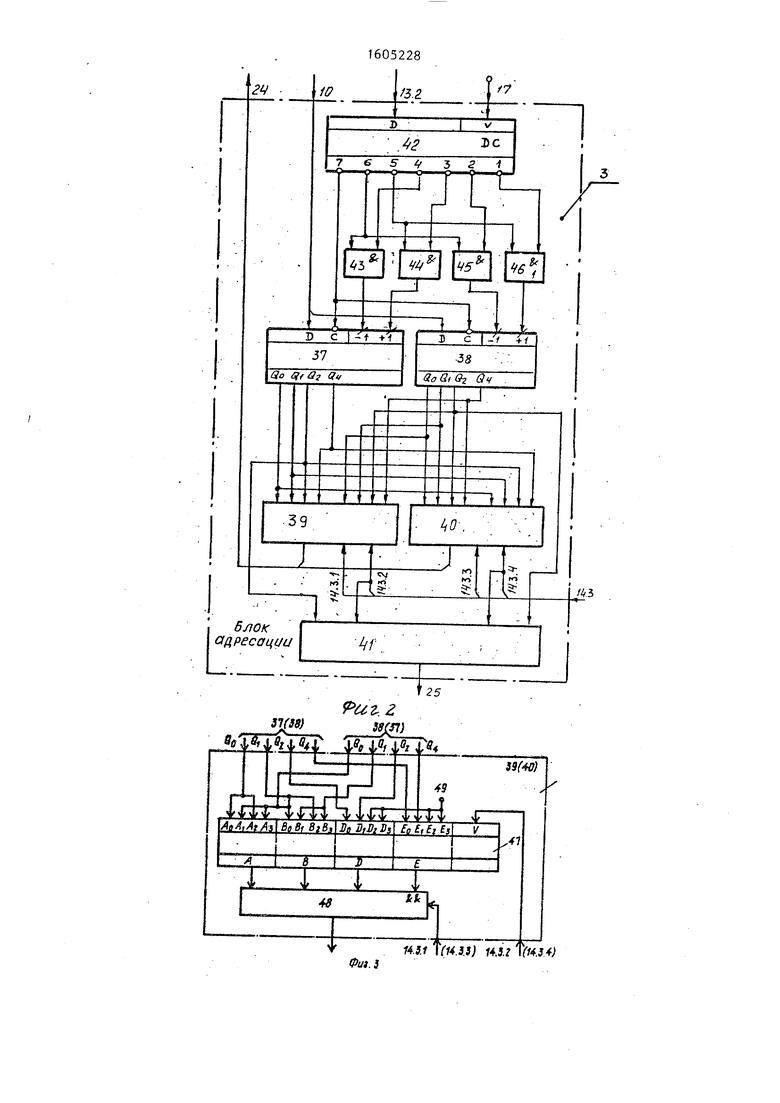

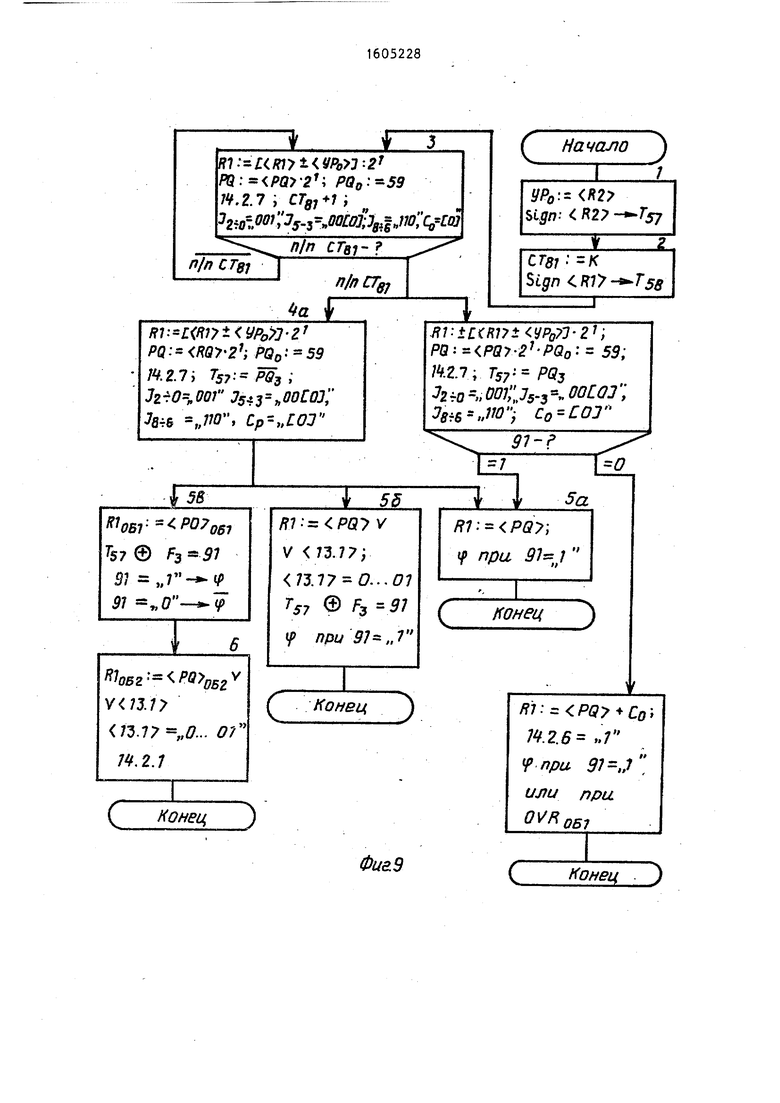

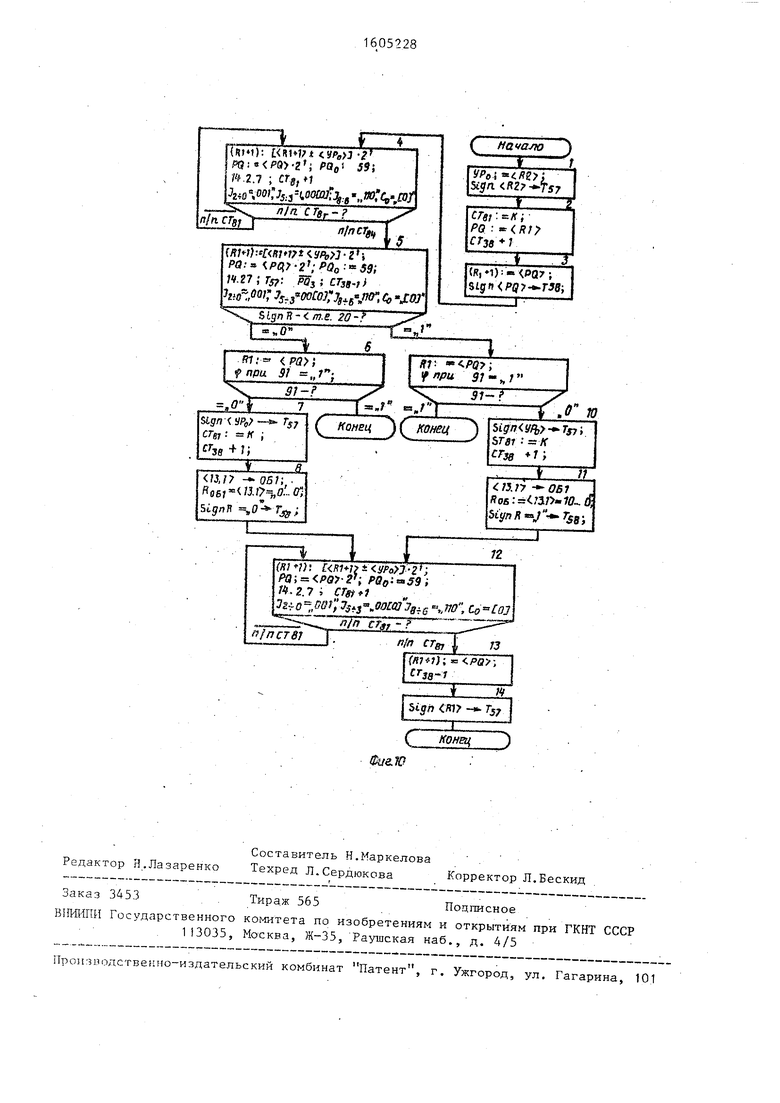

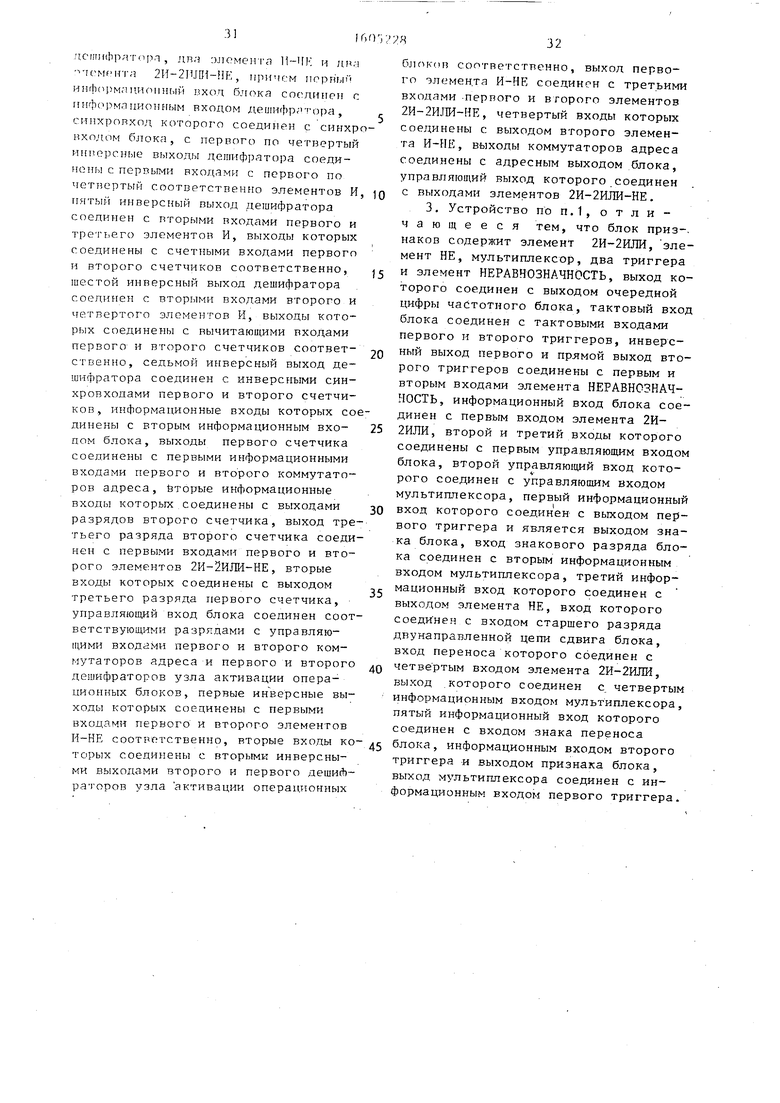

Па фиг,1 представлена функциональная схема устройства; на фиг.2 - структурная схема выполнения блока адресащм; на фиг. З, 4. - структурные схемы коммутатора адреса и узла акти- вад1ш операщ1онных блоков, входящие в состав блока адресации|..на фиг.5 - структурная схема блока признаков; на фиг.6 - структурная схема преобразователя кодовJ на фиг.7 - схема микропрограммного блока управления; на фиг,8 - временные диаграммы сигналов н-икропрограммного блока управления| на фи1 -.9 - алгоритм выполнения команды делеьшя, различные ветви которого определяют различные способы округления результата при различных форматах опера иов; на фиг , 10 - алгоритм вы- полненгш команды р,еления с получени- ем результата удвоенной разрядности

Цепи начальной установки элементов памяти устройства либо цепи отдельных, узловд не оговоренные в описании работы устройстваJ условно не показаны.

Устройство для деления чисел без восстановления остатка (фиг,1) содержит второй 1 и первый 2 операщ-юнные блоки, блок 3 адресации, блок 4 признаков блок 5 дешифрации кодов, первый 6 и второй 7 регистры, первый, второй. и. третий коммутаторы 8-10 и группу элементов И 11, информационные входы 12 первой группы, информащонные входы 13 второй группы, состоящие из входов 13.1 и 13,2s управляющие входы 14, состоящие из входов 14„1, 14.2, 14.3 и 14.4 и входа 14.5j, тактовый вход 15 устройства, синхровходы 16,1 и 16,2, синх- ровход 17 устройства, вбкоды 18-19 первьй и второй групп устройства, выходы признака 20 и знака 21, выход 22 очередной 1дафры частного блока 4 признаков, выход 23 знакового разряда коммутатора 10, адресные и управляющие выходы 24-25 блока 3 адресации, выходы блока 5 дешифраций кодов, имеющие следующую нумерацию: первый, четвертый, третий, шестой, пятьш, седьмой, восьмой, девятый и второй выходы 26- 34, вход 35 нулевого потенциала, выход 36 третьего коммутатора.

Операционные блоки 1 (2) могут быть построены на известньк элемен-

тах.,.

Блок 3 адресации содер:жит (фиг.2) второй 37 и первый 38 счетчики, коммутаторы 39 и 40, узел 41 активагщи операционных блоков, дешифратор 42, четвертьш, третий, второй и первьй элементы И 43-46.

25

30

Коммутатор 39 (40) содержит (фиг.З) четь1рехразрядный мультиплексор 47 и группу 48 элементов И, группа выходов и управляющий вход которого соединены соответственно с группой выходов и управляющим входом 14.3.1 (14.3.3) коммутатора 39 (40) первого (второго) адреса. Группа 14.3.2 (14,3.4) управляющих входов коммутатора 39 (40) первого (второго) адреса соединены с группой управляющих входов мультиплексора 47, выходы которого соединены с информационными входа ми группы 48 элементов И.

Входы QC, Q(, Q и РФ первой группы.37 (38) информационных входов коммутатора 39 (40) первого (второго) адреса соединены с информационными входами мультиплексора 47 следующим 0 образом: первый вход QQ - с первым А, и третьим Ag входами первого разряда, второй вход Q , - с первым В., и третьим Bg вxoдa и второго разряда, третий вход Q-, - с первым входом DC, тре- 5 -тьего разряда и четвертый вход о - с первым входом Е четвертого разря- да мультиплексора 47.

Входы QO, О,, Q и 0. второй группы 37 (38) информационных входов

35

0

5

коммутатора 39 (40) первого (второго адреса соединены с информационными входами мультиплексора 47 следующим, образом: первый вход Од - с вторым А и четвертым А входами первого разряда, второй вход Q, - с вторым В. и четвертым В входами второго разряда третий вход Q - с вторым входом D) третьего разряда и четвертый вход Q4. с вторым входом Е( четвертого разряда мультиплексора. Третий D и четвертый D информационные входы третьего разряда и третий Е к четвертый Е g информационные входы четвертого разряда мультиплексора 47 подключены к шине 49 единичного потенциала.

Узел 41 активации операционньк блоков содержит (фиг.4) первый и второй дешифраторы 50-51, первый и второй элементы И-НЕ 52-53 и первый и второй элементы И-ЙЛИ-НЕ 54-55, выходы которых образуют группу 25 управляющих выходов блока 41 активации операционных блокрв.

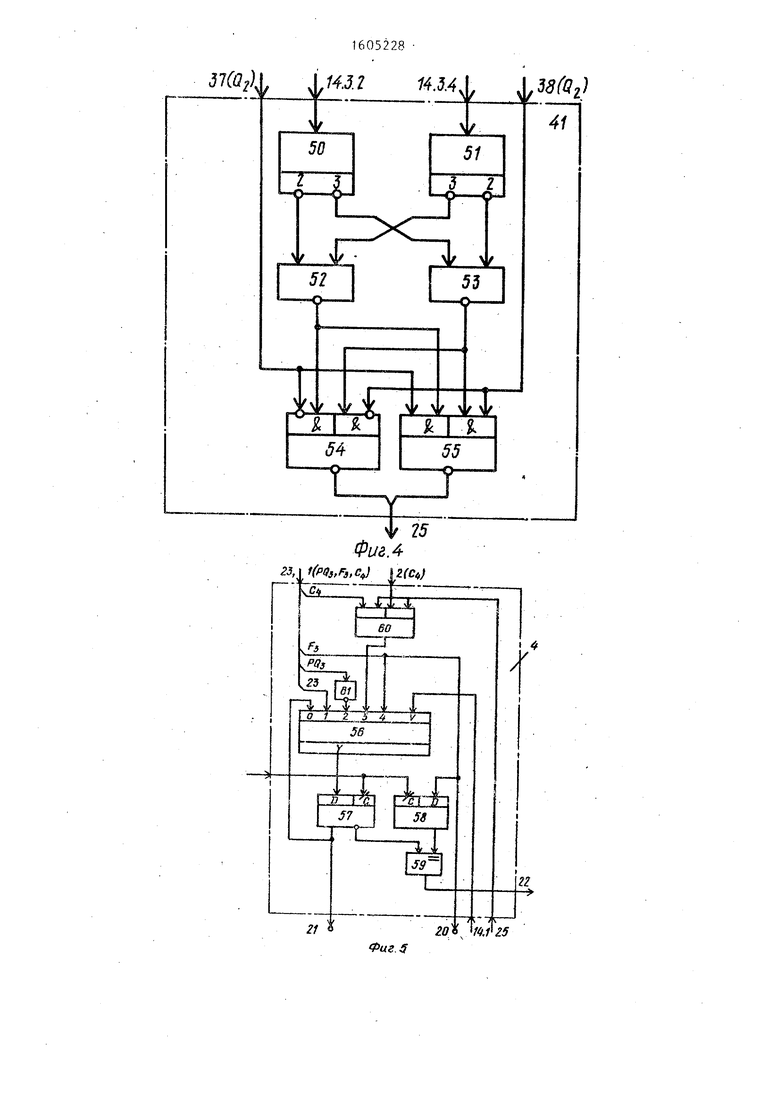

Блок 4 признаков содержит (фиг.5) мультиплексор56, триггеры 57 и 58, элемент 59 неравнозначность, элемент 2И-2ШШ 60 и элемент НЕ 61.

Блок 5 дешифрации кодов содержит (фиг.6) элементы И-ИЛИ 62-64, элемент И-ИЛИ-НЕ 65, элементы И 66-68, элементы И-НЕ 69-72, элементы ШШ 73- 74, элементы НЕ 75-77.

Пример построения микропрограммного блока управления, используемого для пояснения работы устройства для деления чисел без восстановления ос-

На фиг.9 и 10 приняты следующие обозначения: УРд - регистры блоков 1 и 2 с нулевым номером адреса; R1 20 (R2) - регистры блоков 1 и 2, адресуемые кодом, содержащимся в счетчи |ке 38 (37) по фиг.2; R, - содержи |мое регистра блоков 1 и 2 с номером i; знак операнда, храним 25 го в регистре i блоков 1 и 2; PQ - вспомогательный регистр блоков 1.и РОд - мпадший разряд вспомогательн го регистра блоков 1 и 2; 14„2о1, 1 76 и 14.2.7 - микрооперации на вход 30 14.2.1, 14.2.6 и 14.2.7 в блоке 5 (фиг об) I CTg, + 1 - увеличение соде жимого счетчика 81 на единицу; значение соответствующей микроопера ции (Ij и Сд) на входе 14„2 устройс с ва, которое задается равным нулю, а на соответствующем выходе блока 5 - определяется состоянием очередной цифры частного (выход 22 блока 4) п подаче сигнала микрооперации ГЩ на

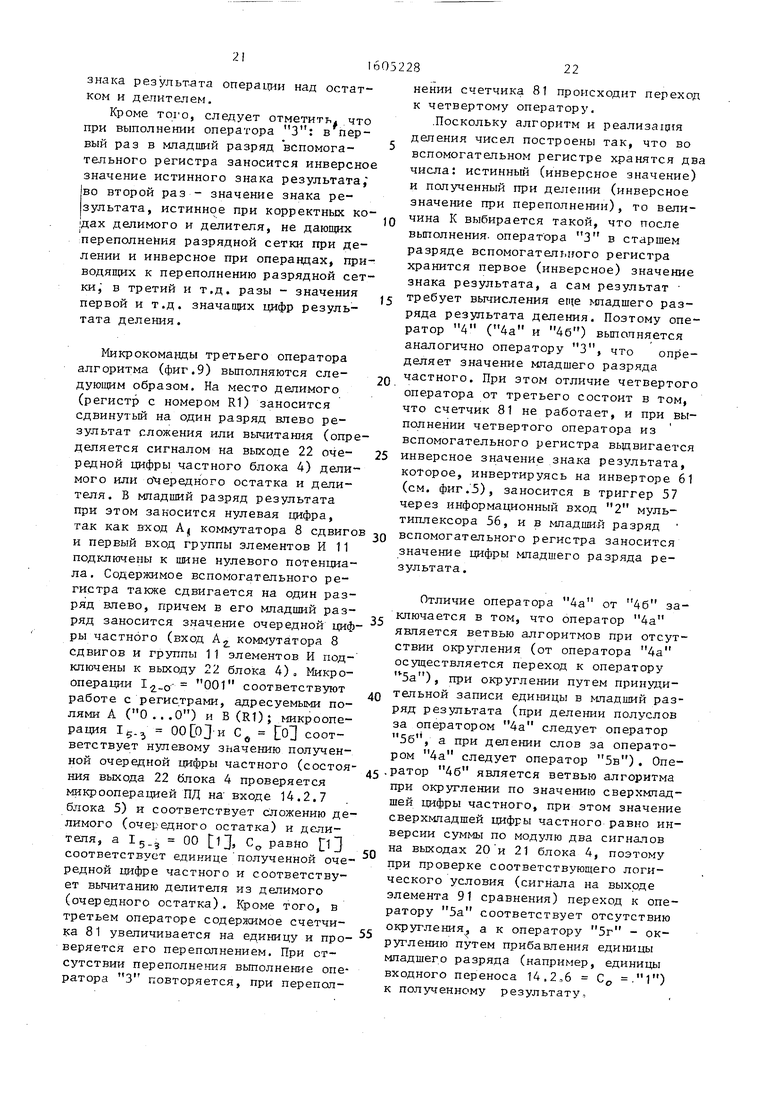

татка, приведен на фиг.7, которьй со- Q вход 14.2.7 в блок-5 (фиг.6); п/п и

держит блок 78. памяти микрокоманд, регистры 79 адреса микрокоманд, регистр 80 микроопераций, счетчик 81 циклов, коммутаторы адреса 82 микро- комацд и логических условий 83, генератор 84 синхросигналов, триггер 85 йуска, группа 86 элементов И, первый 87 и второй 88 элементы И-НЕ, элемент И 89, инвертор 90 и элемент 91 сравнения (неравнозначность).

Кроме того, на фиг.7 показаны входы 92 пуска и 93 останова микропро - раммного устройства управления, первый 94 и второй 95 выходы генератора 84 синхросигналов и группа 96 входов кодов операций, реализуемых устройством.

На фиг.7 нумерация отдельных входов и выходов согласуется с нумерап/г; - значение наличия или отсутствия переполнения счетчика 81; TJT, - триггеры 57 и 58 в блоке 4; Ррз - инверсное значение старшего д5 разряда регистра PQ в блоках 1 и 2; 59 (91) - состояние выхода элемента 59 (91) сравнения; F и OVR - соответственно выходы блока 1 старшего (знакового) разряда результата и пе- 2Q реполнение результата; Cf - переполне ние результата деления двух чисел; :::13. код на группе 13.1 входов устройства; © - сумма по модулю два; k - константа, записываемая в счетчи 81 и определяющая необходимое число импульсов, .которое необходимо подать на счетный вход +1 счетчика 81, чтобы на его выходе выработался сигнал переполнения (если полное число

55

цией входов и выходов устройства выделения чисел без восстановления остатка, представленного на фиг,1, T.ei выходы 13-17 устройства на фиг.8 соответствуют входам 13-17 устройства на фиг о 1, а входы 20 и 21 устройства на фиг.7 - выходам 20 и 21 устройства на фиг.1, поэтому указанные входы (выходы) устройства на фиг.8 одно- именны с выходами (входами) устройства на фиг.1.

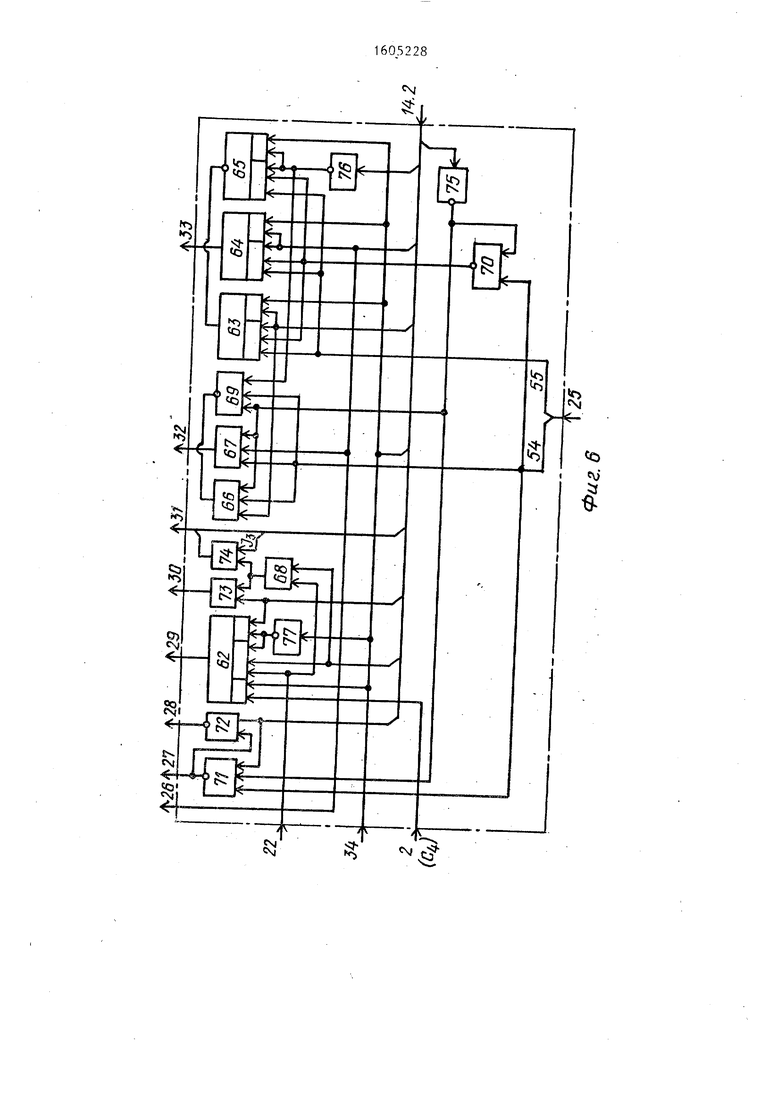

Временная диаграмма формирования сигналов микропрограммным блоком уп- равления после его пуска приведена на фиг.8.

На фиг.9 и 10 приняты следующие обозначения: УРд - регистры блоков. 1 и 2 с нулевым номером адреса; R1 (R2) - регистры блоков 1 и 2, адре , суемые кодом, содержащимся в счетчи- |ке 38 (37) по фиг.2; R, - содержи- |мое регистра блоков 1 и 2 с номером i; знак операнда, хранимо- го в регистре i блоков 1 и 2; PQ - вспомогательный регистр блоков 1.и 2; РОд - мпадший разряд вспомогательного регистра блоков 1 и 2; 14„2о1, 17- 76 и 14.2.7 - микрооперации на входах 14.2.1, 14.2.6 и 14.2.7 в блоке 5 . (фиг об) I CTg, + 1 - увеличение содержимого счетчика 81 на единицу; - значение соответствующей микрооперации (Ij и Сд) на входе 14„2 устройст- ва, которое задается равным нулю, а на соответствующем выходе блока 5 - определяется состоянием очередной цифры частного (выход 22 блока 4) при подаче сигнала микрооперации ГЩ на

вход 14.2.7 в блок-5 (фиг.6); п/п и

Q вход 14.2.7 в блок-5 (фиг.6); п/п и

п/г; - значение наличия или отсутствия переполнения счетчика 81; TJT, - триггеры 57 и 58 в блоке 4; Ррз - инверсное значение старшего д5 разряда регистра PQ в блоках 1 и 2; 59 (91) - состояние выхода элемента 59 (91) сравнения; F и OVR - соответственно выходы блока 1 старшего (знакового) разряда результата и пе- Q реполнение результата; Cf - переполнение результата деления двух чисел; :::13. код на группе 13.1 входов устройства; © - сумма по модулю два; k - константа, записываемая в счетчик 81 и определяющая необходимое число импульсов, .которое необходимо подать на счетный вход +1 счетчика 81, чтобы на его выходе выработался сигнал переполнения (если полное число

5

импульсов на счетном входе -4-1 счетчика 8 1

при котором наступает переполнение,, равно 2 5 где г - разрядность счетчика 81, то соотношение мелу1;у К и задаваемым числом циклов m соответствует выражению m 2 - К; (R1 -I- 1) - увеличенное на со дср/кимое счетчика 38, .адресующее регистры блоков 1 и 2,с номером, на болышм исходно заданного номера; СТзд -I- 1 и СТзв - увеличение и уменьшение на единицу содержимого счетчика 38 (фиг.2); sign - знак результата операции, т.е. состояние сигнала на выходе F блока 1 млн па выходе 20 блока 4| R, - ре- зульч ат опсратди в блоке 1 „

Перед описанием работы устройства для деления чисел без восстановления остатка в целом опишем, назначение и рггботу отдельньЕ блоков, узлов и элементов устройства.

Блоки 1 и 2 предназначены для приема, хранения, преобразования, в частности, деления чисел и вьщачи информации и сигналов признаков под воздействием сигналов, подаваемых на BKo,ij,bn Ср - иходного переноса, ОВ - считывания информации из блоков 1 и -3 микроопераций управления (.-3 определяет выполняемые в бло- ках 1 и 2 действия - сложение, вьгчи- таш-ie и др., а определяет источники информагщи (операндов) для этих i е:1-:тЕнй;, Ig. микроопераций, указывающих куда и каким образом производится запись результата и выдача информации на выход Y .блоков 1 и 2. Указанные входные воздействия воспринимаются и вьтолняются под уп- раглеHvtciH тактирз.тос1его си гнала на , Taivi OROM входе Т,- При по.даче сигнала (низкого уро-ння) на вход ОЕ блоков 1 и 2 его информация вьдается на группу Y информа :1ионных входов а признаки результатов (С.. - выходкой перенос, Т - старики (знаковый) разряд результата, ОТО - переполнение) - па соответствующие выходы блоков 1 и 2:, Информа1.щя старших разря.дов сдвигаемой при делении информации выдается по выходам PR 3 и РО j, а мпад- iiaix разрядов - принимается по входам PR о и PQ,,.-.

Блок 3 предназначен для организации адресации регистров ОБ 1 (2) в процессе вычислений, а также для актива г.щи блоков 1 и 2 в процессе их

10

5

0

5

0

5

5

0

5

функционирования,. Данная активация обусловлена тем, что в процессе функционирования устройства долж1ш активироваться на определенную работу либо оба блока 1 и 2,либо один из блоков 1 и 2, либо оба не должны быть активными. Для этой цели может использоваться тактовый вход Т каждого блока 1 и 2, управляемый соответствующими микрооперациями. Однако гонки в ключах разрешения подачи сигна-, лов на тактовые входы Т, обладающих высоким быстродействием, могут привести к сбоям в.работе блоков 1 и 2.

В устройстве тактовые входы Т обоих блоков 1 и 2 объединены между собой тактовым входом 15 устройства, на который постоянно подаются тактирующие сигналы. Несрабатывание блоков 1 или 2, при необходимости, в данном устройстве рассматривается как цода- ча кода 001 на вход , при котором элементы памяти не изменяют своего состояния. Сигналы блокировки срабатывания одного из блоков 1 и 2 формируются в узле 41 активации опе- раодонных блоков, а условия их формирования будут опис.аны ьшже.

Регистры в блоках 1 и 2 адресуются двумя полями адресов А и S,.поэтому в блоке 3 для их адресации используются счетчик 37-адресов поля А и счетчик 38 адресов поля В блоках 1 и 2. Занесение исходных адресов полей А и В в блок 1 или 2, в счетчики 37 и 33 б.г-ока 3 производится при подаче на их информационные входы D соответстЕ поп1л:х кодов с выхода второго коммутатора 10 данных, подачи кода 111 на информационный вход D де.шнфратора 42 с входов 13.2 .устрой- |Ствз. и подачи синхросигнала на управляющий вход V дешифратора 42 с синх- ровхода 17 устройства. При этом на инверсном выходе 7 дешифратора 42 вьгоабатывается сигнал (низкого уровня), которьш поступает на синхровхо- ды с счетчиков 37 и 38 и обеспечивает в них нанесение упомянутых кодов начальных адресов Таким образом, сигналы на одном из выходов 1 - 7 дешифратора 42 вырабатываются только в момент подачи сигнала на синхровход 17 устройства, прич вм код на входе 13,2 устройства определяет один из выходов 1 - 7 дешифратора 42, на котором вырабатывается сигнал. При нулевом коде на входе 13.2

9.

устройства сигналы на выходах 1 - 7 дешифратора 42 не формируются даже в момент подачи сигнала на синхро вход 17 устройства. Поскольку сигналы на выходах дешифратора 42 формируются в инверсной форме, то элементы 43-46 И в блоке 3 реализуют функцию ИЛИ для этик сигналов. Таким образом при выработке сигналов на выходе Г (2) дешифратора 42 содержимое счетчика 38 увеличивается (уменьшается) на единицу, при выработке сигнала на выходе 3 (4) дешифратора 42 содержимое счетчика 37 увеличивается (уменьшается) на единицу, а при вьфа ботке сигнала на выходе 5 (6) дешифратора 42 содержимое обоих счетчиков 37 и 38 увеличивается (уменьшается) на единицу.

При -выполнении отдельных алгоритмов операций, предполагающих деление операндов, а также при реализации деления командами с различным представлением форматов этих команд блок 3 реализует полную симметрию счетчиков 37 и 38 пе отношению к кодам полей (адресов А и Б. на выходе 24 блока 3. Рокировка этих полей на выходе 24 блока 3 по отношению к счетчикам 37 и 38 осутцествляется коммутаторами 39 и 40.

Кроме, того, блок 3 обеспечивает уплотнение размещения малоформатных данных в регистрах блоков 1.и 2 и формирование фиксированного адреса регистров этих блоков. Б устройстве в качестве фиксированного адреса принят нулевой код, обеспечивающий адресацию регистра с нулевь г номером. Данный регистр используется как допол нитепьный вспомогательный регистр - устройства, что обеспечивает сохранение неизмененным один из двух операндов при делении (на место другого операнда помещается результат деления) .

Таким образом, коммутатор 39 (40) адресов (фиг.З) работает следующим образом. На управляющий вход -14.3.1 (14.3.3) постоянно подается единичный сигнал, разрешаюпщй передачу соответствующего адреса через группу элементов 48 И на выход коммутатора 39 (40) адреса. В тех циклах работы устройст- ва где даплген формироваться фиксированный (нулевой) код адреса поля А (Б) блоков 1 и 2 сигнал на управляющем входе 14.3.1 (14.3.3) коммутато

60522810

ра 39 (40) адреса снимается и на его выходе образуется нулевой код, поскольку эле тенты И 48 закрыты. Если , элементы И 48 открыты, код адреса на выходе коммутатора 39 (40) определяется кодами на выходах мультиплексора 47, В этом случае коммутатор 39 (40) работает следуюпим образом Ко- Q ды на группе 14.3.2 (14.3.4) управ- ляюшлх входов коммутатора 39 (40) и соответственно на управляющем входе V мультиплексора 47 обеспечивает передачу кодов с входов коммутатора 39 15 () на его выход следующим образом. При коде 00 на выход коммутатора 39 (40) передаются коды с его первой группы 37 (38) входов; при коде 01 - со второй группы 38 (37) вхо- 20 дов При кодах 10 и 11 на выходах f старших разрядов D и Е мультиштексо- , ра 47 формируются единичные коды, поскольку информационные входы D и EL, Eg и Ej мультиплексора 47 подключены 25 к шине .49 елиничного потенциала.

Младшие разряды А и В мультиплексора 47 формируют коды следуюш 1м образом. При коде 10 11 осуществляется передача кодов с выходов Q и Q, 30 младших разрядов первой Гвторой J группы информационных входов 37 (38) (37) коммутатора 39 (40) адреса. При этом разряды Q счетчиков 37 и 38 блока 3 определяют место размещения операнда - в блок 1 или блок 2 и соответственно активацию одного из них. Поэтому коды управления па входах 14.3.2 и 14.3.4 коммутаторов 39 и 40 адреса и состояния третьих разрядов 40 Q-z. 37 и 38 адресов поступают на входы узла 41 активации операционных блоков и заставляют срабатывать его сле.дующнм образом (фиг.4).

Дешифраторы 50 и 51 блока 41 дешифрируют только коды 10 и 11 - соответственно инверсные выходы 2 и 3 дешифраторов 50 и 51 Элементы И-НЕ 52 и 53 реализуют функцию ИЛИ для сигналов с выходов дешифраторов 50 и 51 с инвертированием соот- ветствующих их сигналов. Таким образом, на выходе первого (второго) эле-, мента 52 (53) И-НЕ появляется сигнал при коде 10 на группе 14.3.2 (14.3.4) входов устройства и при ко- 5 де 11 на группе 14.3.4 (14.3.2) входов устройства. Сигнал с выхода , первого элемента И-НЕ 52 разрешает срабатьтание первых вентилей первого

54 И второго 55 элементов И-ИЛИ-НЕ,а сигнал с выхода второго элемента II-IiE 53 разрешает срабатывание вторы вентилей этих же элементов И-ИЛИ-НЕ 55. Формирование сигналов одновременно на выходах и первого 52 и второго 53 элементов И-НЕ не должно производиться5 поскольку невозможно мгновенное взаимодействие двух операндов, размещенных в разных блоках 1 и 2„ Такое взаимодействие должно произволиться за два гщ-кла в одном из которых, например втором, операнд вьщается из блока 2 (1) через коммутатор 9 И фиксируется в одном из регистров 6 или 7. Во втором цикле это операггд из регистра 6 (7) . передается через коммутатор 10 в блок 1(2), в котором он и взаимодействует с другим операндом. Таким образом , коды на входах..2 и 14.3.4 формируются так, что сигнал может вырабаты- , ваться только ,на выходе одного из элементов И-НЕ 52 или 53, при этом / нулевое значение выхода Q счетчика 37 рши 38 обеспечит появление низког :,Фовня сигнала на выходе первого эле мента И-ИЛИ-НЕ 54, а единичное значе Ш1е выхода Q j счетчика 37 и 38 - на выходе второго элемента И-ИЛИ-НЕ 55. В первом случае блокируется блок 1 и активируется блок 2, а во втором случае наоборот.

Блок 4 предназначен (фиг.5) для хранения истинного значения знака рез1.71ьтата операций в триггере 57 (в блоке 1 получение истинного знака ре з щьтата не обеспечивается при пере- полнешет результатов операций над cnepai- aivui в блоках 1 и 2) , В триггер 57 заносится знак опер андов, примир депителей,, загружаемых в операционные блоки (разряд 23 выхода коммутатора 10), истинное значение знака результата деления, загружаемо с выхода РО, блока 1, значение знака результатов операций, загружаемых с выхода F блока 1, а также значе1шя сигналов переносов С при обработке малоформатных кодов с выхода элемен- та 60, при этом сигналы на выходах элементов И-ИЛИ-НЕ 54 и 55 поступают в блок 4 через вторую группу 25 управляющих входов и определяют., какой из операционных блоков ак тивирован; т.е. откуда должен восприниматься сигнал С выходного переноса. Один из перечисленных источников

5

информации для триггера 57 задается соответствующим кодом на первой группе 14.1 управляющих входов БПА и управляющем входе V мультиплексора 56, причем при нулевом коде на этом входе содержимое триггера 57 не изменяется, что обеспечивается обратной связью с выхода триггера 57 на его информационный вход D через мультиплексор 56. Значение истинного знака результата, хранимое в триггере 57, может быть использовано, например, при переполнении результата вычислений. В этом результат вычислений может быть заменен максимальным по модулю машинным числом 10.,. ...О для отрицательного значения результата и числом 01-1 для поло0 жительного значения результата.

В триггере 58 в течение одного цикла работы устройства (определяется периодом следования тактов на входе 15 устройства) хранится значение

5 очередного результата вычислений (например, деления). При хранении в процессе деления чисел в триггере 57 знака делителя его инверсное значение и значение знака очередной one- рации в блок 1 (2) при выполнении деления, поступающие на входы элемента 59 сравнения, .обеспечивают формирование на его выходе и на выходе 22 блока 4 значения очередной цифры частного и определяют очередную операцию (сложение или вычитание) над.остатком и делителем.

Кроме того, значения сигналов на выходах 20 и 21 блока 4 определяют возможность ветвления микропрограмм при выполнении соответствующих микрокоманд (будет пояснено при описании вьшопнения команд деления) .

Блок 5 дешифрации кодов ( фиг.4) предназначен для формирования управляющих сигналов блоков 1 и 2, комьгу- татора 8 и группы 11 элементов И, зависимости от состава обрабатываемых данных (состояние выходного переноса блока 2 и очередной цифры частного - выход 22 блока 4) или от сигналов активап и блоков 1 и 2, формируемых на выходе блока 25 блока 3 (выходы элементов И-ИЛИ-НЕ 54 и 55), Исходное значение кодов управления блоков 1, 2, коммутатора 8 и группы элементов 11- поступает в блок 5 с группы управляющих входов 14.2, а ис-- тинное значение кодов управления эти0

5

0

5

0

5

ми узлами устройства формируется на выходах 26-34 блока 5 с учетом состояния сигналов на .выходе 25 блока 3 выходе 22 блока 4 и выходе С блока 2 следуюпц м образом.

Активация работы блоков 1 и 2 производится как безусловно сигналами на соответствуюищх входах группы 14.2 входа в устройство, так и условно в зависимости от состояния сигналов на (фиг.2 и 4) входах 14.3.2 и 14.3.4 в устройство и состояния кодов адресов (на выходах Q счетчиков 37 и 38), определяющих сигналы на входах 25 блока 5.

При поступлении (низкого уровня) сигнала по входу 54 группы входов 25 блока 5 блокируется активация блока 1 (на группе 32 выходов 1д блока 5 формируется код 001 и на выходе 27 единичный сигнал, т.е. заблокирована выработка сигнала ОЕ для блока 1) и разрешается активация блока 2, на выВходы 14.2.2, 14.2.3 и 14.2.4 бло- 10 ка 5 соответствуют управляющим сигналам Ig.g операцг онных блоков и передаются только на группу 32 вькодов блока 5(на выходы элементов 66 и 67 И и 69 И-НЕ) при отсутствии сигналов J5 на входах 14.2.1 и 14.2.5, только на группу 33 выходов блока 5 (на выходы элементов 63 и 64 И-ИШ и 65 И-ИЛ11- НЕ через вторых их вентили) при наличии сигнала ППС на входе 14.2.1 бло- 20 ка 5, а также на обе группы 32 и 33 выходов блока 5 (на выходы элементов И-11ПИ 63 и 64 и И-ШШ-НЕ 65 данные сигналы передаются через их первые вентили) при наличии сигнала на

30

раций деления, передается на выход 26 блока 5 и соответственно на блокирующие входы и коммутатора 8 сдвигов и группы 11 элементов И.

Группа 14.2.9 входов блока 5 фор- М1фует микрооперации Ig-o Л блоков 1 и 2 и передается на выходы 31 блоходе элемента И-НЕ 70 вьфабатывается 25 входе 14.2.5. Кроме того, единичный

сигнал, разрешающий срабатывание вто- сигнал микрооперации I,, определяюрых вентил ей элементов ИЧШИ 63 и сдвиг влево при выполнении опеи элемента 65 Р1-ИЛИ-НЕ; срабатывание

элемента И-НЕ 72 разрешается высоким

уровнем сигнала на выходе элемента

И-НЕ 71). При поступлении сигнала по

входу 55 группы 25 входов блока 5

блокируется активация блока 2 через

вторые вентили элементов И-ИЛИ 63 и

2 ка 5, причем микрооперация 1з передается через элемент ИЛИ 74. Поскольку в делении в зависимости от полученной очереднор цифры частного производится сложение или вьгчитазше остат-

40 ка и делителя, то микрооперация Ig является-условной-(для блоков 1 и 2 15.3 соответствует сложению и Т5-з вычитанию остатка и делителя) . В этом случае ьогкрооперация

45 1з в группе 14.2.9 входов бло-ка 5 равна нулю, а на входе 14.2.7 вырабатывается микрооперация (назовем ее

Блокировка активации блока 1 и разрешение активации блока 2 безусловно производятся сигналом микрооперации на входе 14.2.1 блока 5, т.е. признаком полуслова (ППС), инвертируемым элементом НЕ 75, аналогично тому, как это производится выше описанным сигналом на входе 54 группы входов 25 блока 5,

При активации одновременно блоков 1 и 2 на вход 14.2.5 блока 5 подается сигнал - признаком слова (ПС). При подаче сигнала ПС по входу 14.2.5 блока 5 сигналы (низкого уровня) на входах 54 и 55 группы входов 25 от- . сутствуют.

Для активации только блока V (в дальнейшем предполагаем отсутствие сигналов низкого уровня на входах 54

в дальнейшем признаком деления (ПД)), проверяющая условие истинного значе- JQ ния Ij для блоков 1 и 2, зависящего от значения полученной очередной цифры частного. В данном случае истинное значение микрооперации 1 формируется на выходе элемента И 68, а значит и на соответств тощем выходе

и 55 группы 25 входов, наличие сигналов на этих входах будет оговаривать- 5 группы выходов 31 блока 5.

ся особо; сигналы на входах 14.2, и

14.2.5 должны отсутствовать, что

обеспечит блокировку срабатывания

Поскольку при вычитании (is-j 001) должен формироваться сигнал входного переноса Сов блоках 1 и 2,

пер в ых вентилей элементов И-ИЛИ 63 и 64 и элемента 65 отсутствием сигнала на входе 14.2.5 блока 5, а вторых вентилей - отсутствием сигнала на выходе элемента И-НЕ 70. При этом на выходе 33 блока 5 будет сформирован код 001.

Входы 14.2.2, 14.2.3 и 14.2.4 бло- ка 5 соответствуют управляющим сигналам Ig.g операцг онных блоков и передаются только на группу 32 вькодов блока 5(на выходы элементов 66 и 67 И и 69 И-НЕ) при отсутствии сигналов на входах 14.2.1 и 14.2.5, только на группу 33 выходов блока 5 (на выходы элементов 63 и 64 И-ИШ и 65 И-ИЛ11- НЕ через вторых их вентили) при наличии сигнала ППС на входе 14.2.1 бло- ка 5, а также на обе группы 32 и 33 выходов блока 5 (на выходы элементов И-11ПИ 63 и 64 и И-ШШ-НЕ 65 данные сигналы передаются через их первые вентили) при наличии сигнала на

входе 14.2.5. Кроме того, единичный

раций деления, передается на выход 26 блока 5 и соответственно на блокирующие входы и коммутатора 8 сдвигов и группы 11 элементов И.

Группа 14.2.9 входов блока 5 фор- М1фует микрооперации Ig-o Л блоков 1 и 2 и передается на выходы 31 блов дальнейшем признаком деления (ПД)), проверяющая условие истинного значе- ния Ij для блоков 1 и 2, зависящего от значения полученной очередной цифры частного. В данном случае истинное значение микрооперации 1 формируется на выходе элемента И 68, а значит и на соответств тощем выходе

группы выходов 31 блока 5.

Поскольку при вычитании (is-j 001) должен формироваться сигнал входного переноса Сов блоках 1 и 2,

то при срабатывании элемента И 68 на выходе 30 блока 5 таюке .формируется сигнал входного переноса С для блока 2 ,

Сигнал GO входного переноса для

блока 2 формируется на вькоде 30 блока 5 либо условно сигналом с выхода элементе И 68 (при формировании сигнала ПД на входе 14.2.7 блока .5), либо безусловно сигналом, поступающим на входы 14.2.6. При этом сигнал С для блока 2 используется только при активации блока 2.

Сигнал Сд входного переноса для блока 1 должен быть равен сигналу С-. выходного переноса блока 2 в случае одновременной активации и блока 1 и блока 2 (обработка в устройстве слов, определяемая наличием сигнала ПС на входе 14.2,5 блока 5). В этом случае сигнал ПС на входе 14.2.5 блока 5 через элемент НЕ 77 запрещает срабаты- ;вание второго и третьего вентилей элемента И-1ШИ 62 и разрешает переда- чу сигнала через первьй вентиль элемента И-ИЛИ 62 с выхода С блока 2 на выход 29 блока 5 (вход С блока 1)

При активации только блока 1 закрыт первый вентиль элемента И-ИПИ 62 и открыты его второй и третий вентиль сигналом с вьтхода элемента НЕ 77. При этом при безусловном формировании сигнала С на выходе 29 блока 5 на его входе 14о2,6 формируется сигнал, которьй на выход 29 блока 5 передается через второй вентиль элемента И-ИЛИ 62. При условном формировании сигнала С на выходе 29 бл ока 5 .в командах деления сигналы на входах 14.2.7 и 22 блока 5 обеспечат сраба:- тываюте третьего вентиля элемента - i И.-И.ПИ 62 и вьщачу сигнала С на выход 29. .

Поскольку информационные выходы Y блоков 1 и 2 объединены между собой, то одновременное считывание и-нформации с блоков 1 и 2 недопустимо, поэтому- наличие (низкого уровня) сигнала ОЕ. считывания информации с блока 1 на выходе 27 блока 5 определяет его отсутствие на выходе 28 (выход элемента И-НЕ 71 подключен к входу элемента И-НЕ 72).

Длтя считывания информации с блока 1 (2) на вход 14.2.8 блока 5 должен поступать сигнал. При этом, если отсутствует блокировка срабатывания блока 1 (высокие уровни сигнапов на

10

15

20

25

п

5

0

5

0

5

входе 54 группы 25 входов блока 5 и на выходе элементу НЕ 75), то низкий уровень сигнала ОЕ формируется только на выходе 27, а при наличии блокировки срабатывания блока 1 (активирован только блок 2, что определяется низким уровнем сигнала на входе 54 группы 25 входов блока 2 или на выходе элемента НЕ 75) низкий уровень сигнала ОЕ вырабатывается только на выходе 28 блока 5.

Следует также отметить, что при активации блоков 1 и 2 одновременно они рассматриваются как один операционный блок с разрядностью, равной сумме разрядностей блоков t и 2. По этому сигнал ПС с входа 14.2.5 ПК по ступает через его выход 34 на управляющий вход V коммутатора 8 сдвигов, что соответствует передаче сигналов на выходы .Y. коммутатора 8 с его входов В-.

При отсутствии сигнала на входе 14.2.5 блока 5 и соот атственно на его выходе 34 коммутатор 8 сдвигов передает информацию на выходы Y- со своих входов А;. Таким образом/деление слов производится в блоках 1 и 2, а деление полуслов - в блоке 1. При сдвиге влево результата очередного цикла деления: для остатка его мпадпше разряды должны заполнять- ся нулевой информацией, а частного от деления - значением полз ецной очередной цифрой частного. Поэтому первые входы первой группы входов А коммутатора 8 сдвигов (используется при делении полуслов) и группы элементов И 11 подключены к пшне нулевого потенциала, а вторые входы - к выходу 22 очередной цифры частного блока 4. В каком из операционных блоков 1 или 2 будут восприниматься сигналы с пшны нзшевого потенциала и с выхода 22 блока 4, определяется состоянием сигнала ПС. на выходе 34 блока 5 и активацией этих блоков 2 и (или) 1.

Выходы коммз гатора 8 сдвигов и выходы группы элементов И 11 церево- дятся в активное состояние (передача сигналов со входов на выходы) только при наличии сигнала поступающего с выхода 26 блока 5 на входы W коммутатора 8 и группы 11 элементов И. Во всех остальных случаях выходы коммутатора 8 и группы элементов И 11 переводятся в отключенное (высокоим

педансное) состояние. Это обусловлено тем, что при нулевом состоянии микрооперации I-, входы блоков 1 (2) переключаются в режим вьщачи сигналов.

Первьй коммутатор 9 данных (фиг. предназначен для передачи информаци с первой группы 12 информационных входов устройства (например, при загрузке блоков 1 и 2 операндами - числами, индексами или кодами адресов), с второй группы 13 информационых входов устройства (при коррекци результатов деления) и с групп Y информационных выходов блоков 1 и 2 (-при вьщаче результатов операций во внешние устройства, например, в ОЗУ либо при пересьшке операндов из одного операционного блока в другой). Передача указанной информации через; первый коммутатор 9 данных осуществляется под управлением соответствую- П1ИХ кодов, поступающих на группу управляющих входов 14.4 устройства.

Для временного хранения информации, передаваемой через первый коммутатор 9 данных, используются регистры 6 и 7.

Наличие этих регистров обусловлено, во-первых, необходимостью согласовать работу устройства как с другими элементами устройства (при приеме информации с входов 12 и 13.1 устройства, а также при вьдаче информации и адресов во внешние устройства, например, адреса из памяти блоков 1 и 2 передаются через регистр 6 и выходы 18 устройства, а данные - через регистр 7 и выход 19 устройства), та и с операционными блоками 1 и 2 самого устройства (передача данных из блока 1 в блок 2 и наоборот должна проходить буферизацию на внешнем регистре, что вызвано объединением их как по тактовому входу, так и по входам микроопераций Ig.g из-за устранения влияния гонок).

Регистры 6 и 7 выполняются на элементах памяти типа защелки, которые обеспечивают передачу сигнала с входа на выход при наличии сигнала на синхровходе регистра и запоминание информации в момент снятия синхросигнала. Хранение информации в регистре 6 (7) продолжается до поступления . очередного синхросигнала на вход 16 о 1 группы 16 си гхровходов устрой-. ства.

18

10

15

20

25

) 30

35

40

45

0

5

Второй коммутатор 1.0 данных предназначен для передачи содержимого одного из регистров 6 или 7 на информационные входы блоков 1-3 и знакового разряда на информационный вход блока 4. Подключение к информационным входам указанных блоков не одного из двух регистров 6 и 7, а их обоих через коммутатор 10 позволяет совмещать во времени вьщачу информации на выход 18 (19)устройства с передачей содержимого регистра 7 (6) в блоки 1-4.

Поясним назначение и работу микропрограммного блока управления (МПУУ) и его блоков, узлов и элементов (фиг.7).

Триггер 85 пуска предназначен для запуска и останова генератора 84 .. синхросигналов. Включение триггера 85 по входу 92 разрешает работу, а выключение триггера 85 по входу 93 ос- танавливает работу генератора 84 синхросигналов.

Включенный генератор 84 синхросигналов вырабатывает на своих выходах 94 и 95 последовательность синхросигналов (см первые две последовательности сигналов 94 (15) и 95 на временной диаграмме фиг .8), первый из которьпс используется как в самом МПУУ так и в устройстве для деления (фиг.1) в которое поступает по входу 15.

Инверсное значение сигнала на выходе 95 генератора 84 обеспечивает срабатьшание по его фронту РАМК 79 (см. четвертую последовательность сигналов 79 на фиг.8) и укорочение сигнала с выхода 94 генератора 84 для подачи на вход 17-устройства для деления (смо третью последовательность сигналов 17 на временной диаграмме фиг.8), что обеспечивается элементом И 89.

Коммутатор 82 адреса микрокоманд предназначен для формирования адреса микрокоманды. В качестве адреса первой микрокоманды любой микропрограммы является код операции, поступающей по входу 96 кода операции микропрограммного блока управления и запоминаемый в регистре 79.

Прием в РАМК 79 адреса первой микрокоманды очередной микропрограммы происходит во время считывания из памяти 78 микрокоманд последней микрокоманды текущей микропрограммы. В этом случае на второй выход памяти

19

78 -.шгсрокомаид вычается сигнал микро onepaijjiH Конец комашсы, поступаю- imn i на упра шипоипп вход V коммутатора 82 адреса (сигнал на выходе пере- нолиения счетчика 81 в конце команды отсутствует), обеснечивая передачу через коммутатор 82 на информа- плонньш вход D регистра 79 кода опе- ращи с входа 96 устройства.

При отсутствии микрооперации Конец, команды коммутатор 82 передает информацию с первой группы выходов 78 памяти микрокоманд о наличии сигнала переполнения на выходе счетчика 81 или с второй группы выходов памяти 78 микрокоманд и выхода коммутатора 83 логических условий при отсутствии сигнала на выходе переполнения счетчика 81,

Перед вьтопнением операции деления предположим, что первый операнд (делимое) располагается в регистре операционного-блока 2 с номером R1, хранимым в счетчике 38 блока 3, а второй операнд (делитель) - в регистре с номером R2, хранимым в счетчике 37 блока 3 (коды R1 и R2 поступают на вход 12 устройства и передаются через коммутатор 9, регистр 6 (7) по стробу на входе 16.1 (16.2) группы 16 входов устройства, коммутатор 10 и записываются в счетчики 38 и 37 в момент подачи синхросигнала на вход 17 и кода 111 на группу 13.2 входов устройства).

Загрузка регистров блоков 1 и 2 операндами будет описана отдельно,

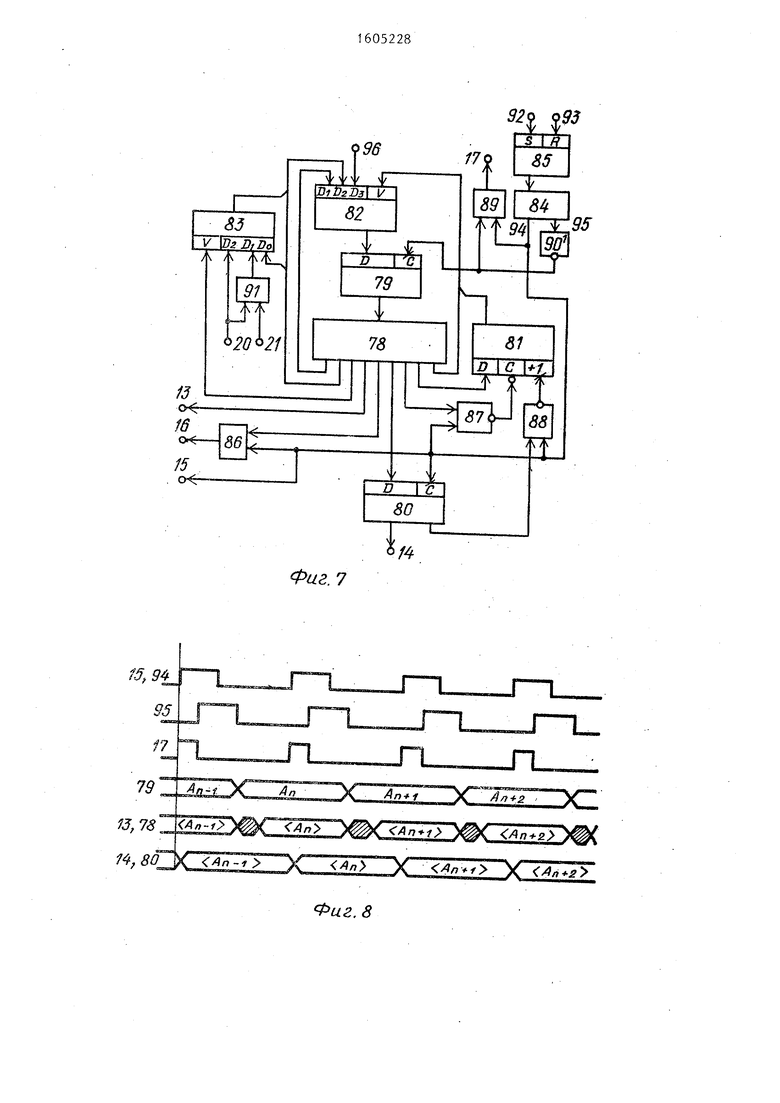

При пояснений алгоритма выполнения деления подразумевается изве Лтным (оговаривалось ранее) что лрн делеихи полуслов срабатывает только блок 1 (на 14.2.1 и 14. л,5 микрооперации отсутствуют), а при делении слов срабатывают и блок 1, и блок 2 (на вход 14.2,5 поступает Mtncp о операция ПС) . Поэтому на фигс9 представлен единьш алгоритм как для деления полуслов так и слов а ьякрооперация 14.2,5 в операторах зтого алгоритма не показана. Кроме Toroj разные алгоритмы представляются отдельньоо ветвями, имеющими бук- венну1о инг4ексацию возле номеров соответствующих операторов, и будут поясняться дополнительно.

В аервой микрокоманде (см. алгоритм на фиг.9) 1ТПОИЗВОДИТСЯ перепись делителя из регистра с номером R2 в

0522820

регистр с нулевым номером, используемым в качестве рабочего регистра. Регистр УРо адресуется нулевым кодом,

, несмотря на ненулевое содержимое,

, счетчиков 37 и 38, путем блокировки передачи содержимого этих регистров через элементы И 48 (фиг,3)„

Кроме того, в первой микрокоманде

0 знак делителя заносится в триггер 57, в котором хранится до окончания процедуры деления при получении очередных нрфр частного.

Во второй микрокоманде в счетчик

15 81 загружается константой К, определяющее число шагов получения цифр частного (для полуслов и слов К имеют различные значения.и определяются их разрядностью). Поскольку в каждом

20 цикле выполнения команды деления лучается значение очередной цифры частного и определяется операция (сложение или вычитание) над остатком и делителем в следующем цикле деле25 ния, то с целью сокращения (на один цикл) времени выпапнения команды деления во второй микрокоманде делимое передаётся в сумматор блока 1 (2), а его знак запоминается в триггере 58„

30 Это позводяет, при выполнении оператора 3 со знаковьц разрядом оперировать также как и с разрядами значащей части делимого (остатка), что упрощает реализацию деления, однако приводит к получению инверсного значения истинного зна;са результата при записи iiepBoro. бита в младший разряд вспомогательного регистра блока 1 (2) при первом.исполнении микрокоманды

Q третьего оператора и. получению истинного значения микроопераций 1 и Ср, обеспечивающих правильное срабатывание оператора 3 для подготовки операции при очередном (втором) выполне.. НИИ оператора 3, 4э

при каждом очеред ном разе вьшолнения оператора 3 на выходе элемента 59 сравнения формируется очередная 1щфра частного предьщущего цикла вы- числений, поступающая в мпадший разряд вспомогательного регистра. Совмещение выпапнения очередной операции (сложение, вычитание), зависящей от полученного результата в предьщу- щем цикле деления и зднесения значе- 55 ния очеремно.й цифры частного во вспомогательный регистр блока 1 и 2, / обеспечивает триггер 58, обеспечиваю- 1Щ1Й -задержку на один т-щкл значения

35

знака результ-ата операоди над остатком и делителем.

Кроме того, следует отметить, что при выполнении оператора в первый раз в младший разряд вспомогательного регистра заносится инверсное значение истинного знака результата; во второй раз - значение знака результата, истинное при корректных кодах делимого и делителя, не дающих переполнения разрядной сетки при делении и инверсное при операндах, приводящих к переполнению разрядной сетки, в третий и т.д. разы - значения первой и т.д. значащих цифр результата деления.

16

20

Микрокоманды третьего оператора алгоритма (фиг.9) вьшолняются следующим образом. На место делимого (регистр с номером R1) заносится сдвинутьй на один разряд влево результат сложения или вычитания (определяется сигналом на выходе 22 оче- 25 редной цифры частного блока 4) делимого или очередного остатка и делителя. В мпадший разряд результата при этом заносится нулевая цифра,

.Поскольку алгоритм и реализащш депения чисел построены так, что вспомогательном регистре хранятся числа: истинный (инверсное значени и полученный при делении (инверсно значение при переполнении), то вел чина К выбирается такой, что после выполнения, оператора 3 в старшем разряде вспомогательного регистра хранится первое (инверсное) значен знака результата, а сам результат требует вычисления еще мпадшего ра ряда результата деления. Позтому о ратор 4 (4а и 46) вьтаттняетс аналогично оператору 3, что опр деляет значение мпадшего разряда частного. При этом отличие четверто оператора от третьего состоит в том что счетчик 81 не работает, и при в полнении четвертого оператора из вспомогательного регистра вьдвигает инверсное значение знака результата которое, инвертируясь на инверторе (см. фиг.5), заносится в триггер 57 через информационный вход 2 мультиплексора 56, и в младши-й разряд

гак как вход А, коммутатора 8 - -падши-й разряд

и первый вход группы элементов И 11 ° - °--ьного регистра заносится

и первый вход группы элементов И 11 подключены к шине нулевого потенциала. Содержимое вспомогательного регистра также сдвигается на один разряд влево, причем в его мпадший разряд заносится значение очередной цифры частного (вход А коммутатора 8 сдвигов и группы 11 элементов И под- кпючены к выходу 22 блока 4), Микрооперации 1.0- 001 соответствуют работе с регистрами, адресуемыми полями А (0...0) и В (R1); ткроопе- 1. С И соответствует нулевому значению полученной очередной цифры частного (состояния выхода 22 блока 4 проверяется микрооперацией ПД на входе 14.2.7 блока 5) и соответствует сложению делимого (очередного остатка) и делителя, а Ig. 00 tl, С„ равно 1 соответствует единице полученной очередной цифре частного и соответствует вычитанию делителя из делимого (очередного остатка). Кроме того, в третьем операторе содержимое счетчи,-г-| ОЧ

-г, v..,j.ya I ир.с 1-.имержимое счетчика 81 увеличивается на единицу и про- вернется его переполнением. При отсутствии переполнения выполнение оператора 3 повторяется, при переползначенне цифры мпадшего разряда результата.

Отличие оператора 4а от 46 за 2 ключается в том, что оператор 4а является ветвью алгоритмов при отсут ствии округления (от оператора 4а осуществляется переход к оператору 5а), при округлении путем принуди- 40 тельной записи единицы в отадший раз ряд результата (при делении полуслов за оператором 4а следует оператор

56 , а при делении слов за оператором 4а следует оператор 5в) . Опе 45-Ратор 4б является ветвью алгоритма при округлении по значению сверхмладшей цифры частного, при этом значение сверхмладшей цифры частного равно инверсии суммы по модулю два сигналов 5Q на выходах 20 и 21 блока 4, поэтому при проверке соответствующего логического условия (сигнала на выходе элемента 91 сравнения) переход к оператору 5а соответствует отсутствию округления, а к оператору 5г - округлению путем прибавления единицы

--i- . . лC/J, Л ЛЛ Цэ

младшего разряда (например, единицы входного переноса 14,2,6 С .1) к полученному результату.

10

20

25

60522822

нении счетчика 81 происходит переход к четвертому оператору.

.Поскольку алгоритм и реализащш депения чисел построены так, что во вспомогательном регистре хранятся два числа: истинный (инверсное значение) и полученный при делении (инверсное значение при переполнении), то величина К выбирается такой, что после выполнения, оператора 3 в старшем разряде вспомогательного регистра хранится первое (инверсное) значение знака результата, а сам результат требует вычисления еще мпадшего разряда результата деления. Позтому оператор 4 (4а и 46) вьтаттняется аналогично оператору 3, что определяет значение мпадшего разряда частного. При этом отличие четвертого оператора от третьего состоит в том, что счетчик 81 не работает, и при выполнении четвертого оператора из вспомогательного регистра вьдвигается инверсное значение знака результата, которое, инвертируясь на инверторе 61 (см. фиг.5), заносится в триггер 57 через информационный вход 2 мультиплексора 56, и в младши-й разряд

15

- -падши-й разряд

° - °--ьного регистра заносится

° - °--ьного регистра заносится

значенне цифры мпадшего разряда результата.

Отличие оператора 4а от 46 за- 2 ключается в том, что оператор 4а является ветвью алгоритмов при отсутствии округления (от оператора 4а осуществляется переход к оператору 5а), при округлении путем принуди- 0 тельной записи единицы в отадший раз- ряд результата (при делении полуслов за оператором 4а следует оператор

56 , а при делении слов за оператором 4а следует оператор 5в) . Опе- 5-Ратор 4б является ветвью алгоритма при округлении по значению сверхмладшей цифры частного, при этом значение сверхмладшей цифры частного равно инверсии суммы по модулю два сигналов Q на выходах 20 и 21 блока 4, поэтому при проверке соответствующего логического условия (сигнала на выходе элемента 91 сравнения) переход к оператору 5а соответствует отсутствию округления, а к оператору 5г - округлению путем прибавления единицы

--i- . . лC/J, Л ЛЛ Цэ

младшего разряда (например, единицы входного переноса 14,2,6 С .1) к полученному результату.

Таким (1бг)азом, в операторе 5а гроизподится перепись частного из вспомогате.пьного регистра PQ в ре- гггстр с номером Rl, причем осуществ- пяется анализ результата на переполнение, которое определяется тем, что знак пол -ченного .результата не равен истинному знаку результата, хранимому в триггере 57, т.е. переполнению соответствует единица на выходе элемента 91 сравнения..

В операторе 56 анализ переполне осу1иеств.аяется аналогично Оператору 5а, а формирование единичног значения младшей части результата деления (частного) производится путем подачи через группу 13.1 входов устройства, коммутатор 9, регистр 6 (7) и коммутатор 10 па информационный вход блока 1 кода с единицей в младшем разряде и нуляш в остальных разрядах, а в самом блоке 1 - проведе- HiiH операгщи поразрядного логического сложе 1ия над .содержимым вспомога- тельного регистра и кода на информационном входе D блока 1 и.занесе- ПИЯ результата в регистр с номером- R1 (I. 110, Ir 5 011 и Ч-с. 011).

Оператор .зв вьтолняется аналогично оператору 5а, Отличие операторов За от 5в состоит в том, чт в операторе 5а при обработке слов перепись результата гфоисходит в бло 1 и блок 2, т.е. на вход 14.2.5 блока 5 поступает сигнал микрооперацией ПС, а при обработке полуслов в one- раторе 5а срабатывает только блок (нет E Пф о операции ПС) . В операторе 5в несмотря на то, что он пред- сташшет ветвь алгоритма деления слов микрооперащ- я ПС не вырабатывается и старшее полуслово результата из регистра PQ переписывается в регистр с номером R1 блока 1 без изменения.

Поскольку младшая часть результата nps делении слов аходится в блоке 2, то формирование в младшем разряде результата осуществляется в операторе 6 аналогично опера- тору 56. Отличие состоит лишь в том, что в шестом операторе в устройство поступает микрооперация ППС по входу Ki.Z.I (см. фиг.6), обеспечивающая срабатыва}ме только блока 2, и отсутствует анализ на переполнение резульг ата (такой анализ проводится в операторе

5в) .

В операторе 5г производится округл еште результата прибавления единицы младшего разряда к результату, полученному в регистре PQ, и получе 1ный результат помеп1;ается в регистр блока 1 (2) с номером R1, При этом анализ на,нереполнение разрядной сетки состоит как проверкой равенства истинного знака полученному (аналогично вьшгеописанному анализу сигнала на выходе элемента 91 сравнения), так и проверкой состояний сигнала OVR в блоке 1. Недостаточность проверки только сигнала OVR заключается в том, что при неверно полученном знаке результата и его округлении переполнение неверно полученного числа может отсутствовать, а недостаточность проверки только на равенство истинного (содержимое триггера 57) и палученного знака результата (сигнал на выходе Р„ блока 1) элементом 91 сравнения заключается в том, что после округления неверно полученного частного его знак может совпасть с истинньм знаком, а наличи переполнения обнаруживается сигналом OVR.

На алгоритмах, представленных на фиг.9 и 10, не показаны ветви анализа и перехода по переполнению. Для данного анализа в ШУУ (фиг.7) коммутатор 83 логических условий должен быть допатнен еще одним логическим условием, равным логическому сложению (функция ШИ), для сигналов с выхода элемента 91 сравнения и с выхода OVR в блок 1„-

При делении слов запись в регистр R1 указанных кодов осуществляется за две аналогичных посыпки: сперва заносится код 10...О (01... 1) в блок 1, а затем код О,..о (1...1) в блоке 2, При записи кодов в блок 2 в устройство подается микрооперация ППС по входу 14.2.1 в блок 5.

На фиг.10 приведен алгоритм деления слов с палучением результата удвоенной разрядности. Размещение результата осуществляется в двух смежных регистрах: старшая часть в регистре блока 1 с номером 1, а младшая часть с номером на единицу большим (фиг.10 имеет обозначения (R1 + 1)).

Поскольку получение очередных цифр частного после получения полноформатного частного заключается в продолжении операций над остатком и делите

лем, a вспомогательный регистр блока 1 (2) должен быть освобожден от частного (путем перезаписи его в регистр R1 блока 1 (2) для получеьшя мпадшей части частного удвоенной разрядности то депимое- из регистра R1 копируется в регистре (R1 + 1).

Таким образом, в первом операторе (фиг.10) делитель из регистра R2 jперегружается в регистр YP,, а знак {делителя запоминается в триггере 57 (фиг.9).

Во время вьтолнения второго оператора счетчик 81 загружается констан- |Той К, определяющей число повторений Оператора 4,. содержимое регистра R1 перегружается во вспомогательный регистр PQ, после чего содержимое счетчика 38 увеличивается на единиду для адресации регистра (R1 +1).

Во время выполнения третьего оператора копия делимого из регистра PQ перегруясается в регистр (R1 + 1), а знак делимого заносится в триггер 58 для определения операции (сложения или вычитания над делимым и делителем при первом выполнении оператора 4.

Повторяя вьшесказапное, следует напомнить, что PQ обозначает вспомогательный регистр в блоке 1 (2), R1 и (R1 -f 1) указывают регистры блока 1 (2), адресуемые полем В (выход коммутатора 40 адреса), а R2 - регистры блока 1 (2), адресуемые полем А (выход коммутатора 39 адреса в блоке 3).

Вьшолнение оператора 4 на фиг.10 идентично выполнению оператора 3 на фиг.9, отличие состоит лишь в том, что вместо регистра R1 адресуется регистр (R1 + 1).

Выполнение оператора 5 VHa фиг. 1.0 осуществляется, аналогично вьшолнению

В операторе 8 восстанавливается значение триггера 58, полученное после оператора 5, Для этого на ... группу 13,1 входов подается код с н лем в старшем разряде. Этот код через коммутатор 9 регистра 6 (7) и коммутатор 10 подается на информационный вход ОБ1. Коды 12-0 1П, 1. и обеспечиваю передачу этого кода через блок 1 без

оператора 4б на фиг.9 с тем отличи- изменения содержимого его регистра.

ем, что вместо регистра R1 в операции участвует регистр- (R1 -ь 1), вместо логического условия значе ше выхода элемента 91 сравнения проверяется логическое условие знак результата (т.е. значение выхода 20 блока 4 или F блока 1) на коммутаторе 83 логических условий. Кроме тоги, по окон- чагши пятого оператора содержимое 38 уменьшается на единицу для адресации регистра R1 при запо- - минании старшей части частного.

Ветвление алгоритма по операторам 6-8 или 9-11 обеспечивает запо50

55

Таким образом нулевое значение знакового разряда результата (F« О) будет записано в триггер 58, и устройство готово к продолжению операци деления.

Операторы 9 и 10 идентичны оп раторам 6 и 7 соответственно, а оператор 11 отличается от оператора 8 только значением кода на груп пе 13,1 входов устройства (единичное значение старшего разряда этого кода обеспечивает установку триггера 58 в единицу вместо нуля как в операторе 8),

10

5

0

5

О

5

минание предыстории деления л.ля правильного получения очередной (первой - старшего разряда - мпадшей части результата деления). Это позволяет в начале вьтолнения оператора 12 иметь такое же состояние триггера 58, какое было получено по окончании оператора 5 (определяющее значение очередной ияфры частного и операцию в операторе 12).

Вьшолнение оператора 6 состоит в запоминании частного (старшей части) в регистре Р1 и проверки результата на переполнение. Единичное состояние выхода элемента 91 сравнения соответствует переполнению результата, поэтому продолжение деления теряет смысл (реакция на переполнение может осуществляться аналогично вышеописанному) . При отсутствии переполнения за оператором 6 следует оператор 7, в котором в триггере 57 восстанавливается значение знака делителя, находящегося в регистре с нулевым номером (Уро)J в счетчике 81 записывается код К, определяющий число повторений оператора содержимое счетчика 38 увеличивается на единицу для адресации регистра (R1 + 1), в котором находится остаток и куда будет произведена запись младшей .части результата деления.

I

В операторе 8 восстанавливается значение триггера 58, полученное после оператора 5, Для этого на ... группу 13,1 входов подается код с нулем в старшем разряде. Этот код через коммутатор 9 регистра 6 (7) и коммутатор 10 подается на информационный вход ОБ1. Коды 12-0 1П, 1. и обеспечивают передачу этого кода через блок 1 без

изменения содержимого его регистра.

0

5

Таким образом нулевое значение знакового разряда результата (F« О) будет записано в триггер 58, и устройство готово к продолжению операции деления.

Операторы 9 и 10 идентичны операторам 6 и 7 соответственно, а оператор 11 отличается от оператора 8 только значением кода на группе 13,1 входов устройства (единичное значение старшего разряда этого кода обеспечивает установку триггера 58 в единицу вместо нуля как в операторе 8),

35

1 в счетчике 37 (38) и в блок 2 при Q2 О в счетчике 37 (38).

Перегрузка полуслов из одного регистра блока 1 (2) в другой производится за два- цикла. В одном цикле содержимое соответствующего регистра блока 1 (2) передается с выхода Y (2) (сигнал ОЕ поступает только в активированный блок 1 (2)) через коммутатор 9 в регистр 6 (7). Во втором цикле полуслова с регистра 6 (7) через коммутатор 10 информация поступает к; ннформаиионный вхсщ D блока 2 (1) и записывается в соответствую45

50

55

1605228

Оператор 12 ня фиг.10 выполняет- апалогичио описанному выше операто- 3 на фиг.9.

Р операторе 13 производится запись младшей части частного из регист- ра PQ в регистр (R14-1), после чего- содержимое счетчика 38 уменьшается на единицу цля адресации регистра R1.

Е операторе 14 значение знака ю частного из старшего разряда регистра F.1 переписывается в триггер 57, после чего выполнение команды деления с поучением удвоенной разрядности результата (частного) заканчивается, 15

Опишем работу устройства в режимах загрузки (выгрузки) информации в (из) блок 1 (2).

Соединение выходов счетчиков 37 и 38 с коммутаторами 39 и 40 адресов и 20 злом 41 активации операционных бло- ков, управляемых группами входов 14.3.2 и 14.3.4 обеспечивает при работе с полуслова размещать их в памяти блока 1 (2) без потерь объема 25 этой памяти. При адресации полуслов на группы 14.3.2 и 14.3.4. БАЗ подаются коды 10 или 11 (Фиг, 2, Зи4), которые обеспечивают переадресацию кодов для полуслов (двум адресам со- 30 ответствует один и тот же регистр, а также выработку блокируюищх сигналов на выходе 25 блока 3, которые определяются состоянием сигналов на выходах Ог. счетчиков 37 и 38 и обеспечивают активацию соответствующего блока 1 (2) ,

Таким образом, при загрузке полу-, слов в блок 1 (2) информация в устройство . поступает по группам входов 40 12 или 13,1, передается через коммутатор 9, регистр 6 (7) и коммутатор 10 на информационные входы D блоков 1 и 2 и записывается в блок 1 при 0

о ги ви п гр и ил пр ми и ка ми

за ни ко ре их му бл пр ва во че вы ро ны ус ан

ро ус ли со ва

7 вы

ни гу ва Та ла ве то на эт

8 са ва бл гер си

28

5

5

0

5

ю 5

0 5 0

0

щий регистр активированного блока 1 (2), .

Загрузка слов в блок 1 и блок 2 осуществляется за два цикла аналогично описанной загрузке полуслов, Разница при загрузке каждой из половин слова в блок 1 (2) от загрузки |полуслова состоит в том, что коды на группах управляющих входов 14,3.2 и 14,3,4 в блок 3 были равны 00 или 01, при этом активация блока 1, производится отсутствием сигналов микроопераций ПС и ППС (входы 14.2,5 и 14.2,1 в блок 5), а активация блока 2 - наличием микроопераций ППС (вход 14,2,1 в блок 5) и отсутствием микрооперации ПС (вход 14,2,5).,

При взаимодействии устройства с запоминающими устройствами может возникнуть необходимость выдачи в них кодов адресов. При хранении кодов адресов (полуслов) в блок 1 (2) выдача их производится аналогично описанному выше режиму переписи полуслов из блока 1 (2) в блок 2 (1). При этом примем, например, выход 18 устройства для выдачи адреса, тогда полуслово (адрес) из блока 1 (2) передается через коммутатор 9 в регистр 6. При выдаче (внешним) запоминающим устройством информации в ответ на выданный адрес она поступает на вход 12 устройства и передается в блок 1 (2) аналогично описанному.

Выдача информации из данного устройства, например, в запоминающее устройство от приема информации отличается тем, что после записи адресов в регистр 6 (выход 18 устройства) информация записывается в регистр

7аналогичным образом и выдается на выход 19 устройства.

Поскольку в устройстве могут храниться коды адресов, то над ними могут производиться операции преобразования, например вычитания-сложения. Так как коды адресов не являются числами со знаковым разрядом и соответственно фиксированной перед ним запятой, то фиксация знака результата операций над кодами или фиксация переполнения этих кодов как чисел не имеет смысла.

8зтом случае- случае имеет смысл фиксация переноса (например, для суммирования с учетом переноса), Позтому в блоке 4 предусмотрена запись в триг- гер 57 сигнала переноса. Поскольку сигнал переноса должен фиксироваться

29

только для активированного блока 1 или блока 2, то в блоке 4 осуществляется выбор сигнала переноса Су только активированного операционного блока с помощью элемента И-ИЛИ 60, управляемого сигналами с выходов элементов И-ИЛИ-НЕ 54 и 55.

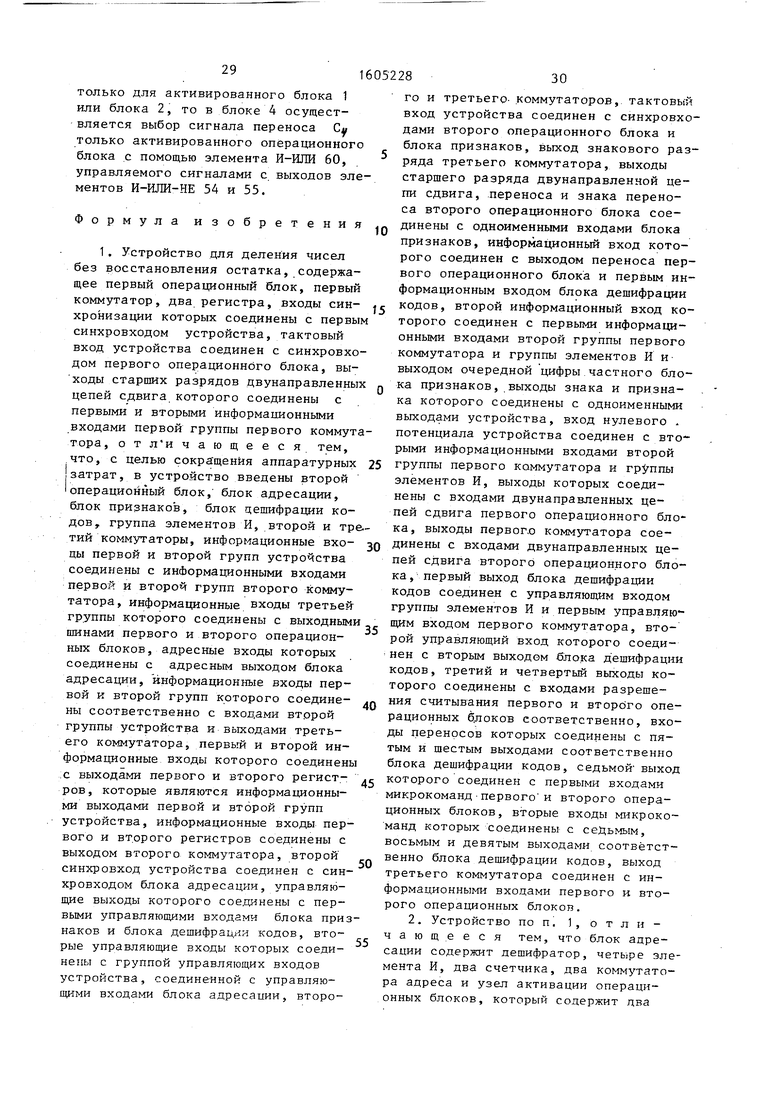

Формула изобретени

160

1. Устройство для деления чисел без восстановления остатка, содержащее первый операционный блок, первый коммутатор, два регистра, входы синхронизации которых соединены с первы синхровходом устройства, тактовый вход устройства соединен с синхровходом первого операционного блока, вы- ходы старших разрядов двунаправленны цепей сдвига которого соединены с первыми и вторыми информационными входами первой группы первого коммуттора, о т л и чающееся тем, что. с целью сокращения аппаратурных

затрат, в устройство введены второй I операционный блок, блок адресации, блок признаков, блок дешифрации кодов, группа элементов И, второй и третий коммутаторы, информационные вхо- ды первой и второй групп устройства соединены с информационными входами перволч и второй групп второго коммутатора, информационные входы третьей группы которого соединены с выходными шинами первого и второго операционных блоков, адресные входы которых соединены с адресным выходом блока адресации, информационные входы первой и второй групп которого соединены соответственно с входами второй группы устройства и выходами третьего коммутатора, первый и второй информационные входы которого соединены :с выходами первого и второго регистров, которые являются информационными выходами первой и второй групп устройства, информационные входы первого и второго регистров соединены с выходом второго коммутатора, второй синхровход устройства соединен с син- хровходом блока адресации, управляющие выходы которого сое,цинены с первыми управляющими входами блока признаков и блока дешифрад; и кодов, вторые управляющие входы которых соединены с группой управляющих входов устройства, соединенной с управляющими входами блока адресации, второ

5

1605228

30

о е15

мх а

25

35

40

е3045

55

го и третьего- коммутаторов, тактовы н вход устройства соединен с синхровхо- дами второго операционного блока и блока признаков, выход знакового разряда третьего коммутатора, выходы старшего разряда двунаправленной цепи сдвига, переноса и знака переноса второго операционного блока сое- Q динены с одноименными входами блока признаков, информационный вход которого соединен с выходом переноса первого операционного блока и первым информационным входом блока дешифрации кодов, второй информационный вход которого соединен с первыми информационными входами BTopofr группы первого коммутатора и группы элементов И и- выходом очередной цифры частного блока признаков, выходы знака и признака которого соединены с одноименными выходами устройства, вход нулевого . потенциала устройства соединен с вторыми информационными входами второй группы первого коммутатора и группы элементов И, выходы которых соединены с входами двунаправленных цепей сдвига первого операционного блока, выходы первого коммутатора соединены с входами двунаправленных цепей сдвига второго операционного блока, первый выход блока дешифрации кодов соединен с управляющим входом группы элементов И и первым управляющим входом первого коммутатора, второй управляющий вход которого соеди- нен с вторым выходом блока дешифрации кодов, третий и четвертый выходы которого соединены с входами разрешения считывания первого и вторбго операционных блоков соответственно, входы цереносов которых соединены с пятым и шестым выходами соответственно блока дешифрации кодов, седьмой- выход которого соединен с первыми входами микрокоманд-первого и второго операционных блоков, вторые входы микрокоманд которых соединены с седьмым, восьмым и девятым выходами соответственно блока дешифрации кодов, выход третьего коммутатора соединен с информационными входами первого и второго операционных блоков.

2. Устройство по п. , отличающееся тем, что блок адресации содержит дешифратор, четыре элемента И, два счетчика, два коммутатора адреса и узел активации операционных блоков, который содержит два

цсшифраторт, двл элемента И-ИК и дв-| -г(-мрнта 2P -2HJ H-iiE, причем поргшй ингЬ(п мл Шо11ный вход бдока соединен с пиформлционным входом дешифратора, синхровход которого соединен с синхр нходом бдока, с первого по четвертый ин11орсные выходы дешифратора соединены с первьми входами с первого по четвертый соответственно эдементов И пятый инверсный выход дешифратора соединен с вторыми входами первого и третьего эдементов И, выходы которых соединены с счетными входами первого и второго счетчиков соответственно, шестой инверсный выход дешифратора соединен с вторыми входами второго и четвертого эдементов И, выходрл которых соединены с вычитающими входами первого и второго счетчиков соответственно, седьмой инверсный выход дешифратора соединен с инверсными син- хровходами первого и второго счетчиков, информадионные входы которых соединены с вторым информационным входом бдока, выходы первого счетчика соединены с первыми информационными входами первого и второго коммутаторов адреса, вторые информационные входы которьгх: соединены с выходами разрядов второго счетчика, выход третьего разряда второго счетчика соединен с первыми входами первого и второго элементов 2И-2ИЛИ-НЕ, вторые входы которых соединены с выходом третьего разряда первого счетчика, yпpaвляюш й вход блока соединен соответствующими разрядами с управляющими входами первого и второго коммутаторов адреса и первого и второго дешифраторов узла активации опера- дионных блоков, первые инверсные выходы которых соединены с первыми входами первого и второго эдементов И-НЕ соответственно, вторые входы которых соединены с вторыми инверсными выходами второго и первого дешифраторов узда активации операционных

Г) f )

32

бдоков соответственно, выход первого элемента И-НЕ соединен с третьими входами .первого и второго элементов 2И-2ИЛИ-НЕ, четвертый входы которых соединены с выходом второго элемента И-НЕ, выходы коммутаторов адреса соединены с адресным выходом блока, управдяющий выход которого соединен 0 с выходами элементов 2И-2ИЛИ-НЕ.

3, Устройство по п.1, о т л и - чающееся тем, что блок приз-, наков содержит элемент 2И-2ИЛИ, элемент НЕ, мультиплексор, два триггера 5 и элемент НЕРАВНОЗНАЧНОСТЬ, выход которого соединен с выходом очередной цифры частотного блока, тактовый вход блока соединен с тактовыми входами первого и второго триггеров, инверсный выход первого и прямой выход второго триггеров соединены с первым и вторым входами элемента НЕРАВНОЗНАЧНОСТЬ, информационный вход блока соединен с первым входом элемента 2И- 2ИЛИ, второй и третий входы которого соединены с первым управляющим входом блока, второй управляющий вход которого соединен с управляющим входом мультиплексора, первый информационный 0 вход которого соединен с выходом первого триггера и является выходом знака блока, вход знакового разряда блока соединен с вторым информационным входом мультиплексора, третий инфор- 5 мационный вход которого соединен с выходом элемента НЕ, вход которого соединен с входом старшего разряда двунаправленной цепи сдвига блока, вход переноса которого соединен с 0 четвертым входом элемента 2И-2ИЛИ, .которого соединен с четвертым информационным входом мультиплексора, пятый информационный вход которого соединен с входом знака переноса 5 блока, информационным входом второго триггера и выходом признака блока, выход мультиплексора соединен с информационным входом первого триггера.

0

5

/7

85

/

D с

80

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

Изобретение относится к вычислительной технике и может найти применение в арифметических устройствах процессоров быстродействующих ЦВМ. Цель изобретения - сокращение аппаратурных затрат. Устройство позволяет реализовать различные дисциплины округления результата деления, получить результат деления удвоенной разрядности и делить числа различного формата без потери производительности устройства и снижения коэффициента использования оборудования устройства. Устройство для деления чисел без восстановления остатка содержит операционные блоки 1, 2, блок 3 адресации, блок 4 признаков, блок 5 дешифрации кодов, регистры 6, 7, коммутаторы 8 - 10 и группу элементов И 11. 2 з.п. ф-лы, 10 ил.

Фаг. 7

f OCZdF-o

п X ,

. 8

/4

Rl--L HT ± ypo l-Z PQ: / 5 2 ;/ flo 5S /.2.7i 757: POy;

.oor Js uocoj;

%e ,JJO, Cp ,,

i 58

I 5g

P07oej

3 7

I

Kr. PQyv

V 73.77;

r

У

57 ®

при 9J..r

( Конец

С

PQ - PQy-2 PQo- 59; .2.7; ZrQ..OOn,:is 3.00L03 l %6,,7W,-

91-r

Я7.- Я57; V /Oa /

( /rg7//f /

;4 .2.5.7

5;,,; ;

/. 75;

s5

С 3

1

Тч1м):

PQfli 59; П.2Л ; Cfj, f}

.oo. J;..3 -4QOffl/rД,,, ..Ш.

gb- ,

J/7// CJ

L

:x

L

f г } PO- PO,y 2 ;PQo- S9; J4-Z7;Tf7: PSj; СГд,,,)

,go/r 7j,3 gofgj;7g.g ,ffly; b va7

Signff- / 7.e. g-,

«нО

..

fnpu Д/

f

ff;: f 57

57

r

( -Q/ygf О

Hi

(Я1 ) яэ; ; ffo. .2.7 i Г

:72rO 7,OT ; 7jj,-.

f I пег 81

HfeZE

Л/-7 frg.

(

У/ о

Z

сгеГ -к;

PQ

СТзв Г

(я, l) Stjf /( ч. Г5в; Г .

ff;: f 57 - ;

57-

r

О

iPT

bign yfby- Tff; ьтаг A f w r;

7T

Ji

/5.7

,d,

;j

f гзв-

Sijrt Я1

r

ir

(КОНЩ

| Устройство для деления чисел безВОССТАНОВлЕНия OCTATKA | 1979 |

|

SU817706A1 |

| Хвощ С.Т./Варлинский Н.Н | |||

| и Попов Е.А | |||

| Микропроцессоры и микро- ЭВМ в системах автоматического уп- ранпеиия | |||

| -Л., 1987, с | |||

| Ветроэлектрическая силовая установка | 1921 |

|

SU378A1 |

| рис | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-11-07—Публикация

1989-01-10—Подача