сл

00

СХ)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для микропрограммного управления | 1983 |

|

SU1188742A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Микропрограммное устройство управления и отладки микропрограмм процессора | 1984 |

|

SU1168937A1 |

| Устройство для отладки вычислительной системы | 1986 |

|

SU1336015A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1495789A1 |

| Устройство для контроля тестопригодных программ | 1990 |

|

SU1751767A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1633402A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке и отладке устройств с микропрограммным управлением. Цель изобретения - повышение быстродействия при отладке программ. Устройство содержит блок 1 задания -режима, коммутаторы 2,8 и 27, счетчик Bj блок 4 постоянной памяти, регистр 5 микрокоманд, блок 6 сравнения, де

л W

ишфрлторы 7 и 32, элементы И 9,10,

16,17,18,19,20,21 и 22, элементы |ИЛИ 11,23,24,25 и 26, элемент 12 за- держки, сумматор 13 по модулю два. триггеры 14,15,30 и 31, блоки 28 и 29 памяти. За счет вновь введенных блоков изобретение обеспечивает возможность

1

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке и отладке устройств с микропрограммным управле- ijiHeM.

Цель изобретения- повьшение быстро- |ействия при отладке программ

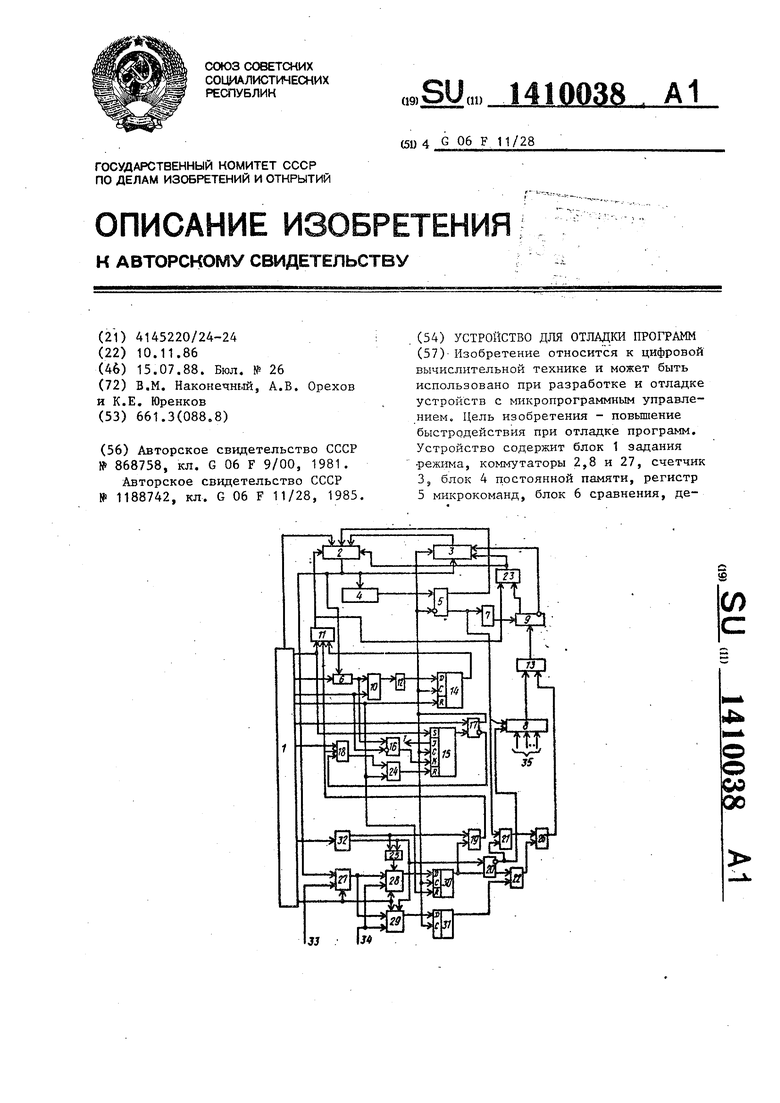

На чертеже представлена функцио- 1 альная схема устройства.

Устройство содерзкит блок 1 задания режимов, первый коммутатор 2 адреса, счетчик 3 адреса, блок 4 постоянной памяти, регистр 5 микрокоманд, блок 6 сравнения, дешифратор 7 признака ус- л овного перехода, коммутатор 8 усло- в}ий, первый и второй элементы И 9j,10, первый элемент ИЛИ 11, элемент 12 задержки, сумматор 13 по модулю два, триггер 14 цикла отладки, триггер 15 блокировки синхронизации, элементы И 16-22, элементы ИЛИ 23-265 второй кэммутатор 27 адреса, первый и второй блоки 28 и 29 памяти, первьй и второй триггеры 30 и 31 управления дешифра- тЬр 32 режима работы, адресный 33, и |1формационньш 34 входы, вход 35 задания условий устройства.

Устройство функционирует в одном и дйух режимов (режим 1 и 2), каждый из которых имеет свой цикл предварительной настройки, включающий фиксацию начального и конечного адресов, кода рфжима в блоке задания режимов, за- пйсь в соответствующие блоки памяти меток по адресам остановов и зацикливания (в блок 28 памяти в режиме 1) ш (и меток по адресам управляемых переходов с метками управления направле- нием перехода (в блоки 28 и 29 памяти в режиме 2).

управления переходами по командам ветвления независимо от действительного значения сигналов условий на входе устройства, что позволяет отлаживать последовательность участков программы без останова в промежуточных точках. 1 ил.

Циклы предварительной настройки задаются нулевым значением управляющего сигнала отладки блока задания режи нов, а рабочие циклы - единичным значением этого сигнала,

В режиме 1 при нулевом значении управляющего сигнала отладка блока задания режимов коммутатор 27 адреса переключается на прием информации с адресного входа 33 устройства} блоки 28 и 29 памяти переключаются сигналом отладки в реяшм записи по управляющему входу записи чтения, блок 28 памяти выбирается по сигналу с элемента ИЛИ 25, в результате чего в блоке 28 памяти (емкостью Nxl бит, где N - емкость блока 4 памяти микропрограмм) через информационньй вход 34 устройства производится загрузка информации. Единичное значение загружаемой информации определяет метку адреса изменения хода вьтолнения микропрограммы в рабочем цикле режима 1, После загрузки информации в блок 28 памяти уп- управляющий сигнал отла;1;ки блока задания режимов принимает единичное значение и переключает коммутатор 27 адреса на прием адреса микрокоманды с выхода счетчика 3 адреса через коммутатор 2 адреса. По сигналу начальной установки триггеры цикла отладки 14, блокировки синхронизации 15, управления 30 устанавливаются в нулевое состояние „ Управляющий сигнал пуска блока задания режимов, длительностью одного периода тактовой частоты, поступает на вход элемента ИЛИ 11 и S- вход триггера 15 блокировки синхронизации. С выхода элемента ИЛИ 11 единичный сигнал поступает на управляю- Щ111 вход - 1:)ммутатора 2 адреса, что

обеспечивает прохождение начального адреса микрокоманды с блока 1 задания режимов на вход бл.ока 4 памяти микрокоманд и через элемент ШШ 23 на управляющий вход разрешения записи счетчика 3 адреса, обеспечивая разрешение занесения в счетчик 3 адреса начального адреса микрокоманды с вы- хода коммутатора 2 адреса. Кроме того сигнал пуска устанавливает триггер 15 блокировки синхронизации в единичное состояние и разрешает прохождение сигнала такта блока 1 задания режимов через элемент И 17 на входы синхрони- зации регистра 5 микрокоманд, счетчика 3 адреса, триггера 14 цикла отладки, триггеров 30 и 31 управления,

В устройстве может быть сформировано два типа микрокоманд: переход по счетчику адреса и условный переход, отличающийся признаком условного перехода в коде микрокоманды,MiiKpoKOMaH- да, выбираемая из блока 4 постоянной памяти, фиксируется по заднему фрон ту тактового импульса на регистре 5 Микрокоманд. Код признаков переходов микрокоманды поступает с выхода 2 регистра 5 микрокоманд на вход дешифратора 7 признака условного перехода.

Если выбрана микрокоманда перехода по счетчику адреса, то на выходе дешифратора 7 признака условного перехода формируется нулевой сигнал, определяющий появление единичного сигнала на инверсном выходе элемента И 9, ко- торьй разрешает при поступлении на счетный вход счетчика 3 адреса переднего фронта тактового импульса прибавлять единицу. В следующем микротакте устройство формирует микрокоманду, адрес которой отличается на единицу от адреса текущей микрокоманды. Если в текущей микрокоманде на регистре 5 микрокоманд фиксируется команда условного перехода, то на выходе дешифратора 7 признака условного перехода формируется единичный сигнал, поступающий на вход элемента И 9. Одновременно на первый управляющий вход коммутатора 8 условий поступает из регистра 5 микрокоманд код номера условия. При этом коммутатор 8 условий пропускает на вход с сумматора 13 по модулю два сигнал одного из условий по входу 35, номер которого закодирован в микрокоманде. Кроме того, на вход элемента И 21 с выхода регистра

5

0 5

0

5

0

5

0

5

5 микрокоманд поступает признак управления полярностью перехода, определяющий прямое или инверсное значение управляющего входа 35, при котором возможен переход по адресу, хра- в регистре 5 микрокоманд или по счетчику 3 адреса. Управляющий сигнал кода pejKiiMa работы блока 1 задания режимов на втором выходе дешифратора 32 определяет нулевой сигнал, который через элемент И 20 с инверсного выхода задает единичньо сигнал на вход элемента И 21 .- Управляющий сигнал с прямого выхода элемента И 20 через элемент И 22 определяет нулевой сигнал на втором входе элемента ИЛИ 26. При выдаче нулепого сигнала признака управления полярностью перехода со второго выхода регистра 5 мпчрокоманд на втором входе с т-матора 13 по модулю два установится нз левой сигнал, что определяет прямое значение признака УСЛОВНОГО перехода, соответствующее выходу ком гутатора 8 условий. Управ- ляющт сигнал разрешение счета на счетчик 3 адреса с инверсного выхода первого элемента И 9 принимает значение лог/М, если управляющий сигнал на выбранном входе коммутатора 8 ус-- ловий имеет нулевое значение. Нулевой сигнал с прямого выхода элемента И 9 через элемент lillli 23 при нулевом значении сигнала на первом входе элемента 1ШИ 23 разрешает передачу адреса мкpoкoмaнды через коммутатор 2 адреса со счетчика 3 адреса. Если анализируемое ветвление микропрограммы выполнено, то на вход элемента И 9 поступает единичный сигнал с выхода сумматора 13 по модулю два. Выходной сигнал с прямого выхода элемента И 9 поступает через элемент ИЛИ 23 на управляющий вход коммутатора 2 адреса и пропускает на его выход адрес микрокоманды из регистра 5 микрокоманд. Если на выходе регистра 5 установлен единичньш сигнал признака управления полярностью перехода, то на вход сумматора 13 по модулю два через элементы И 21, I UTM 26 проходит единичньм сигнал. В этом случае выбранньш коммутатором 8 сигнал условия перехода принимает инверсное значение на выходе сумматора 13 по модулю два. В последующих тактах устройство формирует адреса микрокоманд аналогично изло- женному вьш1е. Адрес исполняемой микрокоманды в каждом такте работы уст1 ойства поступает на блок 6 сравнени выхода коммутатора 2 адреса На торой вход блока 6 сравнения посту- ijiaeT конечный адрес микропрограм ш, установленньй на выходе блока 1 зада йия режимов. Когда шкpoпpoгpa мa ;|;остигает адреса, равного конечному, на выходе блока 6 сравнения уставав- :1ивается единичный сигнал, поступаю- 11ЩЙ на вход элемента И 10 и прямой :аход элемента И 16 „ Если сигнал цик- шческого режима блока 1 задания ре-- кимов принимает единичное значение го триггер 14 цикла отладки устанав-- тивается в единичное состояние через элемент 12 задержки по заднему фрон- У о тактового импульса, Сигнап с вьЬю- ца триггера 14 цикла отладки через 5лемент ИЛИ 11 устанавливает устрой-- :тво в исходное состояние аналогично сигналу пуска блока 1 задания режив, зацикливая микропрограмму с начального адреса, В случае задапик ну тевого значения сигнала циклического ; ежима, поступающего на инверсньш зход элемента И 165 единичный сигнал : выхода блока 6 сравнения через эле чент И 16 поступает на триг

гера 15 блокировки синхронизации i-i jio заднему фронту тактового импульса тереключает его в нулевое состояние, игнал с выхода триггера 15 блоки- зевки синхронизации блокирует поступ 1ение тактовых импульсов через эле.-- Мент И 17 на блоки устройства Затем абота устройства может быть повторе :а заданием других значенш 1 начала ; конца микропрограммы, устанавливае Ных в блоке 1 задания режимов„ С вы™ сода коммутатора 2 адреса адрес ник- Ьокоманды поступает через коммутато 27 адреса на вход блока 28 памяти, Единичный сигнал с первого, выхода де .Шифратора 32 режима работы через эле Иент ИЛИ 25 разрешает выборку информации из 28 памяти. Информация Из блока 28 памяти фиксируется по заднему фронту тактового импульса на Триггере 30 управления. При единич-- Ном значении управляющего сигнала останова блока 1 задания режимов и инверсного выхода элемента И 17 сиг-Нал с выхода элемента И 1В устанавливает в нулевое .состояние через эле Мент ИЛИ 24 триггер 15 блокировки синхронизации. Выход триггера 15 блокирует поступление тактовьк импуль- Сов через элемент И 17 на элементы

0

5

0

0

5

0

5

5

0

стройства5 и счетчик 3 адреса фиксирует адрес микрокоманды, по которому в блоке 28 памяти была предваритель- записана единица,

.В режиме 2 в блок 28 памяти записываются метки по тем адресам микрокоманд условных переходов, ветвление в которых определяется или на неотлаженных аппаратных средствах, или при практически не прогнозируемых поступлениях внеш шх сигнгшоЕ: условий на ynpaEHHroirp-ift вход 35 устройства, или когда сигналы условий определяются результатами работы блока обрабО|Тки данных. Перед отладкой очередного участка микропрограммы определяется строго ориентированньш граф переходов в помеченных узловых точках ветвления путем задания наиболее вероятного .или необходимого направления перехолд. Направление переходов в .икрокоман,дах условного ветвления определяется содержимым блока 29 памяти Е соответствии с адресами указанных Е .шкрокоманд блока 28 памяти. По нулевому значению сигнала отладка с выхода блока 1 задания режимов коммутатор 27 адреса пропускает на адресньш вход блоков 28 к 29 памяти адреса микрокоманд с выхода коммутатора 2 адреса, Управляю.щий сигнал кода режима работы блока 1 задания режимов через дешифратор 32 режи.ма работы по второму выходу разрешает выборку информации из блоков 28 и 29 памяти и подготавлива- - ет прохойчдение сигналов через элемент И 20. С выхода блоков 28,29 памяти информация фиксируется по заднему фронту тактового импульса соответственно на триггерах 30.,31 управления Единичный сигна.л на выходе триггера 30 управления, определяющий помеченную гуЕикрокоманду условного перехода, проходит элемент И 20 и нулевьм значением с инверсного выхода блокирует элемент И 21,, не пропуская управляющий сигнал признака управления поляр- ностью перехода со второго выхода регистра 5 микрокоманд. Кроме того, нулевое значение инверсного выхода элемента И 20 по второму управляющему входу коммутатора 8 условий устанавливает на его выходе нулевое значение, Единичньп сигнал с прямого выхода элемента И 20 разрешает прохождение через элемент И 22 выходного сигнала триггера 31 управления. Значение выхода три1М ера 31 управления определя7

ет направление ветвления в помеченных узловых точках микрокоманд условного перехода. Значение нулевого сигнала триггера 31 управления поступает через элементы И 22, ИЛИ 26 на второй вход сумматора 13 по модулю два. По аналогии с режимом 1 нулевой сигнал с выхода сумматора 13 по модулю два вьфабатывает на инверсном выходе элемента И 9 единичное значение сигнала разрешения счета на счетчик 3 адреса. Единичное значение триггера 31 управления определяет выработку управляющего сигнала разрешения записи на счетчик 3 адреса с выхода элемента ИЛИ 23 через элементы И 9, сумматор 13, ИЛИ 26, И 22 и переключаюнщй коммутатор 2 адреса на прием следующего адреса микрокоманды с выхода регистра 5 микрокоманд,.

Формула изобретения

Устройство для отладки программ, содержащее блок задания режимов, пер- :вьй коммутатор адреса, счетчик адре- са, блок постоянной памяти, регистр микрокоманд , блок сравнения, де- пшфратор признака условного перехода, кЬммутатор условий, первый и второй элементы И, первьм элемент ИJШ причем выходы адресов начала и конца программы блока задания режимов соединены соответственно с первым информационным входом коммутатора адреса и первым входом блока сравнения, выход первого коммутатора адреса соединен с информационным входом счетчика адреса, выход блока постоянной памяти соединен с информационным входом регистра микрокоманд, выходы дешифратора признака условного перехода и блока сравнения соединены с первыми входами соответственно первого и второго элементов И, входы задания условий устройства соединены с информационными входами коммутатора условий, о т- личающееся тем, что, с целью повьшения быстродействия при отладке программ, в устройство введены второй коммутатор адреса, дешифратор режима работы, триггер цикла отладки триггер блокировки синхронизации, элемент задержки, сумматор по модулю два, первьй и второй триггеры управления, первый и второй блоки памяти, семь элементов И, четыре элемента ИЛИ, причем выходы пуска, задания цик

1

00388

лического режима, начальной установки-, тактовых импульсов, задания режима останова, задания кода режима работы,

задания режима отладки блока задания режима соединены соответственно с первым входом первого элемента ИЛИ, инверсным входом третьего элемента И, нулевым входом триггера цикла отлад10 ки, первым входом четвертого элемента И, первым входом элемента И, входом депшфратора. режима работы и управляю- пщм входом второго коммутатора адреса, выходы пуска, задания циклического

15 режима, начальной установки и задания режима отладки блока задания режима соединены соответственно с единичным входом триггера блокировки синхронизации, вторым входом второго элемента

20 И, нулевым входом первого триггера управления, с входом признака записи первого блока памяти, выходы начальной установки и установки режима отладки блока задания режима соединены

25 соответственно с первым входом второ- го элемента ИЛИ, с входом признака записи второго блока памяти, выход первого элемента 1-ШИ соединен с первым управляющим входом первого коммутатора

30 адреса и первым входом третьего элемента ИЛИ, выход которого соединен с входом разрешения записи счетчика адреса и вторым управляющим входом первого коммутатора адреса, выход

. счетчика адреса соединен с вторым ин- формационнь1м входом первого коммутатора адреса, выход которого соединен с адресным входом блока постоянной памяти, вторым входом блока сравнения

40 и первым информационным входом второ- , го .коммутатора адреса, первый информационный выход регистра микрокоманд соединен с третьим информационным входом первого коммутатора адреса, выход

45 кода признаков перехода регистра микрокоманд соединен с входом дешифрат о- ра признака условного перехода, первым управляющим входом коммутатора условий и первым входом шестого элемента И,

gQ выход второго элемента Pi через элемент задержки соединен с информационным входом триггера цикла отладки, выход которого соединен с вторьм входом первого элемента ИЛИ, выход блока

eg сравнения соединен с входом третьего элемента И, выход которого соединен с К-входом триггера блокировки синхронизации, выход которого соединен с вторым входом четвертого элемента И,

14

прямой выход которого соединен со счетным входом счетчика адреса, с входом синхронизации триггера цикла Отладки, входом записи регистра микро команд, входами синхронизации первого и второго триггеров управления, ин- i версный выход четвертого элемента И I соединен с вторым входом пятого эле-ч« I мента И, выход которого соединен с вторым входом второго элемента ИЛИ I выход которого соединен с нулевым I входом триггера блокировки синхрони- |зации,1-вход которого соединен с ши- ной единичного потенциала устройства адресный вход устройства соединен с вторым информационным входом второго коммутатора адреса, выход которого соединен с адресными входами первого и второго блоков памяти, информационный вход устройства соединен с информационными входами первого и второго блоков памяти, выходы первого и второго блоков памяти соединены с информационными входами соответственно первого и второго триггеров управления, прямой выход первого триггера управления соединения - с первыми входами седьмого и восьмого элементов И, инверсный выход восьмого элемен- та И соединен -С вторым управляющим входом коммутатора условий и вторым |входом шестого элемента И, первьй

0038 О

выход дешифратора ре.жи:ма работы соединен с первым входом четвертого элемента ИЛИ и вторым входом восьмого

g элемента И, выход которого соединен

с третьими входами пятого элемента И первого элемента ИЛИ, второй выход дешифратора режима работы соединен с вторым входом четвертого элемента

5

0

5

ИЛИ, с вторым входом седьмого элемента И, входом записи второго блока памяти, выход четвертого элемента ИЛИ соединен с входом записи первого блока памяти, прямой выход второго триггера управления соединен с первым входом девятого элемента И, прямой выход седьмого элемента И соединен с вторьм входом девятого элемента И, выход которого соединен с первым вхо- дом пятого элемента ИЛИ, выход шестого элемента И соединен с вторым входом пятого элемента ИЛИ, выход которого соединен с входом первого операнда сумматора по модулю два, выход коммутатора условий соединен с входом второго операнда сумматора по модулю два,

выход которого соединен с вторым входом первого элемента И, прямой и ин- 30 версный выходы которого соединены соответственно с вторым входом третьего элемента 1ШИ и с входом разрешения счетчика адреса.

| Устройство для управления остановом цифровой вычислительной машины | 1979 |

|

SU868758A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1188742A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-15—Публикация

1986-11-10—Подача