(.54) УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1980 |

|

SU1043657A2 |

| Устройство для отладки программ | 1983 |

|

SU1174932A1 |

| Устройство для отладки программ | 1984 |

|

SU1275452A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для отладки программ | 1984 |

|

SU1223236A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для визуального контроля исполнения программ | 1984 |

|

SU1260964A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1587514A1 |

Изобретение относится к вычислительной технике и может быть использовано при отладке программ и при создании специализированных устройств, предназначенных для отладки программ.

Известно устройство для отладки программ, содержащее блок регистра установки, распределитель, блок формирования адреса участка, блок формирования адреса, блок управления, запоминающее устройство без разрушения информации, блок приема и вывода команд, блок подключения постоянного запоминающего устройства, числовые и адресные шины, командную ишну обращения .

Недостатком данного устройства являются небольшие функциональные возможности, так как устройство применяется то.ль ко для отладки програ лм для постоянных запоминающих устройств, а не всего устройства с программами включительно.

Известно также устройство для отладки программ, содержащее блок управления, блок переключения, блок приема и вывода информации, блок . контроля, регистр дешифратора, триггер сбоя, триггер автоматического

переключения , триггеры возврата и логические схемы И, ИЛИ, НЕ 2,

Недостатком устройства является то, что не обеспечивается возможность отладки аппаратной части-устройства. Кроме того, требуется дополнительная программа-отладчик, на хранение которой расходуется часть объема памяти машины, т,е.

10 уменьшается объем памяти для рабочих программ, следовательно, уменьшается .коэффициент использования .оборудования.

Наиболее близким к изобретению

15 по технической сущности является устройство для отладки программ, содержащее клавиатуру набора информации, первый и второй блок сравнения, элемент И 3j.

20

Однако устройство имеет узкие функциональные возможности. Известное устройство позволяет осуществить останов по определенному адресу и

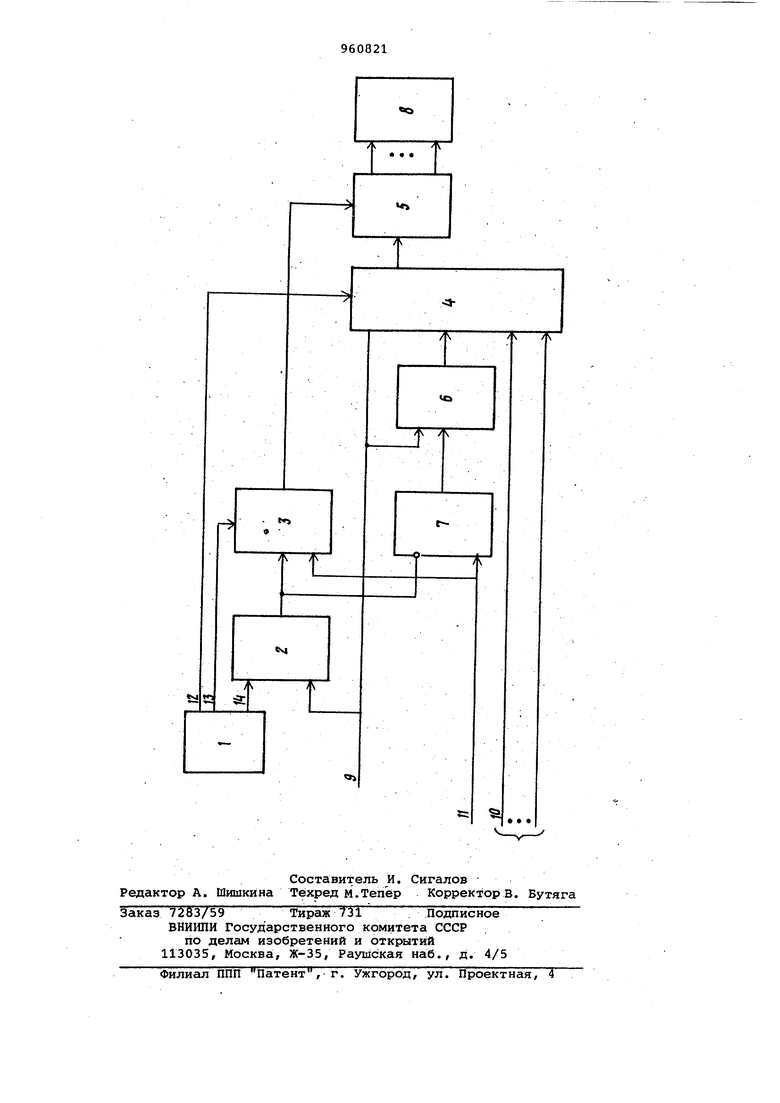

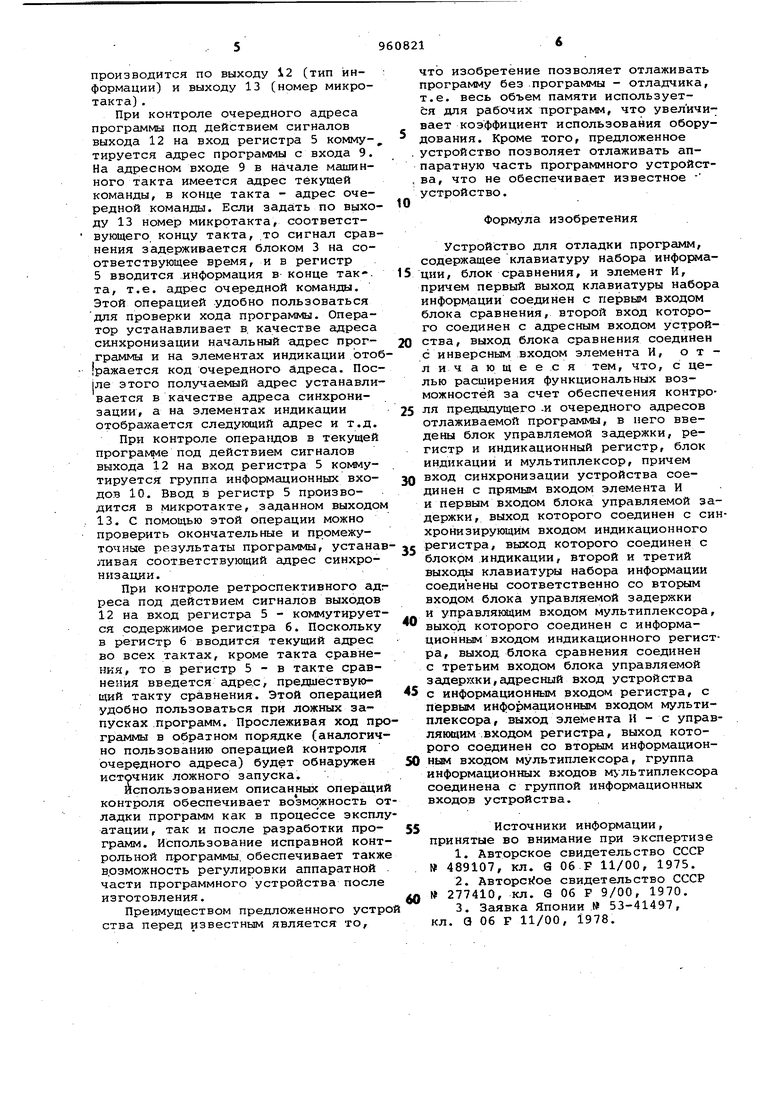

25 Ги по определенному содержимому суьолато|ра.При этом невозможно определить адрес, предшествующий текущему, знание которого необходимо при отладке программы. Знание этого адреса поз30волит определить из какого места -программы был осуществлен переход на команду с текущим адресом. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения контроля предыдущего и очередного адресов отлаживаемой программы, Поставленная цель достигается тем, что в устройство для отладки программ, содержащее клавиатуру набора информации, блок сравнения и элемент И, причем первый выход клавиатуры набора информации соеди|Нен с первым входом блока сравнения, второй вход которого соединен с адресным входом устройства, выход блока сравнения соединен с инверсным входом элемента И, введены блок управляемой задержки, регистр и индикационный регистр, блок инди ации, мультиплексор, причем вход синхронизации устройства соединен с прямым входом элемента И и первым входом блока управляемой задержки, выход которого соединен с синхронизирующим входом индикационного регис ра, выход которого соединен с блоком индикации, второй и третий выходы клавиатуры набора информации соединены соответственно со вторым входом блока управляемой задержки и управляющйм входом мультиплексора, выход которого соединен с информационным входом индикационного регистра, выход блока сравнения соединен с тре тьим входом блока управляемой задерж ки, адресный вход устройства соедине с информационным входом регистра, с первым информационным входом мульт плексора, выход элемента И соединен с управляющим входом регистра, выход которого соединен со вторым инфо мационным входом мультиплексора, гру па информационных входов мультиплекг сора соединена с группой информацион ных входов устройства. На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит клавиатуру 1 набора информации, блок 2 сравнения, блок 3 управляемой задержки, мультиплексор 4, индикационный регистр 5, регистр б, элемент И 7, блок 8 индикации, адресный вход 9 устройства, группы информационных входов 10 муль типдексоров, вход 11 синхронизации, выхсЗды 12-14 клавиатуры набора инфор мащГи, Клавиатура набора информации представляет собой набор тумблеров, посредством которых задаются исходные данные для управления индикацией Посредством выхода 14 задается адрес синхронизации, выходом 13 - величина задержки и выходом 12 тип- индицируемой информации. Блок 2 сравнения предназначен для ;сравнения адреса синхронизации, поступакщего с клавиатуры 1, с текущим адресом программы. Блок 3 управляемой задержки предназначен для задержки сигнала сравнения на заданную клавиатурой 1-величину. Мультплексор 4 обеспечивает коммутацию информации с регистра 6, адресного входа 9 группы информационных входов 10 мультиплексоров в соответ.- ствии с управляющими потенциалами клавиатуры 1 на вход регистра 5. Регистр 5 предназнач-ен для сохранения операнда на время индикации. Содержимое регистра 5 отображается на элементах индикации блока 8. Регистр 6 предназначен для хранения адреса, предшествовавшего текущему адресу программы. Работу программного устройства разделяют на машинные такты, в течение каждого такта выполняется одна команда программы. Время такта разделяется на микротакты, в течение которых выполняется по одной микрокоманде. В процессе работы программного устройства на вход регистра 5 транслируется информация одной из входных шин через мультиплексор 4 (в соответ ствии с кодом на выходе 12 клавиатуры 1 набора информации). Поступающий по входу 9 текущий адрес программы постоянно сравнивается в блоке 2 с адресом синхронизации (выход 14J, установленным на клавиатуре 1 набора информагщи. В тактах, в которых сразненич-; отсутствует, текущий адрес со входа 9, вводится в регистр 6 по сигналу элемента И 7, а в регистре 5 сохраняется предьщущая информация. В случае сравнения текущего адреса с адресом синхронизации формируется выходной сигнал блоком 2 сравнения, который задерживается блоком 3 управляемой задержки на заданное клавиатурой 1 (выход 13) количество микротактов и поступает на управлянвдий вход регистра 5. По этому сигналу в регистр 5 вводится новая информация с выхода мультиплексора 4. Выходной сигнал блока 2 сравнения запрещает формирование сигнала элементом И 7, поэтому в регистр б в такте сравнения текущий адрес не вводится, т.е. сохраняется адрес предыдущей команды (ретроспективный адрес). Предложенное устройство обеспечивает выполнение основных операций, необходимых (удобных) для отладки программы: контроль очередного адреса программы, ксгнтроль операндов в текущей команде, контроль предыдущего адреса программы (ретроспективного адреса). Выбор операции производит оператор посредством органов управления (тумблеров) клавиатуры 1 набора информации. Управление клавиатург 1 производится по выходу 12 (тип информации) и выходу 13 (номер микротакта) . При контроле очередного адреса программы под действием сигналов выхода 12 на вход регистра 5 коммутируется адрес программы с входа 9. На адресном входе 9 в начале машинного такта имеется адрес текущей команды, в конце такта - адрес очередной команды. Если зада:ть по выхо ду 13 номер микротакта, соответствующего концу такта, то сигнал срав нения задерживается блоком 3 на соответствующее время, и в регистр 5 вводится информация в конце так-, та, т.е. адрес очередной команды. Этой операцией удобно пользоваться для проверки хода программы. Оператор устанавливает в. качестве адреса синхронизации начальный адрес прогграммы и на элементах индикации ото ражается код очередного адреса. Пос |ле этого получаемый адрес устанавли вается в качестве адреса синхронизации, а на элементах индикации отображается следующий адрес и т.д. При контроле опера1щов в текущей программе под действием сигналов выхода 12 на вход регистра 5 коммутируется группа информационных входов 10. Ввод в регистр 5 производится в микротакте, заданном выходо 13. С помощью этой операции можно проверить окончательные и промежуточные результаты программыf устава ливая соответствующий адрес синхронизации. При контроле ретроспективного ад реса под действием сигналов выходов 12 на вход регистра 5 - коммутирует ся содержимое регистра 6. Поскольку в регистр б вводится текущий адрес во всех тактах, кроме такта сравнения, то в регистр 5 - в такте сравнения введется адрес, предшествующий такту сравнения. Этой операцией удобно пользоваться при ложных запусках программ. Прослеживая ход пр граммы в обратном порядке (аналогич но пользованию операцией контроля очередного адреса) будет обнаружен источник ложного запуска. Использованием описанных операци контроля обеспечивает возможность о ладки программ как в процессе экспл атации , так и после разработки программ. Использование исправной конт рольной программы, обеспечивает такж возможность регулировки аппаратной части программного устройства после изготовления. Преимуществом предложенного устр ства перед известным является то. что изобретение позволяет отлаживать программу без программы - отладчика, т.е. весь объем памяти используется для рабочих программ, что увеличивает коэффициент использования оборудования. Кроме того, предложенное устройство позволяет отлаживать аппаратную часть программного устройства, что не обеспечивает известное устройство. Формула изобретения Устройство для отладки программ, содержащее клавиатуру набора информации, блок сравнения, и элемент И, причем первый выход клавиатуры набора информации соединен с первым входом блока сравнения, второй вход которого соединен с адресным входом устройства, выход блока сравнения соединен с инверсным входом элемента И, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения контроля предыдущего .и очередного адресов отлаживаемой программы, в него введены блок управляемой задержки, регистр и индикационный регистр, блок индикации и мультиплексор, причем вход синхронизации устройства соединен с прямым входом элемента И и первым входом блока управляемой задержки, выход которого соединен с синхронизирующим входом индикационного регистра, выход которого соединен с блоком индикации, второй и третий выходы клавиатуры набора информации соединены соответственно со вторым входом блока управляемой задержки и управляющим входом мультиплексора, выход которого соединен с информационным входом индикационного регистра, выход блока сравнения соединен с третьим входом блока управляемой задержки,адресный вход устройства с информационным входом регистра, с Первым информационным входом мультиплексора, выход элемента И - с управляющим входом регистра, выход которого соединен со вторым информационным входом мультиплексора, группа информационных входов мультиплексора соединена с группой информационных входов устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 489107, кл. Q Об F 11/00, 1975. 2.Авторс ое свидетельство СССР 277410, кл. 0 Об Р 9/00, 1970. 3.Заявка Японии I 53-41497, кл. а Об Р 11/00, 1978.

Г

т:

tvj

и:

V

/

Авторы

Даты

1982-09-23—Публикация

1979-06-20—Подача