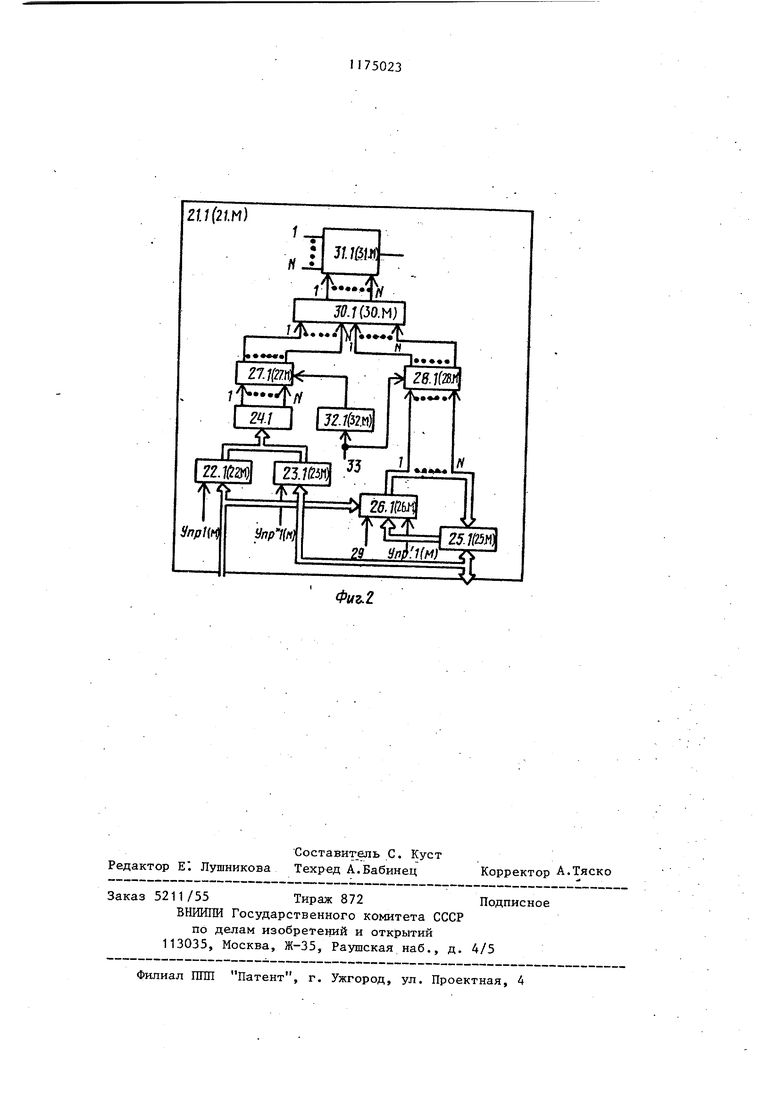

ленные выходы - с входами запоминающего устройства, выходы которого сое динены с входами четвертой группы управляемых вентилей и с однонаправ- леннь 1и входами шинного формирователя, входы первой группы управляемых вентилей и адресные входы запоминающего устройства соединены с выходами счетчика N, входы второй группы управляемых вентилей соединены с шинами кода N внутриблочной магистра ли, выходы первой и второй групп управляемых вентилей соединены между собой и с входами дешифратора кода N, выходы которого соединены с входами третьей группы управляемых вентилей, а выходы третьей и четвертой групп управляемых вентилей соединены соответственно с первыми и вторыми входами группы элементов ИЛИ, выходы которой соединены с управляющими входами группы N каналов. управляющий вход первой группы управляемых вентилей соединен с соответствующим данной плате коммутации выходом второй группы управляемых вентилей блока коммутации, управляющий вход второй группы управляемых вентилей соединен с соответствующим данной плате коммутации выходом первого дешифратора блока коммутации, один управляющий вход запоминающего устройства соеди нен с третьей внешней шиной управления, а второй управляющий вход его- с соответствующим данной плате коммутации выходом третьей группы управляемых вентилей блока коммутации, управляющий вход третьей группы управляемых вентилей соединен с выходом инвертора, а вход инвертора соединен с управляющим входом четвертой группы управляемых вентилей и с четвертой внешней шиной управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь огибающей | 1986 |

|

SU1709391A1 |

| МНОГОКАНАЛЬНЫЙ КОММУТАТОР | 1991 |

|

RU2026605C1 |

| СИСТЕМА РАСПРЕДЕЛЕНИЯ РЕСУРСОВ | 2000 |

|

RU2189073C2 |

| Устройство для управления загрузкой бункеров | 1983 |

|

SU1144955A1 |

| Устройство для ввода-вывода дискретных сигналов микроЭВМ | 1989 |

|

SU1681306A1 |

| Устройство для чтения микрофиш с автоматической установкой кадра | 1987 |

|

SU1425588A1 |

| Устройство обработки информации комплексной измерительной системы | 1990 |

|

SU1837283A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ МОНТАЖА, ПАРАМЕТРОВ ЭЛЕКТРИЧЕСКИХ ЦЕПЕЙ И ДИАГНОСТИКИ НЕИСПРАВНОСТЕЙ СЛОЖНЫХ УСТРОЙСТВ ЭЛЕКТРОАППАРАТУРЫ И ТОКОРАСПРЕДЕЛИТЕЛЬНЫХ СЕТЕЙ | 2008 |

|

RU2377585C1 |

| Система для контроля положения секций морской многоканальной сейсмокосы | 1981 |

|

SU972438A1 |

| Устройство для управления режимом обмена мажоритарно-резервированной системы | 1981 |

|

SU1058097A1 |

КОММУТАТОР, содержащий последовательно соединенные формирователь тактовых импульсов и счетчики N, М и Р, Р блоков коммутации, каждый из которых содержит переключающее устройство и дешифраторы кода М и Р, входы которых соединены с выходами соответствующих счетчиков, выходы дешифратора кода Р соединены с входами переключающего устройства, выход которого соединен с управляющим входом дешифратора кода М и М плат коммутации, каждая из которых содержит дешифратор кода N и группу N каналов, отличающийся тем, что, с целью расширения функциональных возможностей путем увеличения количества режимов работы, в каждый блок коммутации введено три групп.ы управляемых вентилей, инвертор, два дешифратора, второе переключающее устройство и шинный формироватапь с разрядностью кодов N, М и Р, а в каждую плату коммутации - четыре группы управляемых вентилей, группа элементов ЮШ, инвертор, запоминающее устройство, содержащее N ячеек памяти с разрядностью кодов N, М и Р и шинный формирователь с разрядностью кодов N, М и Р, причем в каждом блоке коммутации выходы депгифратора кода М соединены с входами первой группы управляемых вентилей, управляющий вход которой соединен с первой внешней ЛШ1НОЙ управления, а выходы соединены с входами второй и третьей групп управляемых вентилей, управляющий вход второй группы управляемых вентилей соединен с выходом инвертора, вход которого соединен с управляю1Щ1м входом третьей группы с управляемых вентилей и с второй 5 внешней шиной управления, двунаправленные входы-выходы шинного формирователя соединены с внешней С wsss магистралью с разрядностью кодов N, М и Р, а однонаправленные выходы его соединены с однонаправленными входами и С внутриблочной магистралью с разрядностью кодов N, М н ,Р, входы первого дешифратора соедиИш с шинами кода М внугрнблочной магистрали, входы второго дешифраС/1 тора - с шинами кода Р внутриблочf Чцяцной магистрали, а входы второго дешифратора - с пмнами кода внутриблочной магистрали, выходы второго дешифратора соединены с входами второго переключающего устройства, выход которого соединен с одним из управляющих входов первого деш1-:фратора, а второй управляющий вход первого дешифратора соединен с входом инвертора, в каждой плате коммутации двунаправленные входы-вьсходы шинного формирователя соединены с внутриблочной магистралью, а однонаправ

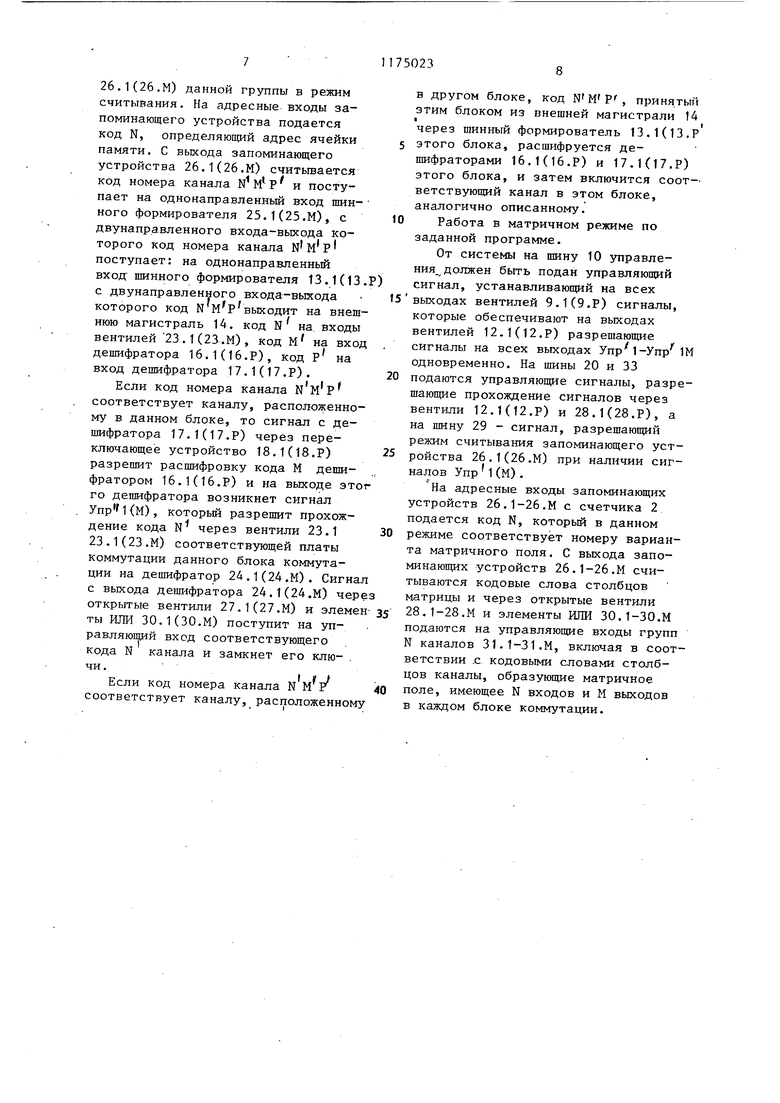

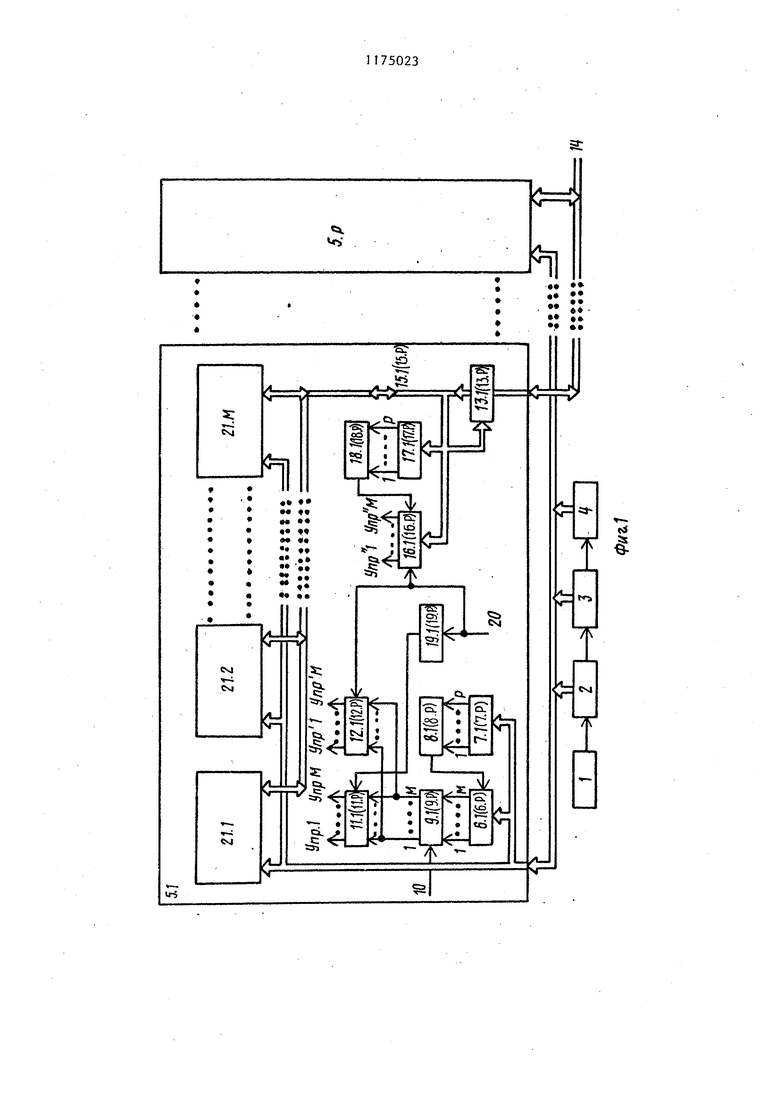

Изобретение относится к измерительной технике, в частности к электронным коьмутаторам информационных систем и систем диагностики. Цель изобретения - расширение функциональных возможностей путем увеличения количества режимов работы коммутатора. На фиг. 1 представлена структурная электрическая схема коммутатора; на фиг. 2 - структурная электрическая схема платы коммутации. Коммутатор содержит формирователь 1 тактовых импульсов, к выходу которого подключены последовательно соединенные счетчики N, М и Р 2 - 4 соответственно, блоки 5.1-5.Р комм:тации, каждый из которых содержит дешифратор 6.1(6.Р), входы которого соединены известным способом с выходами счетчика 3, дешифратор 7.1(7 входы которого соединены известным способом с выходами счетчика 4, переключающее устройство 8.1(8.Р), входы которого соединены известным способом с выходами 1-Р дешифратора 7.1 (7.Р), а выход соответствующий номеру данного блока, - с управляющим входом дешифратора 6i1 (6,Р), первую группу управляемых вентилей 9.1{9.Р), входы которой соединены с выходами 1-м дешифратора 6.1(6.Р), а управляющий вход с первой внешней шиной 10 управления, вторую и третью группы управляемых вентилей 11.1(11.Р) и 12.1(12.Р) соответственно, входы которых соединены между собой и с выходами 1-М группы управляемых вентилей 9.1(9.Р), шинньй формирователь 13.1(13.Р) с разрядностью кодов N, М и Р, двунаправленные входы-выходы которого соединены с внешней магистралью 14 с разрядностью кодов N, М и Р, а однонаправленные входы и выходы соединены между собой и внутри блочной магистралью 15.1(15.Р) с разрядностью кодов N, М и Р, первый и второй дешифраторы 16.1(16.Р) и 17.1(17.Р) соответственно, причем входы дешифратора 16.1(16.Р) соединены с шинами кода М, а входы дешифратора 17.1(17.Р) с шинами кода Р внутриблочной магистрали 15.1(15.Р) второе переключающее устройство 18.1(18.Р), входы которого соединены с выходами 1-Р

дешифратора 17.1(17.Р), а выход, соответствующий номеру данного блока - с вторым управляющим входом дешифратора 16.1(16.Р), инвертор 19.1(19.), выход которого соединен с-управляющим входом группы управляемых вентилей 11.1(11.), а вход - с первым управляющим входом дешифратора 16.1(16.) и с второй внешней шиной 20 управления, платы коммутации 21.1-21.М, каждая из которых содержит первую и вторую группы управляемых вентилей 22.1(22 и 23.1(23.М) соответственно, дешифр тор 24.1(24.М), причем входы группы управляемых вентилей 22.1(22.М) соединены с выходами счетчика 2, входы группы управляемых вентилей 23.1(23 соединены с шинами кода N внутриблочной магистрали 15.1(15.М), управляющий вход Упр.1(М) группы управляемых вентилей 22.1(22.М) соединен с соответствующим данной плате коммутации выходом группы управляемых вентилей 11.1(11.) данного блока коммутации, управляющий вход Упр 1 (М) группы управляемых вентилей 23.1(23.М) соединен с соотзетстэуюш м данной плате коммутации выходом дешифратора 16.1(16.) данного блока коммутации, а выходы групп вентилей 22.1(22.М) и 23.1(23. соединены между собой и с входами

дешифратора 24.1(24.М), шинньй формирователь 25.1(25.М) с разрядностью кодов N, Ми, запоминающее устройство 26.1(26.М), содержащее N ячеек памяти С разрядностью кодов N, М и , третью и четвертую группы управляемых вентилей 27.1(27. и 28.1(28.М) соответственно, причем, двунаправленные входы-выходы шинного формирователя 25.1(25.М) соединены с внутриблочной магистралью 15.1 15.1(15.), однонаправленные выходы - с входами запоминающего устройства 26.1(26.М), адресные входы которого соединены с выходами счетчика 2, первый управляющий вход - с третьей внешней шиной 29 управления, второй управляющий вход Упр 1 (М) с соответствующим данной плате коммутации выходом группы управляемых вентилей 12.1(12.) данного блока коммутации, а выходы - с однонаправленными входами шинного формирователя 25.1(25.М) и с входами группы управляемых вентилей 28.1

Коммутатор работает следующим образом.

Перед началом работы подаются сигналы, определяющие один из режимов, а, именно: циклический, программирования, циклический по заданной программе, матричный по заданной программе, а также переключающее устройство 8.1(8.) в каждом блоке установлено в положение, соответствующее номеру данного блока.

абота в циклическом режиме.

От системы на внешние щины 10, 20, 33 управления должны быть поданы сигналы управления, разрешающи прохождение сигналов через группы вентилей 9.1(9.), 11.1(11.) и 27.1(27.М) и запрещающие прохождение сигналов через группы вентилей 12.1(12.) и 28.1(28.М), а шинные формирователи 13.1(13.) и 25.1(25.и) известным способом переведены в пассивное состояние. С выхода формирователя 1 тактовых импульсов тактовые импульсы подаются: на вход счетчиков 2.3 и 4. От счетчиков 2. 3 и 4 поступает код, разрядность которого соответствует количеству каналов в группе N, количеству групп каналов :в блоке коммутации М и количеству блоков коммутации (код N, М, ). Переключающее устройство 8.1(8.) в каждом блоке установлено в соответствии с номером данного блока. При совпадении кода , поданного на дешифратор 7.1(7.), с номером данного блока на выходе переключающего устройства 8.1(8.Р) устанавливается сигнал, разрешающий прохождение сигналов через дешифратор 6.1(6.Р). Сигнал с выхода дешифратора 6.1(6.Р через открытые вентили 9.1(9.Р) и 11.1(11.Р) подается на управляющий вход вентилей 22.1(22.М), разрешая прохождение через них кода N на вход дешифратора 24.1(24.М), с вькода которого сигнал через открытые вентили 27.1(27.Р) и элементы ИЛИ 30.1(ЗО.М) поступает на разрешающий вход соответствующего кана ла в группе N каналов 31.1(31.М).

Работа в режиме программирования

Программирование циклического режима. От системы на внешние шины 10 20 и 33 управления подаются сигналы управления, запрещающие прохождение сигналов через вентили 11.1(11.Р) и 27.1(27.Р) и разрешающие прохождение сигналов через вентили 12.1(12.Р), а на шину 29 - сигнал управления, устанавливающий режим записи запоминающего устройства 26.1(26.М) при наличии сигнала Упр 1(М). Шинные формирователи 13.1(13.Р) и 25.1(25.М) известным способом устанавливаются в режим приема информации.

От счетчиков 2-4 подается код JMP. Из внешней шины 14 подается код номера канала N М Р , в частном случае код счетчика NMP и код N М Р могут совпадать.

Код счетчика М, Р расшифровывается аналогично предьщущему режиму. Код счетчика N во всех режимах, кроме первого, является адресом ячейки запоминающего устройства 26.1(26 Код NMP проходит через шинный формирователь 13.1(13.Р) на вход шинного формирователя 25. 1(25.М), а с выхода его - на входы запоминающего устройства 26.1.(26.М). При наличии на адресных входах запоминающего устройства 26.1(26.М) кода счетчика N и сигнала Упр 1(М) на управляющем входе в соответствующую ячейку записывается код N М Р . Количество ячеек памяти равно количеству каналов в группе N. Таким образом, в запоминающем устройстве 26.1(26.М) данной группы N каналов может быть последовательно записано N номеров каналов, каждый из

которых может находиться в любой плате коммутации 21.1-21.М любого блока коммутации 5.1-5.Р, в том числе и в данной группе данного блока. В запоминающих устройствах всех плат коммутации всех блоков коммутации последовательно могут быть записаны адреса всех NMP каналов в любой

заданной последовательности. При необходимости эта последовательность может быть полностью или частично оперативно изменена.

Программирование матричной структуры производится аналогично программированию циклического режима в произвольной последовательности. При этом код счетчика N определяет , номер конфигурации матричной структуры (матричного поля) а код к м р кодовое слово столбца матрицы. При матричной структуре группа N каналов составляет столбец матрицы, а одноименные каналы групп N каналов всех плат коммутации 21.1 - 21.М составляют строку матрицы. Таким образом, каждый из Р блоков представляет собой матрицу (матричное поле) , которые (матрицы) могут объединяться в соответствии с требованиями системы.. .

В каждом запоминающем устройстве 26.1(26.М) может быть записано N вариантов кодовых слов столбца матрицы. Следовательно, во всех М платах коммутации одного блока может быть записано N вариантов матрицы NX М

Работа в циклическом режиме по заданной программе.

От системы на внешние шины 10, 20 и 33 управления должны быть поданы сигналы управления, разрешающие прохождение сигналов через вентили 9.1(9.Р), 12.1(12.Р) и 27.1(27.М) и дешифратор 16.1(16.Р). На внешнюю щину 29 управления подается сигнал, обеспечивающий режим считывания запоминающего устройства 26.1(26.М) при наличии разрешающего сигнала Упр 1(М).

От счетчиков 2, 3 и 4 подается код NMP. Код МР расшифровывается дешифраторами 6.1(6.Р) и 7.1(7.Р), как быпо описано вьш1е. При этом сигнал Упр 1(М), соответствующий данной группе каналов, устанавливает запоминающее устройство

Если код номера канала NM соответствует каналу, расположенному в данном блоке, то сигнал с дешифратора 17.1(17.) через переключающее устройство 18.1(18.) разрешит расшифровку кода М дешифратором 16.1(16.) и на выходе это го дешифратора возникнет сигнал Упр1(М), который разрешит прохождение кода N через вентили 23.1 23.1(23.М) соответствующей платы коммутации данного блока коммутации на дешифратор 24.1(24.М). Сигна с выхода дешифратора 24.1(24.М) чер открытые вентили 27.1(27.М) и элеме ты ИЛИ ЗО.КЗО.М) поступит на управляющий вход соответствующего кода N канала и замкнет его клю- .

и Если код номера канала N М F

соответствует каналу, расположенном

в другом блоке, код , принятый этим блоком из внешней магистрали 14 через шинный формирователь 13.1(13. этого блока, расшифруется дешифраторами 16.1(16.) и 17.1(17.) этого блока, и затем включится соответствующий канал в этом блоке, аналогично описанному.

абота в матричном режиме по заданной программе.

От системы на шину 10 управления, должен быть подан управляющий сигнал, устанавливающий на всех выходах вентилей 9.1(9.) сигналы, которые обеспечивают на выходах вентилей 12.1(12.) разрешающие сигналы на всех выходах Упр 1-Упр Ш одновременно. На шины 20 и 33 подаются управпяютще сигналы, разрешающие прохозвдение сигналов через вентили 12.1(12.) и 28.1(28.), а на шИну 29 - сигнал, разрешающий режим считывания запоминающего устройства 26.1(26.М) при наличии сигналов Упр1(м).

На адресные входы запоминающих устройств 26.1-26.М с счетчика 2 подается код N, который в данном режиме соответствует номеру варианта матричного поля. С выхода запоминающих устройств 26.1-26.М считываются кодовые слова столбцов матрицы и через открытые вентили 28.1-28.М и элементы ИЛИ 30.1-30.М подаются на управляющие входы групп N каналов 31.1-31.М, включая в соответствии .с кодовыми словами столбцов каналы, образующие матричное поле, имеющее N входов и М выходов в каждом блоке коммутации.

М

t

2/./f2/.M)

-T

f/l| 1.

I Ж№м)| IJ....-,.,

j«

w.

З./

I j I игуМ о t 1

|гг./(ЗД| |25. rpiii /NO. . I .

УпрКн

npHt

я./f

(««

T j

H

I

Ндэ

т

29 ynftl(M) A

| Ртутный разрежающий насос | 1922 |

|

SU799A1 |

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| ПРИСПОСОБЛЕНИЕ ДЛЯ ПОДЪЕМА И ОПУСКАНИЯ КОРПУСОВ ПЛУГА | 1926 |

|

SU7078A1 |

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

Авторы

Даты

1985-08-23—Публикация

1984-03-26—Подача