вода с измененной адресной частью команд ввода-вывода, нанрнмер, для унравления несколькими идентичными ПУ, имеющими различиые номера, или к нрограммной перестройке исходной программы ввода-вывода за счет модификации адресной части всех команд ввода-вывода. В результате увеличиваются объем оперативной памяти и временные издержки нри программировании ввода-вывода.

Целью изобретения является расширение области применения устройства путем физического изменения нумерации ПУ.

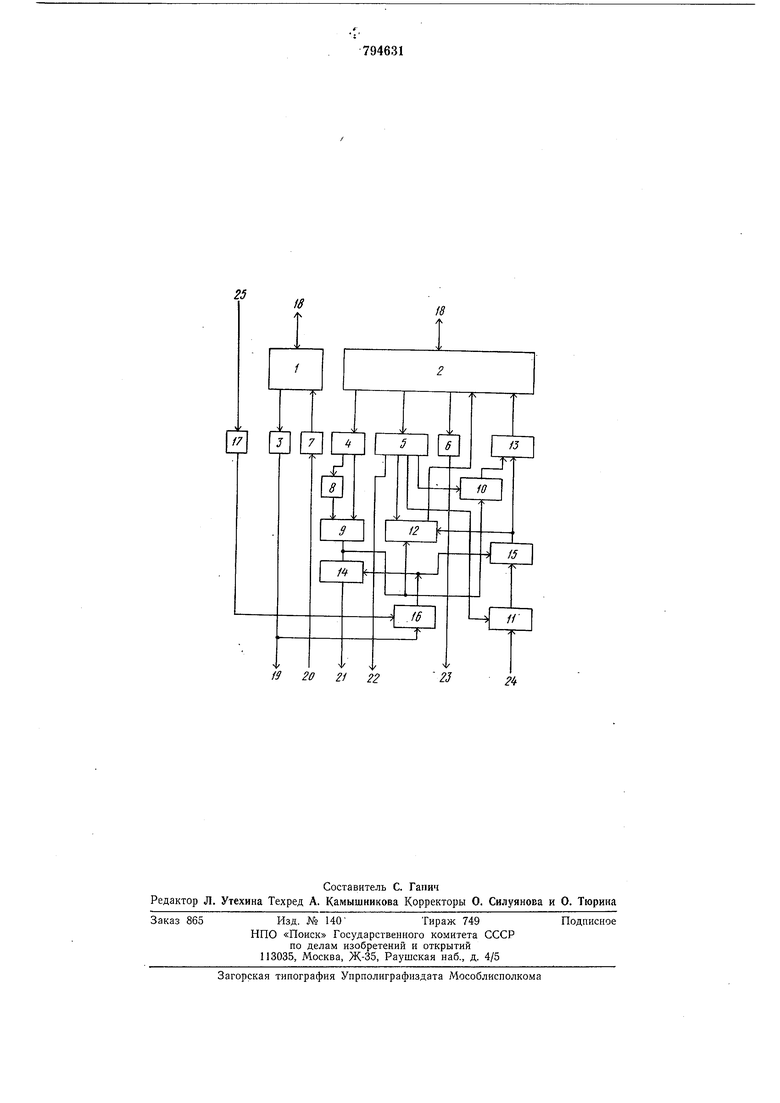

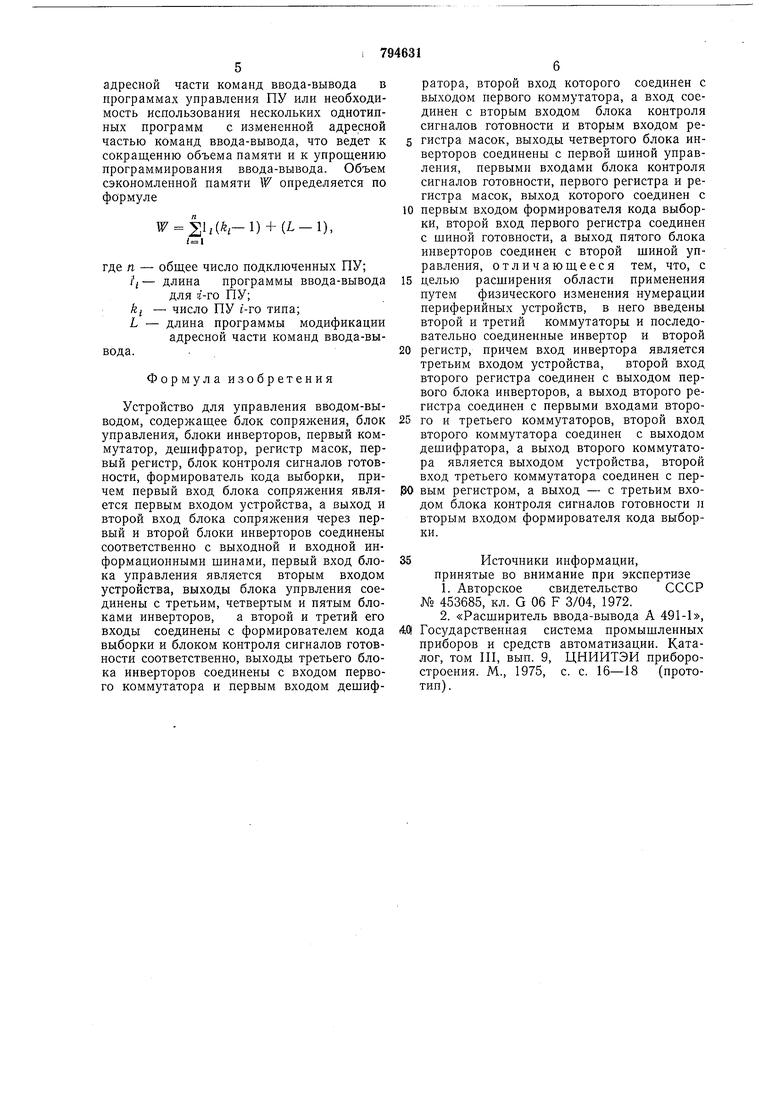

С этой целью в иредложепное устройство введены второй регистр (иастройки), инвертор, второй и третий коммутаторы и шина записи. При этом первый вход второго коммутатора соединен с шиной выборки ПУ. Вторые входы второго и третьего коммутаторов соединены с выходом первого регистра, первый вход которого соединен с выходом первого блока инверторов, а второй - с выходом инвертора, вход которого соединен с управляюш;ей шиной процессора. Выход первого регистра соединен с первым входом третьего коммутатора, выход которого соединен с третьим входом блока контроля сигналов готовности и вторым входом формирователя кода выборки. На чертеже показана структурная схема предлагаемого устройства.

Устройство содержит блок 1 сопряжения, блок 2 управления, блоки инверторов 3-7, первый коммутатор 8, дешифратор 9, регистр 10 масок, иервый регистр 11, блок 12 контроля сигналов готовности, формирователь 13 кода выборки, второй коммутатор 14, третий коммутатор 15, второй регистр 16, иивертор 17, шины 18 связи с ироцессором, в 1ходную 19 и входную 20 информационные шины, шину выборки 21, шины унравления 22, 23, шину готовности 24 и шину записи 25.

Устройство для управления вводом-выводом работает следующим образом.

В режиме передачи ииформации из процессора в ПУ данные передаются через блок 1 сопряжения, блок инверторов 3 и выходную информационную шину 19. В обратном направлении данные передаются через входную информационную шину 20, блок инверторов 7 и блок 1 сопряжения. Совместно с информацией через блок 2 управления и блок инверторов 4 на первый коммутатор 8 и дешифратор 9 иоступает код номера ПУ. Код номера дешифрируется, и на одном из выходов дешифратора 9 вырабатывается сигнал выборки, который через второй коммутатор 14 и шину 21 выборки поступает в соответствующее ПУ. Сигналы управления обменом через блок 2 управления, блоки инверторов 5, О по управляющим шинам 22, 23 поступают в выбранное ПУ.

Сигналы готовности от ПУ поступают но шние 24 готовности и запоминаются в регистре 11. При этом каждому г-му сигналу выборки в шине 21 выборки соответствует г-й сигнал готовности на пш5 ие 24 готовности. Приоритет ПУ определяется позицией сигнала выборки на выходе дешифратора 9 и соо1ветствующей этому сигналу позицией сигнала готовности на выходе регистра И. Таким образом, позиция сигнала готовности в регистре 11 всегда связана с номером ПУ, поэтому прн изменении позиции сигиала выборки на выходе дешифратора 9 должна изменяться соответственно и нозиция сигнала готовности 15 на входе блока 13 формирователя кода выборки. В противиом случае код вызова программы но инициативе выбранного ПУ через систему прерывания не будет соответствовать номеру ПУ. Второй коммутатор 20 14 выполняет изменение позиции /-го сигнала выборки, формируемого на выходе дешифратора 9 в соответствии с кодом, записанным в регистре 16, и через шииу 21 выполняет выборку f-ro ПУ. В соответствии 5 с этим же кодом .регистра 16 третий коммутатор 15 выполняет изменение позиции г-го сигнала готовностн в /-Й сигнал готовности. Запись кода настройки управляется процессором через инвертор 17 по шине 25 0 записи.

Запрещение и разрещение сигиалов готовности вынолняется регистром 10 масок в блоке 13 формирователя кода выборки. Установка и сброс /-го разряда регистра 10 5 масок выполняется процессором через блок 2 управления и блок инверторов 5 при наличии на выходе дешифратора 9 /-го сигнала выборки. Одновремеиная Зстановка или сброс,всех разрядов регистра 10 масок 0 выполияется без сигналов выборки по снециальиым командам от процессора. При маскировании всех сигналов готовностн прерывание процессора запрещается. Опрос состояния /-ГО сигнала готовности, посту5, пающего в блок 12 контроля сигналов готовности с выхода третьего коммутатора 15, выполняться программно сигналами управления от процессора через блок 2 управления и блок инверторов 5 при на0 лнчии /-ГО сигнала выборки на выходе дещифратора 9.

Коммутаторы 14 и 15 в предлагаемом устройстве выполняют функции перекоммутации п входных в п выходных сигналов в 5 соответствии с кодом, хранящимся в регистре 16, и могут быть реализованы известными способами (см. «Косвенная бинарная п-мерная матрица микропроцессоров. - «Экспресс-информация, серия «Вычисли0 тельная техника, 1978, № 8, с.с. 14-24). Введение новых элементов и связей позволяет реализовать возможность физического изменения нумерации ПУ программным снособом. Такое решение исключает 5 необходимость программной модификации

адресной части команд ввода-вывода в программах управления ПУ или необходимость использования нескольких одиотипных программ с измененной адресной частью команд ввода-вывода, что ведет к сокращению объема памяти и к упрощению программирования ввода-вывода. Объем сэкономленной памяти W определяется по формуле

W li(k,l)

(i-1),

где п - общее число подключенных ПУ; /; - длина программы ввода-вывода

для if-го ПУ;

kf - число ПУ t-ro типа; L - длина программы модификации адресной части команд ввода-вывода.

Формула изобретения

Устройство для управления вводом-выводом, содержащее блок сопряжения, блок управления, блоки инверторов, первый коммутатор, дешифратор, регистр масок, первый регистр, блок контроля сигналов готовности, формирователь кода выборки, причем первый вход блока сопряжения является первым входом устройства, а выход и второй вход блока сопряжения через первый и второй блоки инверторов соединены соответственно с выходной и входной информационными шинами, первый вход блока управления является вторым входом устройства, выходы блока упрвления соединены с третьим, четвертым и пятым блоками инверторов, а второй и третий его входы соединены с формирователем кода выборки и блоком контроля сигналов готовности соответственно, выходы третьего блока инверторов соединены с входом первого коммутатора и первым входом дешифратора, второй вход которого соединен с выходом первого коммутатора, а вход соединен с вторым входом блока контроля сигналов готовности и вторым входом регистра масок, выходы четвертого блока инверторов соединены с первой шиной управления, первыми входами блока контроля сигналов готовности, первого регистра и регистра масок, выход которого соединен с

10 первым входом формирователя кода выборки, второй вход первого регистра соединен с шиной готовности, а выход пятого блока инверторов соединен с второй шиной управления, отличающееся тем, что, с

15 целью расширения области применения путем физического изменения нумерации периферийных устройств, в него введены второй и третий коммутаторы и последовательно соединенные инвертор и второй

20 регистр, причем вход инвертора является третьим входом устройства, второй вход второго регистра соединен с выходом первого блока инверторов, а выход второго регистра соединен с первыми входами второго и третьего коммутаторов, второй вход второго коммутатора соединен с выходом дешифратора, а выход второго коммутатора является выходом устройства, второй вход третьего коммутатора соединен с первым регистром, а выход - с третьим входом блока контроля сигналов готовности и вторым входом формирователя кода выборки.

35Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 453685, кл. G 06 F 3/04, 1972.

2.«Расширитель ввода-вывода А 491-1, 401 Государственная система промышленных

приборов и средств автоматизации. Каталог, том П1, вып. 9, ЦННИТЭИ приборостроения. М., 1975, с. с. 16-18 (прототип).

19 20 21 22

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода-вывода информации | 1983 |

|

SU1176340A1 |

| Устройство для сопряжения управляющей вычислительной машины с периферийными устройствами | 1983 |

|

SU1201841A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Устройство для сопряжения цифровых вычислительных машин | 1976 |

|

SU608151A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1990 |

|

SU1727126A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для сопряжения двух элект-РОННыХ ВычиСлиТЕльНыХ МАшиН | 1979 |

|

SU809147A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

Авторы

Даты

1981-01-07—Публикация

1979-02-08—Подача