.1

Изобретение откосится к вычислительной технике и может быгь использовано в системах автоматргческого управления и контроля, применяег к, напримерS в радиолокации.

Целью изобретения является повышение быстродействия коррелятора.

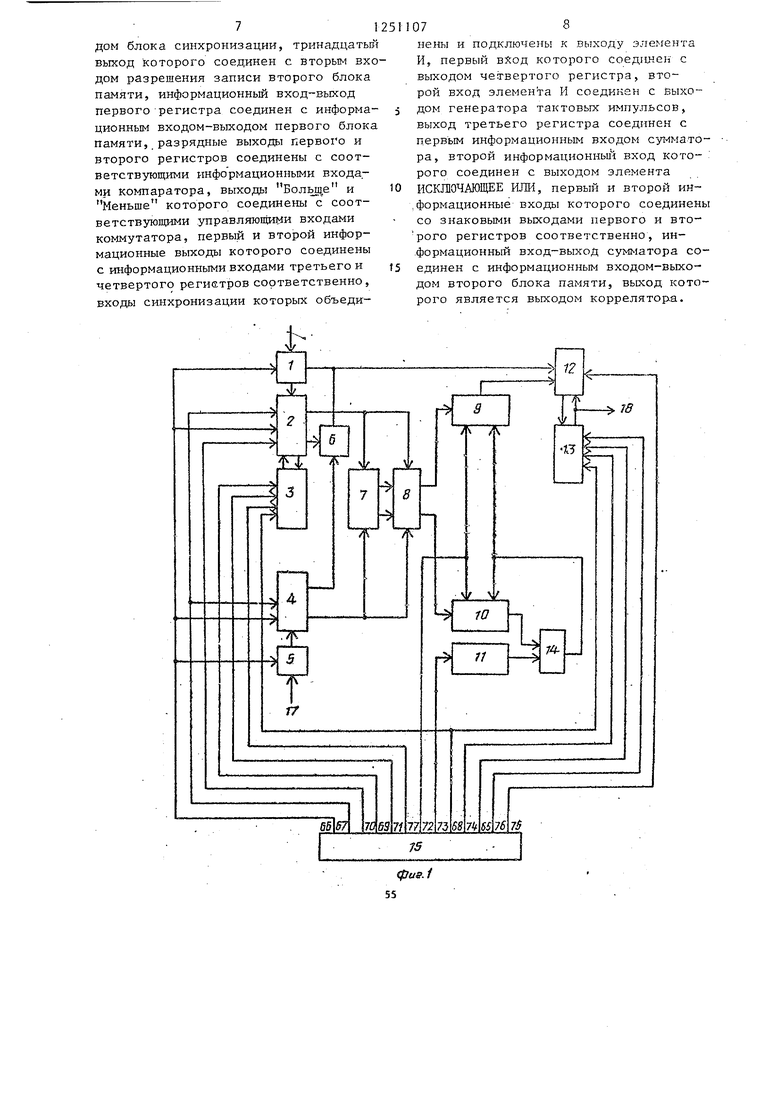

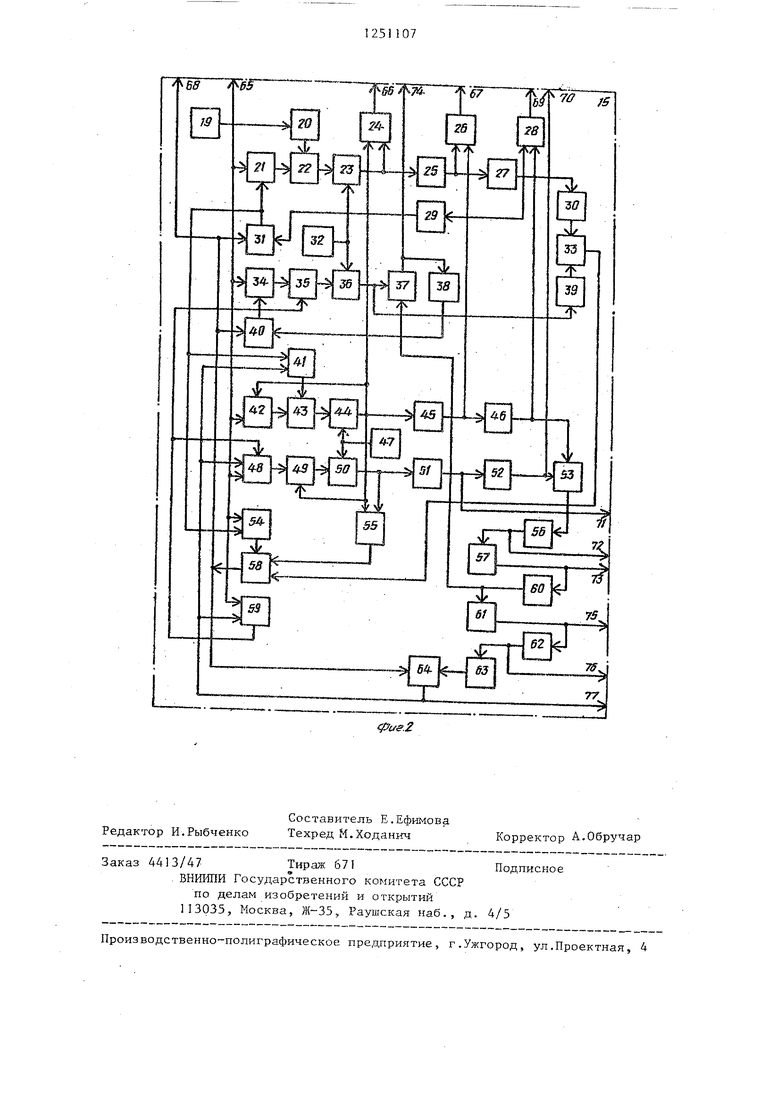

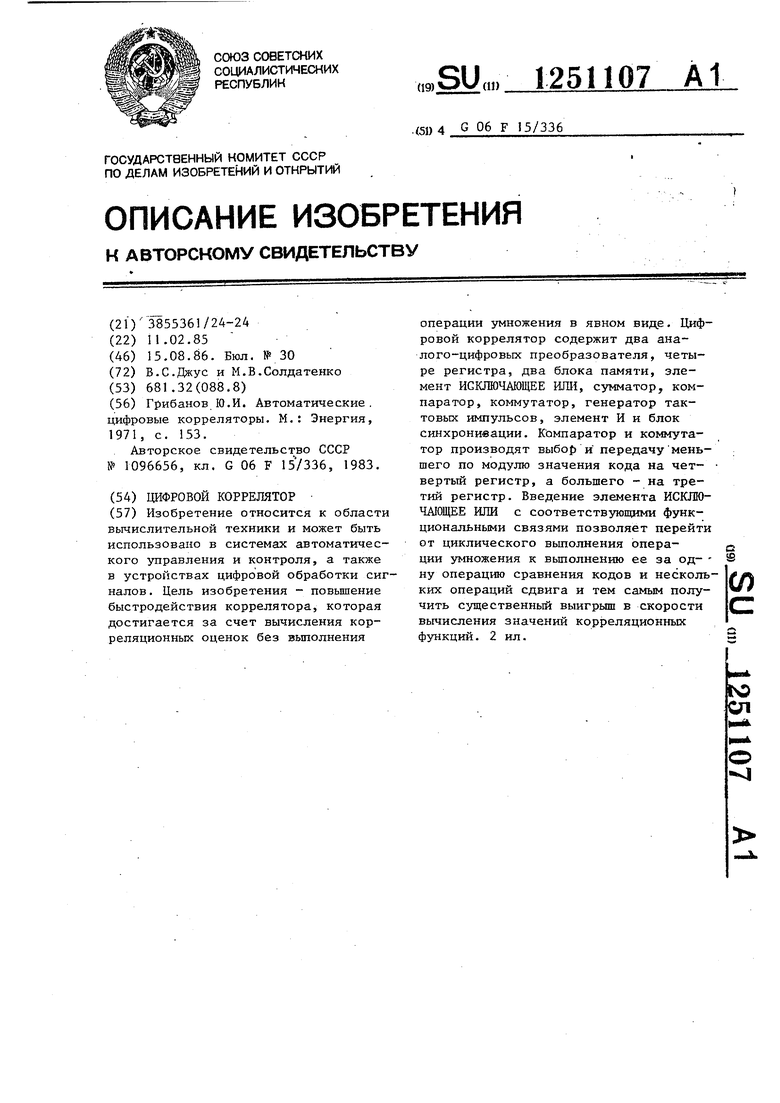

На фиг.1 представлена структурная схема жорреляторау на фиг.2 - структурная схема блока синхрониза- umi.

Коррелятор (фиг.1/ содержит первый аналого-цифровой преобразователь 1, первый регистр 2, первый блок 3 памяти, второй регистр 4, второй апа- лого-цифровой преобразователь 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6 компаратор 7 коммутатор 8, третга регистр 9, четвертый регистр 10, генератор 11 тактовых импульсов, сз мматор 12, второй блок 13 памяти, элемент И 14, блок 5 синхронизации, первый вход 16 коррелятора, второй вход 7 коррелятора, выход 18 коррелятора.

Блок 15 синхронизации коррелятора (фиг.2) содержит генератор 19 одиночного импульса, первый элемент 20 задержки, первый элемен г ИЛИ 21 , первый триггер 22, первый элемент И 23, первый элемент ИЛИ 24, второй элемент 25 задержки, третий элемент ШШ 26, третий элемент 27 задержки, четвертый элемент ИЛИ 28, четвертый и пятый элементы 29 и 30 задержки, второй элемент И 31, первый задающий генератор 32, пятый и шестой элементы ИЛИ 33 и 34, второй триггер 35 третий элемент И 36, седьмой элемент ИЛИ 37, шестой и седьмой элементы 38 и 3 задержки, четвертый элемент И 40, восьмой и девятый элементы ИЛИ 41 и 42, третий триггер 43, пятый элемент И 44, восьмой и девятый элементы 45 и 46 задержки, второй задшощий генератор 47, элемент РШИ 48, четвертый триггер 49, шестой элемент И 50, десятый и одиннадцатый элементы 51 и 52 задержкИуДесятый, одиннадцатьй и двенадцатый элементы ШП 53-55, двенадца-

NtmH

R.y(ut) м

sign у, 9 m

072

тьй и тринадцатьй элементы 56 и 57 за- дерглки, счетчики 58 и 59 адреса и произведений, четырнадцатьш, пятнадцатый, шестнадцатьй и семнадцатый элементы 60-63 задержки, седьмой элемент И 64, первый, третий,, четвертый, пятый, шестой, седьмой, девятьй, десятьи, пось мой, одиннадцатый, тринадцатый, двенадцатый и второй выходы 66, 67, 70, 69,71,77,72,73,68,74,65,76 и 75 соответственно.

Цифровой коррелятор работает следующим образом.

На входы 16 и 17 поступают соответственно сигналы x(t) и y(t). Пройдя через аналого-цифровые преобразова- тели 1 и 5, их оцифрованные модульные значения, представляемые в естественной форме, после хранения на соответствующих регистрах 2, 4 и задержки в первом блоке 3 памяти поступают на входы компаратора 7 и коммутатора 8. Последние обеспечивают передачу меньшего по модулю цифрового кода в третий регистр 9, а большего в четвертый регистр 10. Такое распределение цифровых кодов, по регистрам 9 и 10 фактически обеспечивает релейный метод вьиисления оценки корреляционной функции, так как в дальнейшем все вычислительные операции проводятся только над одним, меньшим по модулю, цифровым кодом, находящим- сз в третьем регистре 9. Дополнительно к этому в корреляторе производится анализ старшего разряда модульного значения большего цифрового кода, который обеспечивает коррецию меньшего цифрового кода с целью получения более высокой точности вьпшс- ления промежуточных произведений. Полученные таким образом модульные значения произведений поступают на вход суг-матора 12, на знаковый вход которого с выхода элемента ИСКЛОЧАЮЩЕЕ ИЛИ 6 поступает знак произведения. На сумматоре 12 совместно с вторым блоком 13 памяти формируется окончательная оценка корреляционной функции:

.

при )х,.,/ ;

2 , при /х J .

31

где Ktx (К|) - количество нулей (число сдвигов) между запятой и первой значащей цифрой входного кода Х. ц, (У;)) ,

Для организации синхронной работы отдельных блоков и вычисления оценки корреляционной функции параллельно-последовательным способом в. соответствии с выражением. (1) исполь зуется блок 15 синхронизации. Работа цифрового коррелятора синхронизируется четырьмя последовательностями импульсов, вырабатываемых блоком 15. Работа блока 15 начинается с выработ ки генератором .О 9 одиночного импульса управляющего сигнала 65 СБРОС. Данный управляющий сигнал обеспечивает установку в исходное нулевое, состояние блока 13, первого 22, второго 35, третьего 43 и четвертого 49 триггеров, а также счетчиков 58 адреса и 59 произведений. Задержанный в первом элементе 20 задержки управляющий сигнал СБРОС производит установку в единичное состояние первого триггера 22, разрешая передачу тактовых импульсов, формируемых первым задаюащм генератором 32, через первый элемент И 23 на вход последо- вательно соединенных второго 25 и третьего 27 элементов задержки. В результате с тактовой частотой первого задающего генератора 32 вырабатывается первая последовательность уп- равляющих сигналов:

Т-1 ПУСК АЦП - управляющий сигнал 66, обеспечивающий формирование и выдачу оцифрованных величин с вы- ходов первого и второго аналого циф- ровых преобразователей 1 и 5, а также перевод первого 2 и второго 4 регистров в нулевое состояние, при этом последние подготавливаются к : приему новой информации, поступающей с первого I и второго 5 аналого- цифровых преобразователей;

1-2 ЗАПИСЬ В РЕГИСТРЫ 1 и 2 С АЦП управляющий сигнал 67;

Т-З ЗАПИСЬ В БЛОК 3 - управляю- щий сигнал 69, обеспечивающий пара- фазную запись информации с выхода первого регистра 2 в ячейку памяти блока 3 по текущему адресу, сформированному счетчиком 58 адреса.

В результате после формирования т-1 раз первой последовательности управляющих сигналов блок 15 с так1074

ТОБОЙ частотой второг о задаюи сго генератора 47 вырабатывает вторую последовательность управляющих сигналов :

И-1 ПУСК АЦП - управляющий сигнал 66;

II-2 ЗАПИСЬ В РЕГИСТРЫ 1 И 2 С АЦП - отправляющий сигнал 67;

II-3 ЗАПИСЬ В БЛОК 3 - управляющий сигнал 69;

II-4 ЗАПИСЬ В РЕГИСТРЫ 9 и 10 - управляющий сигнал 72, обеспечивающий парафазную запись информации в регистры 9 и 10, поступающий с выхода коммутатора 8, управляемого компаратором 7;

11-5 ПУСК ГЕНЕРАТОРА - управляющий сигнал 73, обеспечивающий запус генератора 11;

II-6 СЧИТЫВАНИЕ С БЛОКА 13 - управляющий сигнал 74, обеспечивающий парафазное считывание информации в сумматор 12 с блока 13 по текущему адресу, сформированному счетчиком 58 адреса;

II-7 СЛОН{ЕНЖ - управляющий сигнал 75, обеспечивающий вьтолнение операции сложения в сумматоре 12;

II-8 ЗАПИСЬ В БЛОК 13 - управляющий сигнал 76, обеспечивающий пара- фазную запись информации с сумматора 1 2 в блок 13 по текущему адресу, сформированному счетчиком 58 адреса

III-1 СЧИТЫВАНИЕ С БЛОКА 3 - управляющий сигнал 71, обеспечивающий парафазное считывание информации в первый регистр 2 с блока 3 по текущему адресу; сформированному счетчиком 58 адреса;

III-2 ЗАПИСЬ В РЕГИСТР 2 - управляющий сигнал 70, обеспечивающий парафазную запись информации с блока 3 в первый регистр 2;

III-8 РЕГЕНЕРАЦИЯ - управляющий сигнал 77, обеспечивающий регенераци (перезапись информации с i-й ячейки в (1-1)-ю ячейку памяти) информации в блоке 3, Одновременно данный управляющий сигнал произт одит перевод третьего триггера 43 в едини чное состояние (п1эи этом разрешается выработка второй последовательности управляющих сигналов), четвертого триггера 49 в нулевое СОСТОЯНИЕ (выработка третьей последовательности управляющих сигналов прекрап1ается) , а также поступает на вход счетчика 59

произведений для формирования следующего (большего на единицу младшего разряда) номера текущего произведения .

Выработка второй и третьей последовательностей управ.ь-яющих сигналов прекращается сигналом переполнения, вырабатываемым счетчиком 59 произведений. Сигнал переполнения переводит четвертый триггер 49 в нулевое состояние, а второй триггер 35 в единичное состояние, В результате после формирования N-ra раз второй по следовательности управляющих сигналов и (N-m)(m-l) раз третьей последовательности управляющих сигналов блок 53 с тактовой частотой первого задающего генератора 32 выраба- тывйет четвертую последовательность управляюпцта сигналов s

IV-J СЧИТЫВАНИЕ С БЛОКА 13 - управляющий сигнал 74, обеспечивающий парафазное считывание информации на устройство индикации с блока 13 по текущему адресу, сформированному счетчиком 58 адреса. Данный управляющий сигнал через седьмой элемент 39 задержки поступает на вход счетчи- ка 58 адреса для формирования следующего (большего на единицу младшего разряда) номера текущего адреса считывания , Одновременно управляющий Сигнал 74 через шестой элемент 38 задержки поступает на вход четвертого элемента. И 40. Последний с учетом содержимого счетчика 58 адреса формирует сигнал перевода в. нулевое состояние второго триггера 35, Управ- ляющий сигнал 68 блока 15 представляет собой L-разрядный код адреса, поступающий на входы блоков 3 и 13.

На этом работа цифрового коррелятора прекращается.

Выходы управляющих сигналов I-, , 1-2 и , 1-3 и IT.-3, являю- ищеся общими для отдельных узлов цифрового коррелятора, объединены че рез двз входовые логические элементы ИЛИ 24, 26, 28 и 37 соответственно. Логические элементы И 3L 40 и 64 являются многовходовыми с числом входов L+1, где L - разрядность двоично го счетчика 58 адреса., и представляют собой элементы неполного дешифратора .

10

,15 20

25 зо о

55

45

50

Формула и 3 о б р е т а м н я

Цифровой коррелятор, содержавши первый и второй аналого-цифровые преобразователи, первый, второй, третий и четвертый регистры, первый и второй блоки памяти, ком таратор, коммутатор, элемент И, сумматор, блок синхронизации и генератор тактовых импульсов, причем информационные входы первого и второго аналого-цифровых преобразователей являются первым и вто- pbiNS информационными входами коррелятора соответственно, выходы первого и второго аналого-цифровых преобразователей соединены с информационными входами rtepBoro и второго регистров соответственно, разрядные выходы которых соединены с соответ- ствузощими информационными входами коммутатора, объединенные входы запуска первого и второго аналого-цифровых преобразователей соединены с первым выходом блока синхронизации, вход разрешения сум1 1ирования сут гматора со единен с вторым выходом блока синхронизации, отличающийся тем, что, с целью повьшения быстродействия, в него введен элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, третий выход блока синхронизации подключен к объединен ным входам разрещения записи первого и второго регистров, объединенные входы обнуления которых подключены к первому выходу блока синхронизации, четвертый выход которого соединен с дополнительным входом разрешения записи первого регистра, пятый выход блока синхронизации соединен с первым входом разрешения записи перво- то блока памяти, вход считьшания которого соединен с шестым выходом блока синхронизации, седьмой выход которого соединен с вторым входом разрешения записи первого блока памяти, адресные входы первого и второго блоков памяти объединены и подключены к восьмому выходу блока синхронизации, девятый выход которого подключен к объединенным входам разрешения записи третьего и четвертого регистров,: десятьш выход блока синхронизации соединен с входом запуска генератора тактовых импульсов, одиннадцатый выход блока синхронизации соединен с входом считывания второго блока памяти, первый вход разрешения записи которого соединен с двенадцатым выхо71

дом блока синхронизации, тринадцатьБт выход которого соединен с вторым входом разрешения записи второго блока памяти, информационный вход-выход первого регистра соединен с информа- ционным входом-выходом первого блока памяти,,разрядные выходы первого и второго регистров соединены с соответствующими информационными входами компаратора, выходы Больще и Меньше которого соединены с соответствующими управляющими входами коммутатора, первый и второй информационные выходы которого соединены с информационными входами третьего и четвертого регистров соответственно, входы синхронизации которых объеди1078

нены и подключены к выходу элемента И, первый вХод которого соедилен с выходом четвертого регистра, второй вход элемента И соединен с выходом генератора тактовых импульсов, выход третьего регистра соединен с первым информационным входом су1-1мато ра, второй информационньй вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй ин,формационные входы которого соединены со знаковыми выходами первого и вто рого регистров соответственно, ин- .формационный вход-выход сумматора соединен с информационным входом-выходом второго блока памяти, выход которого является выходом коррелятор1а.

Редактор И.Рыбченко

Составитель Е.Ефимова Техред М.Ходанич

Заказ 4413/47Тираж 67 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35,, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор А.Обручар

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для определения корреляционной функции | 1987 |

|

SU1501086A1 |

| Устройство для диагностирования логических схем | 1988 |

|

SU1684757A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1221666A1 |

| Устройство для определения взаимной корреляционной функции | 1987 |

|

SU1427383A1 |

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

| Устройство для считывания информации | 1989 |

|

SU1693617A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1982 |

|

SU1053119A1 |

Изобретение относится к области вьиислительной техники и может быть использовано в системах автоматического управления и контроля, а также в устройствах цифровой обработки сигналов . Цель изобретения - повышение быстродействия коррелятора, которая достигается за счет вычисления корреляционных оценок без выполнения операции умножения в явном виде. Цифровой коррелятор содержит два аналого-цифровых преобразователя, четыре регистра, два блока памяти, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматор, компаратор, коммутатор, генератор тактовых импульсов, элемент И и блок синхронивации. Компаратор и коммутатор производят выбор и передачу меньшего по модулю значения кода на чет- вертый регистр, а большего - на третий регистр. Введение элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с соответств тощими функциональными связями позволяет перейти от циклического вьтолнения операции умножения к вьшолнению ее за од- - ну операцию сравнения кодов и нескольких операций сдвига и тем самым получить существенный выигрыш в скорости вычисления значений корреляционных функций. 2 ил. i (Л

| Грибанов Ю.И | |||

| Автоматические, цифровые корреляторы | |||

| М.: Энергия, 1971, с | |||

| Паровозный золотник (байпас) | 1921 |

|

SU153A1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-15—Публикация

1985-02-11—Подача