формационным входом первого дешифратора i-ro блока границ счета, отличающееся тем5 4TQ, с целью сокращения объема оборудования в устройство введены блок вычитания, блок сравнения, группа элементов И, счетчик, генератор импульсов, первый, второй, третий и четвертый триггеры, семь элементов И, элемент ИЛИ и элемент задержки, а в каждый блок границ счета введены четвертый и пятый элементы ИЛИ, второй дешифратор, второй элемент И и элемент задержки, причем входы текущего и начального адресов программы устройства соединены с входами операндов блока вычитания, выход разности которого соединен с первым входом блока сравнения, вход длины программы устройства соединен с вторым входом блока сравнения, выход которого соединен с первым входом первого элемента И, единичным входом первого триггера и первыми входами элементов И группы, вход кода команды устройства соединен с вторыми входами элементов И группы, выходы которых соединены с информационными входами счетчика, тактовый вход устройства соединен с тактовым входом блока сравнения, информационный выход и выход переполнения счетчика соединены соответственно с входами второго элемента И и элемента ИЛИ, выход которого соединен с R-входами первого и второго триггеров, вход начальной установки устройства соединен с вторым входом первого элемента ИЛИ и первым входом четвертого элемента ИШ каждого блока границ счета, -с нулезьм входом второго триггера каждого блока границ счета, выход генератора импульсов соединен с вторьм входом первого элемента И, с первыми входами третьего и четвертого элементов И и через элемент задержки с первьми входами пятого, шестого и седьмого элементов И, выход первого элемента И соединен с единичным входом второго триггера, единичный и нулевой выходы которого сбединены с вторыми входами соответственно седьмого и шестого элементов И, выходы шестого и седьмого элементов И соединены соответственно с нулевым и единичным входами третьего триггера, единичный и нулевой выходы которого соединены с в .орыми входами соответственно четвертого и третьего элементов И, выходы которых соединены соответственно с единичным и нулевым входами четвертого триггера, выход четвертого элемента И соединен со.счетным входом счетчика, единичный выходы первого и четвертого триггеров соединены соответственно с вторым и третьим входами пятого элемента И, выход которого соединен с тактовым входом второго дешифратора первого блока границ счета, выход второго элемента И соединен с первым входом второго элемента И всех блоков границ счета, вход опроса состояния счетчика устройства соединен с третьим информационным входом первого дешифратора всех блоков границ счета, выход четвертого элемента ИЛИ i-ro блока границ счета соединен с нулевым входом первого триггера i-ro блока.границ счета, первый выход первого депгафратора 1-го блока границ счета через элемент задержки соединен с вторым входом четвертого элемента ШШ, первым входом пятого элемента ИЛИ, с входом сброса одноразрядного счетчика i-roблока границ счета, выход второго элемента ИЛИ i-ro блока границ .счета соединен со счетным входом одноразрядного счетчика, третий выход первого дешифратора каждого блока .границ счета соединен с единичным вхо-. дом второго триггера, информационный вход которого соединен с шиной нулевого потенциала, единичный и нулевой выходы второго триггера i-ro блока границ счета соединены соответственно с первым и вторым информационными входами второго дешифратора, первый и второй выходы которого соединены соответственно с вторым входом пятого элемента ИЛИ i-ro блока гра-ниц счета и с тактовым входом второго дешифратора (i+1)-ro блока границ счета, выход пятого элемента ИЛИ i-го блока границ счета соединен с тактовым входом второго триггера i-ro блока границ счета, первьй выход второго дешифратора i-ro блока границ

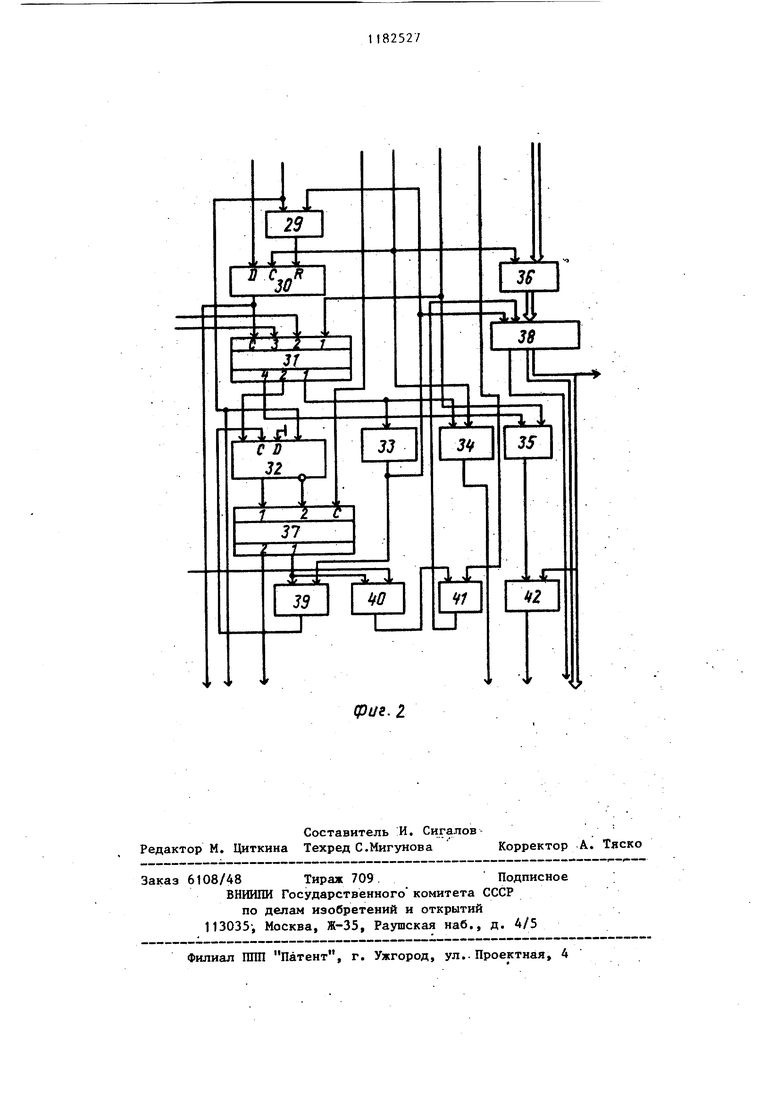

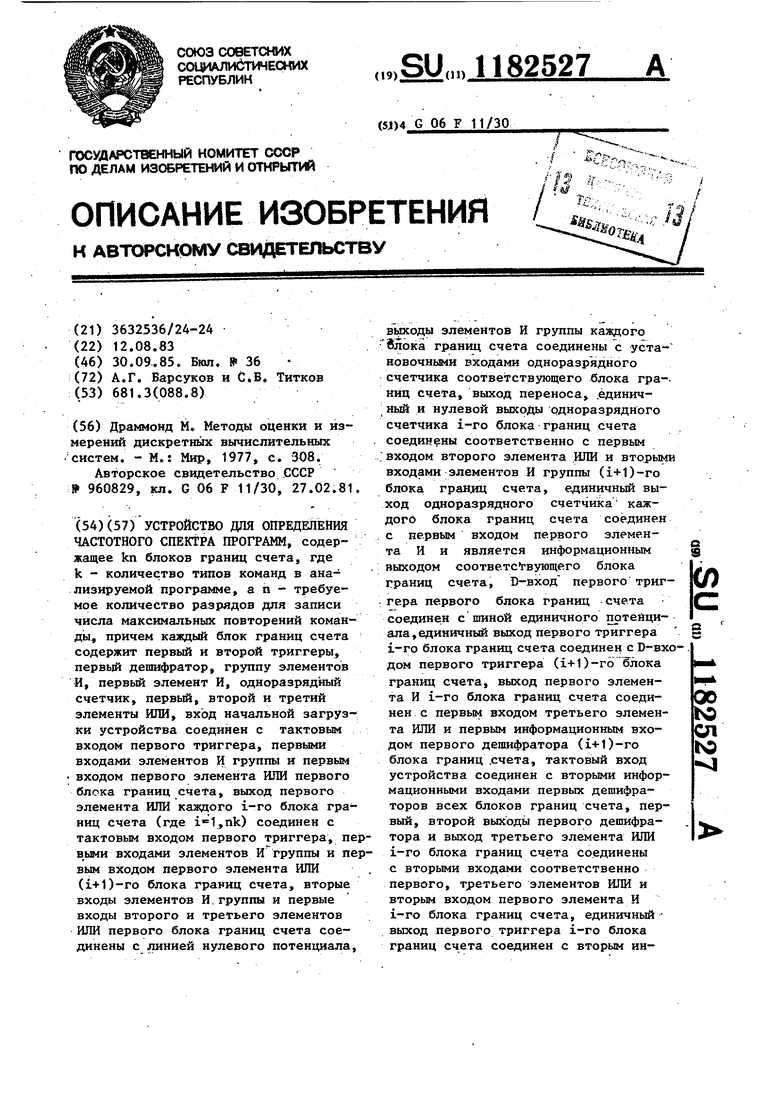

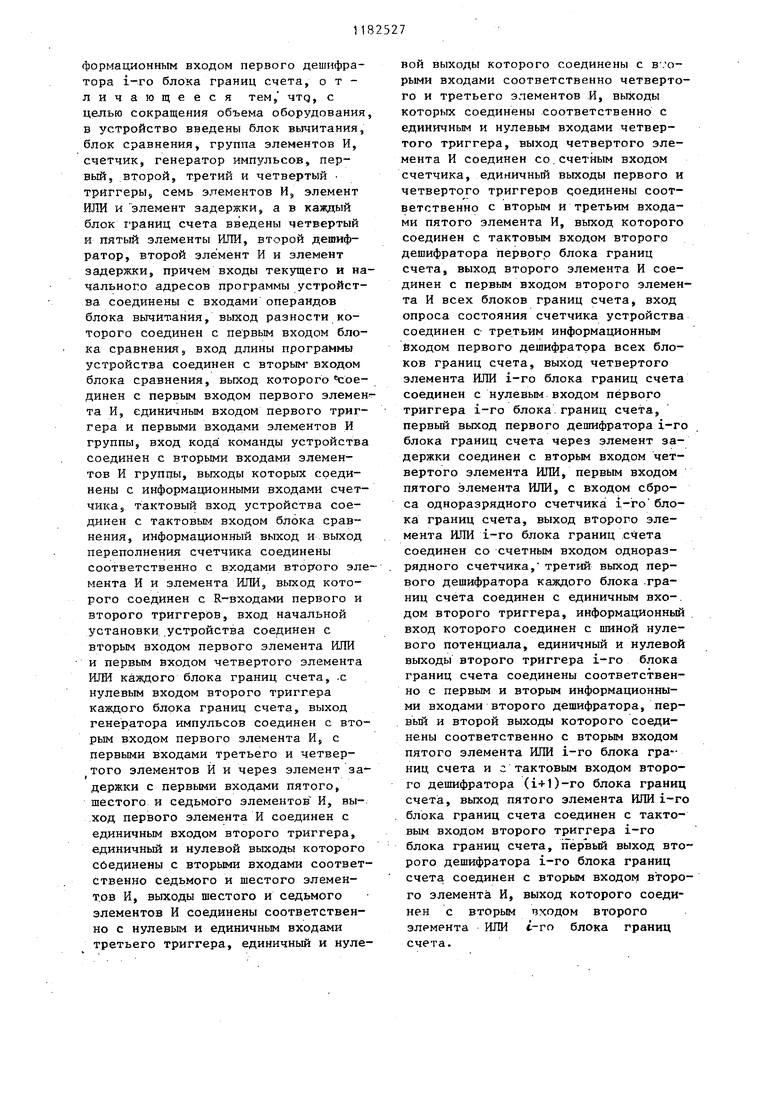

счета соединен с вторым входом второго элемента И, выход которого соединен с вторым 13ХОДОМ второго элемента ИЛИ с-го блока границ счета. Изобретение относится к вычислительной технике и может быть использовано в аппаратных и гибридных мониторах для определения статистических характеристик работы программ. Целью изобретения является сокра.щение объема оборудования. На фиг. 1 приведена структурная схема устройства для определения частотного спектра программ; на фиг. 2 - функциональная схема блока границ счета. Устройство содержит (фиг. 1) блок вычитания 1, блок сравнения 2, группу элементов ИЗ, счетчик 4, второй элемент И 5, элемент ИЛИ 6, первый триггер 7, пятый элемент И 8 генератор ийпульсов 9, первьй элемент И 10, элемент задержки 11, второй триггер 12, шестой 13 и седьмой 14 элементы И, третий триггер 15, третий 16 и четвертый 17 элементы И четвертый триггер 18 п k блоков 19 границ счета, вход 20 кода команды, вход 21 текущего адреса программы, вход 22 начального адреса программы вход 23 длины программы, вход 24 начальной установки, тактовый вход 25 устройства, вход 26 опроса состояния у счетчика устройства, вход 27 начальной загрузки устройства, группу информационных выходов 28 устройства. Блок 19 границ счета содержит (фиг. 2) четвертый элемент ИЛИ 29, первый триггер 30, первый дешифратор 31, второй триггер 32, элемент задержки 33, первый 34 и третий 35 элементы ИЛИ, группу элементов И 36 второй дешифратор 37, одноразрядный счетчик 38, пятый элемент ИЛИ 39 второй элемент И 40, второй элемент И 41, первый элемент И 42. Блок 19 границ счета работает следующим образом.. На подготовительном этапе сигнал с входа 24 начальной установки устройства сбрасывает в ноль второй триггер 32, через четвертый элемент ИЛИ 29 - первый триггер 30 и поступает в следующий блок границ счета. Затем сигнал с входа 27 начальной загрузки.устройства, воздействуя на тактовый вход первого триггера 30, записывает в него с.остояние информа ционного входа. Этот же сигнал стро бирует установку одноразрядного .счетчика 38 через группу элементов И 36. Далее сигнал начальной загрузки через первый элемент ИЛИ 34 поступает в следующий блок границ счета на аналогичный вход. На рабочем этапе по сигналу с тактового входа 25 устройства, поступающему на второй информационный вход первого дешифратора 31, и при наличии единицы на его тактовом входе возбуждается третий выход дешифратора 31, что приводит к установке в единичное состояние второго триггера 32. Сигнал, поступающий на тактовый вход второго деншфратора 37, расшифровывает .состояние второго триггера 32. Если он установлен в единицу, то сигнал с первого выхода второго дешифратора 37 череэ пятый элемент ИЛИ 39 поступает на тактовый вход второго триггера 32 и переводит его в нулевое состояние по своему заднему фронту. Этот же сигнал при наличии единищл на первом входе второго элемента И 40 проходит через второй элемент ИЛИ 41 на счетный вход одноразрядного счетчика 38. Эта ситуация в блоке границ счета возникает в том случае если в нем хранится младший разряд математического счетчика обрабатываемой в данном такте команды. Иначе при нулевом состоянии второго триггера 32 возникает сигнал на втором выходе второго дешифратора 37, который поступает на соответствующий вход следующего блока границ счета. Таким образом, если данный блок не является границей MaTeMatH4ecKoro счетчика или не принадлежит математическому счетчику обрабатываемой в данном такте команды, то его состояние не меняется. Сигнал с входа 26 опроса состояния счетчика устройства поступает на третий информационный вход первого дешифратора 31 и, при наличии единицы в первом триггере 30, возбуждает второй выход дешифратора. Этим сигналом через третий элемент ИЛИ 35 на первом элементе И 42 опрашивается с состояние одноразрядного счетчика 38. Если оно единичное, то сигнал с выхода первого элемента И 42 поступает в следующий блок границ счета на первый информационный вход первого дешифратора 31 и, пройдя третий элемент ИЛИ 35, опрашивает состояние одноразрядного счетчика 38. Если этот блок границ счета оказался младшей границеп другчлч) мптематического счетчика, то имеется возможность переполн ния предыдущего. Поэтому сигнал с п вого выхода первого дешифратора 31, пройдя первый элемент ИЛИ 34, посту пает в последующие блоки для органи зации сдвига на один разряд всех ма тематических счетчиков (аналогично процессу начальной загрузки), а через элемент задержки 33, пятый элемент ИЛИ 39 и четвертый элемент ИЛИ 29 сбрасывает соответственно од норазрядный счетчик 38, второй триг гер 32 и первый триггер 30, Таким образом, математическому счетчику, которому грозило переполнение, будет вьщелен свободный старший разряд. Если -первоначальный сигнал с вых да первого элемента И 42 не встрети в следующем блоке границы математического счетчика и, пройдя третий элемент ИЛИ- 35, обнаружит нулевое состояние одноразрядного счетчика 38, то он закончит свое распространение. Так как опрос состояния прои водится после такта обработки каждой команды, то угроза переполнения может возникнуть только в одном мат матическом всейсовокупное ти. В процессе счета на выходе переноса одноразрядного счетчика 38 появляется сигнал, который поступает на первый вход второго элемента ИЛИ 41 следующего блока границ счета и далее на счетный вход одноразрядного счетчика 38 этого блока. Состояние одноразрядного счетчика 3 по группе информационных выходов пе редается в следующий блок границ счета через группу элементов И 36 этого блока. Причем единичный инфор мационньй выход одноразрядного счет чика является одним из выходов груп пы информационных выходов устройства 28. Устройство для определения частотного спектра программ работает следующим образом. Перед началом работы устройство по сигналу от вычислительной системы по входу 24 начальной установки устройства приводится в исходное состояние. При этом сбрасываются триггеры 7 и 12 через элемент ИЛИ 6 а также первый и второй триггеры всех блоков 19 границ счета. Первый 2/4 же задержанный импульс генерятора импульсов 9 переписывает нуленоо состояние триггера 12 через элемон г И 13 в триггер 15, а следующий основной импульс через элемент И 16 устанавливает в колб триггер 18. На подготовительном этапе по входу 27 начальной загрузки устройства подается k импульсов. Под воздействием этих импульсов логическая единица с информационного входа первого триггера первого блока 19 границ счета распространяется в k блоков 19 границ счета При этом каждому математическому счетчику отводится по одному разряду. Одновременно логический ноль записьгоается в k одноразрядных счетчиков. На рабочем этапе текущий адрес программы по входу 21 поступает в блок вычитания 1, где определяется разность между этим адресом и начальHbw адресом программы с входа 22. Далее поступает сигнал на текстовый вход 25 устройства, который стробирует работу блока сравнения 2 и, поступая в блоки 19 границ счета, устанавливает соответствующие вторые триггеры 32. Если текущая разность меньше длины программы, задаваемой постоянно с входа 23, то на выходе блока 2 сравнения формируется сигнал, разрешающий прием кода команды с входа 20 через группу элементов И 3 в счетчик 4, причем команда принимается на счетчик в обратном коде. Сигнал с выхода блока сравнения устанавливает в единицу триггер 7 устройства и разрешает прохождение импульсов через элемент.И 10. Основной импульс с генератора 9, пройдя элемент И 10, устанавливает в единицу триггер 12, а задержанный переписывает единицу через элемент И 14 в триггер 15. Следующий основной импульс генератора 9, пройдя через элемент И 17, устанавливает в единицу триггер 18 и поступает на счетный вход счетчика 4 в качестве-первого импульса пос-ледовательности поиска входа соответствующего математического счетчика. Единицы с выходов триггеров 7 и 18 создают условие прохождения задержанных импульсов последовательности поиска через элемент И 8 на тактовый вход второго дешифратора 37 первого блока 1.9,1 границ счета.

Предположим, что поступивший код команды равен i. Тогда по i-му основному импульсувсе разрядысчетчика 4 устанавливаются в единичное состояние и появляется сигнал на выходе элемента И 5, свидетельствующий об окончании последовательности поиска.

В это время i-й задержанный импульс последовательности достигает границы i-ro математического счетчика в соответствующемблоке 19 границ счета. Совпадение сигнала с выхода элемента И 5 с i-rt задержанным импульсом последовательности в этом блоке на элементе И 40 дает счетный импульс в младший разряд i-ro математического .счетчика.

Далее (1+1)-й основной импульс последовательности приводит к переполнению счетчика и появлению сигнала переноса из этого счетчика. Сигнал переноса через элемент ИЛИ 6 сбрасывает D ноль триггеры 7 и 12, прекращая прохождение задержанных импульсов последовательности поиска. Триггеры 15 и 18 сбрасываются аналогично последовательности начальной установки.

Последним этапом обработки команды является опрос состояния математических счетчиков для предотвращения их переполнения. С этой целью на вход 26 опроса состояния счетчика устройства подается сигнал, действие которого изложено в описании работы блока 19 границ счета.

Следующий такт обработки очередной команды начинается с приходом нового текущего адреса программы, на вход 21, кода команды на вход 20; по тактовому входу 2 устройства.

Устройство завершает свою работ тогда, когда заканчивается выполнение анализируемой программы. В 5 конце работы устройства группа информационных выходов 28 устройства содержит частотный спектр исследуемой программы. При этом Количество выполнений команды с тем или иным

o кодом операции определяется показанием соответствующего математического счетчика, включающего необходимое количество разрядов одноразрядных счетчиков блоков 19 границ счета.

5 Мпадший разряд каждого математического счетчика определяется наличием единицы в первом триггере 30 соответствующего блока 19 границ счета. Так, младшим разрядом первого математического счетчика является одноразрядный счетчик 38 первого блока 19.1 границ счета.

Таким образом, все множество одноразрядных счетчиков, предназначенных

5 для хранения кодов математических счетчиков, динамически перераспределяется в процессе работы устройства. Для идентификации входов в математические счетчики используются в

0 каждом блоке границ счета лишь два триггера: первый и второй. Первый триггер участвует в динамическом перераспределении одноразрядных . счетчиков в процессе работы устройства. Второй триггер необходим для реализации поиска входа в требуемый математический счетчик. Отношение выполняемой команды к анализируемой программе обеспечивается блоком вычитания и сравнения. Это дает возможность- получения частотного спекТра программ при мультипрограммной работе вычислительной системы.

Фиг.1

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство управления конвейерным вычислительным устройством | 1991 |

|

SU1751757A1 |

| Устройство контроля | 1984 |

|

SU1198542A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для контроля выполнения программ | 1985 |

|

SU1307460A1 |

| Устройство для определения профиля программ | 1981 |

|

SU960829A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для сопряжения абонентов с ЦВМ | 1987 |

|

SU1460723A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЧАСТОТНОГО СПЕКТРА ПРОГРАММ, содержащее kn блоков границ счета, где k - количество типов команд в анализируемой программе, an- требуемое количество разрядов для записи числа максимальных повторений команды, причем каждый блок границ счета содержит первый и второй триггеры, первый дешифратор, группу элементов И, первый элемент И, одноразрядный счетчик, первый, второй и третий элементы ШШ, вход начальной загрузки устройства соединен с тактовым входом первого триггера, первь&ш входами элементов И группы и первым входом первого элемента ИЛИ первого блока границ счета, выход первого элемента ИЛИ каждого i-ro блока границ счета (где ,nk) соединен с тактовьм входом первого триггера, перв,ыми входами элементов И группы и первым входом первого элемента ИЛИ (i+1)-ro блока границ счета, вторые входы элементов И.группы и первые входы второго и третьего элементов ШШ первого блока границ счета соединены с линией нулевого потенциала. выходы элементов И группы каждого влока границ счета соединены с установочньми входами одноразрядного счетчика соответствующего блока гра-ниц счета, выход переноса, .ёдинич ный и нулевой выходы одноразрядного счетчика i-ro блока границ счета соединены соответственно с первым .входом второго элемента ИЛИ и вторыми входами элементов И группы (i+1)-ro блока грациц счета, единичный выход одноразрядного счетчика каждого блока границ счета соединен с первым входом первого элемента И и является информационным выходом соответствующего блока границ счета, D-вход первого триггера первого блока границ счета соединен с шиной единичного потенциала , единичный выход первого триггера i-ro блока границ счета соединен с D-BXO- . дом первого триггера

| Драммонд М | |||

| Методы оценки и измерений дискретных вычислительных систем | |||

| - М.: Мир, 1977, с | |||

| Распределительный механизм для паровых машин | 1921 |

|

SU308A1 |

| Устройство для определения профиля программ | 1981 |

|

SU960829A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-30—Публикация

1983-08-12—Подача