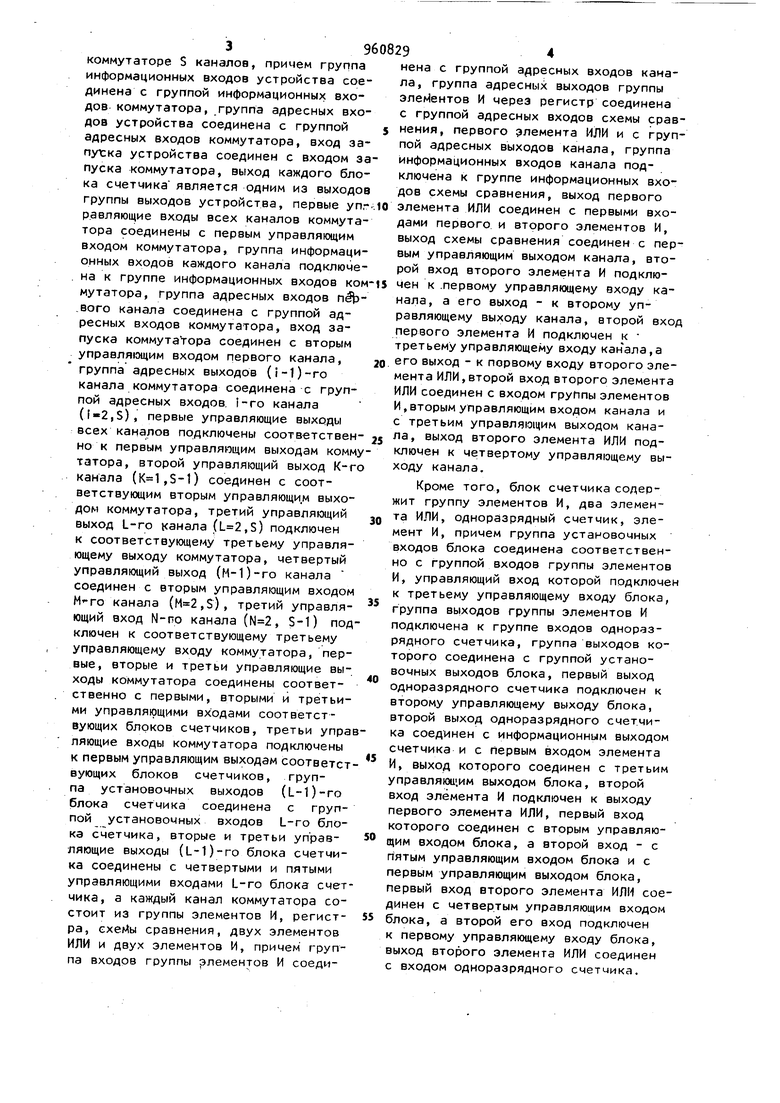

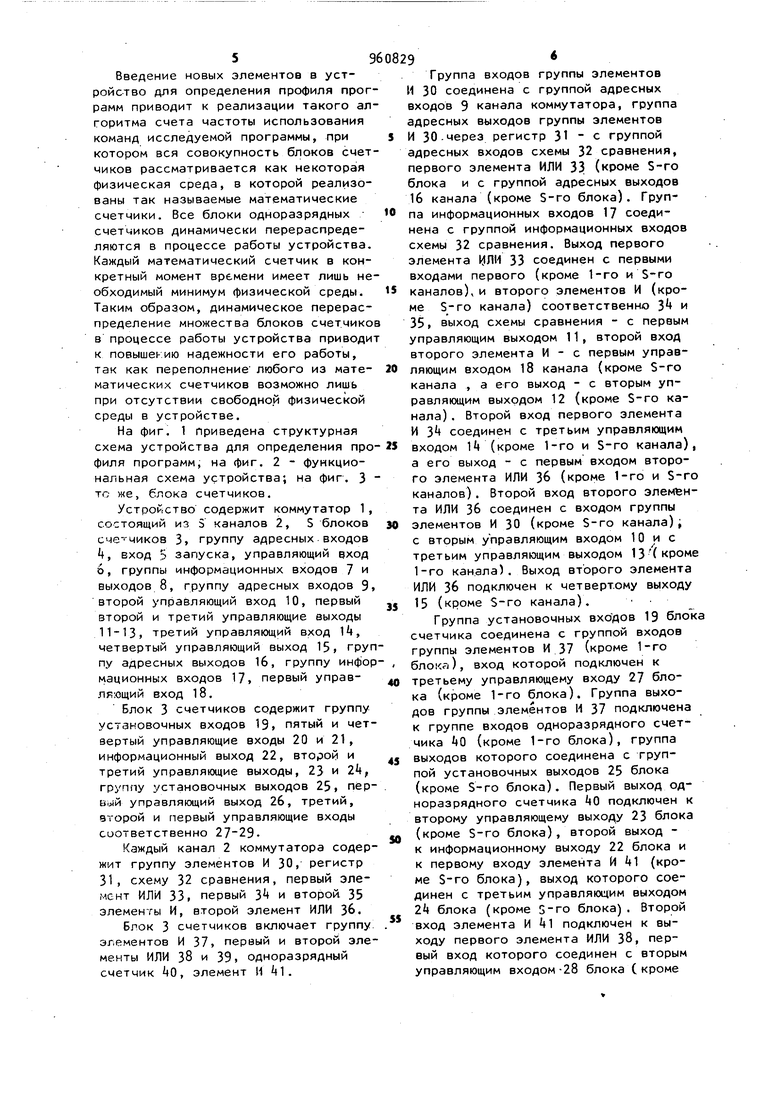

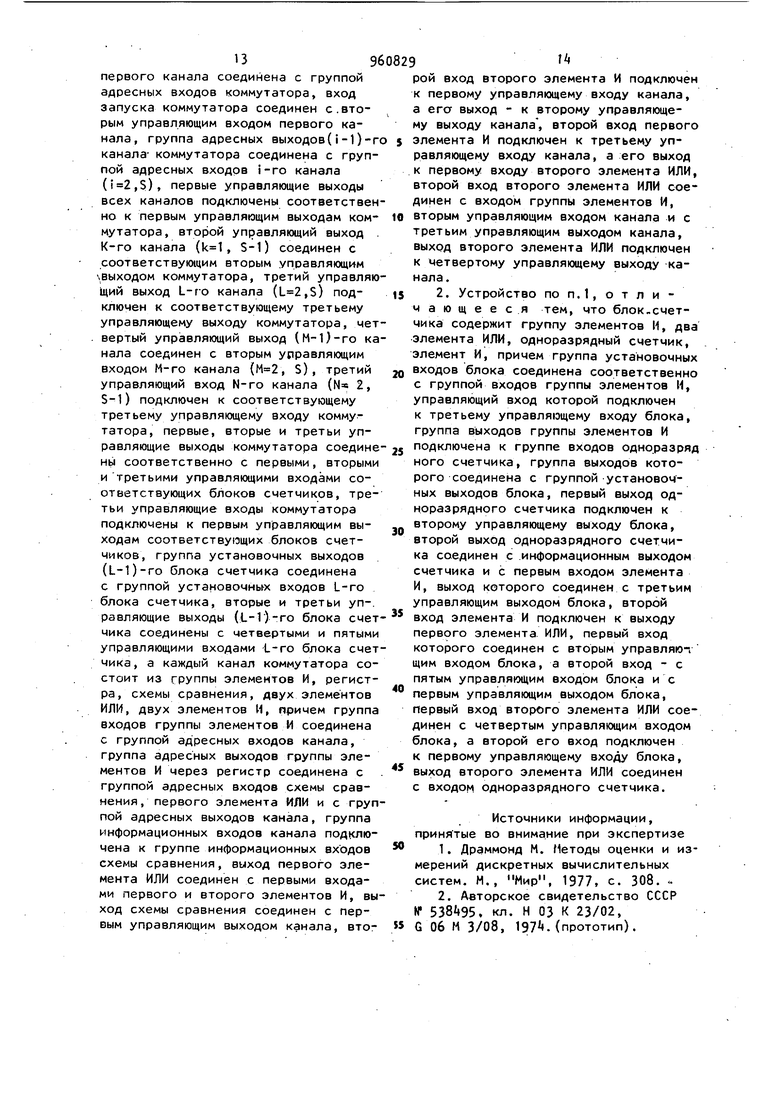

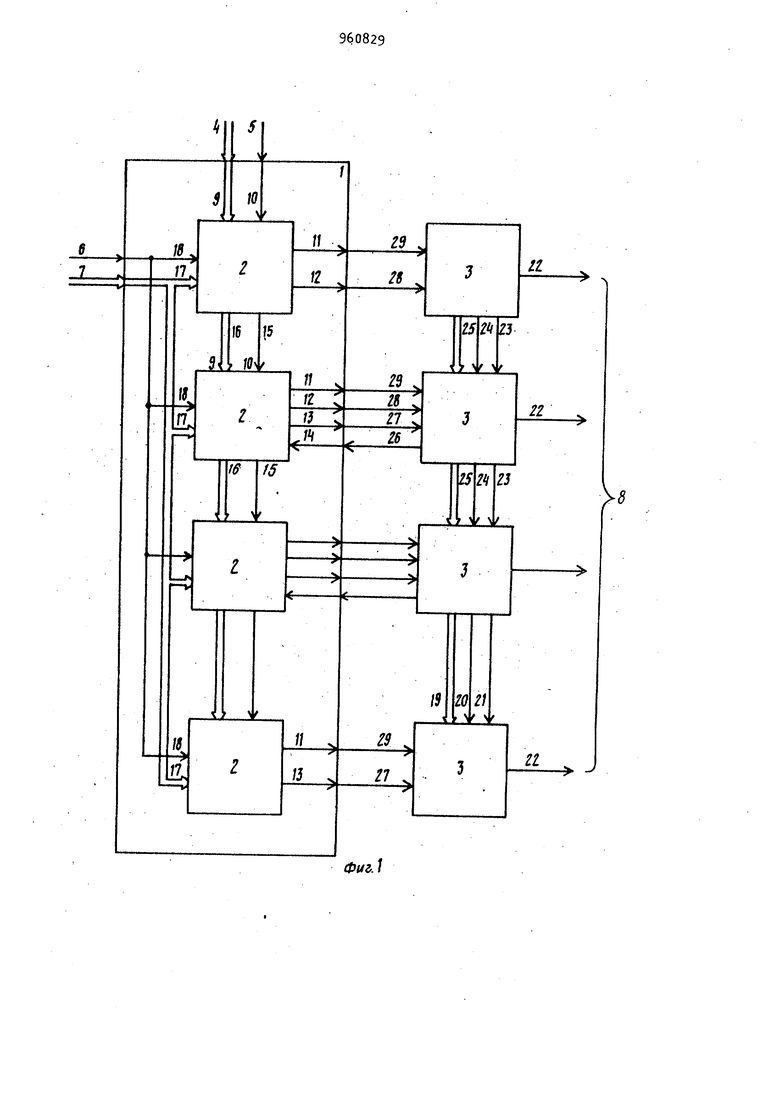

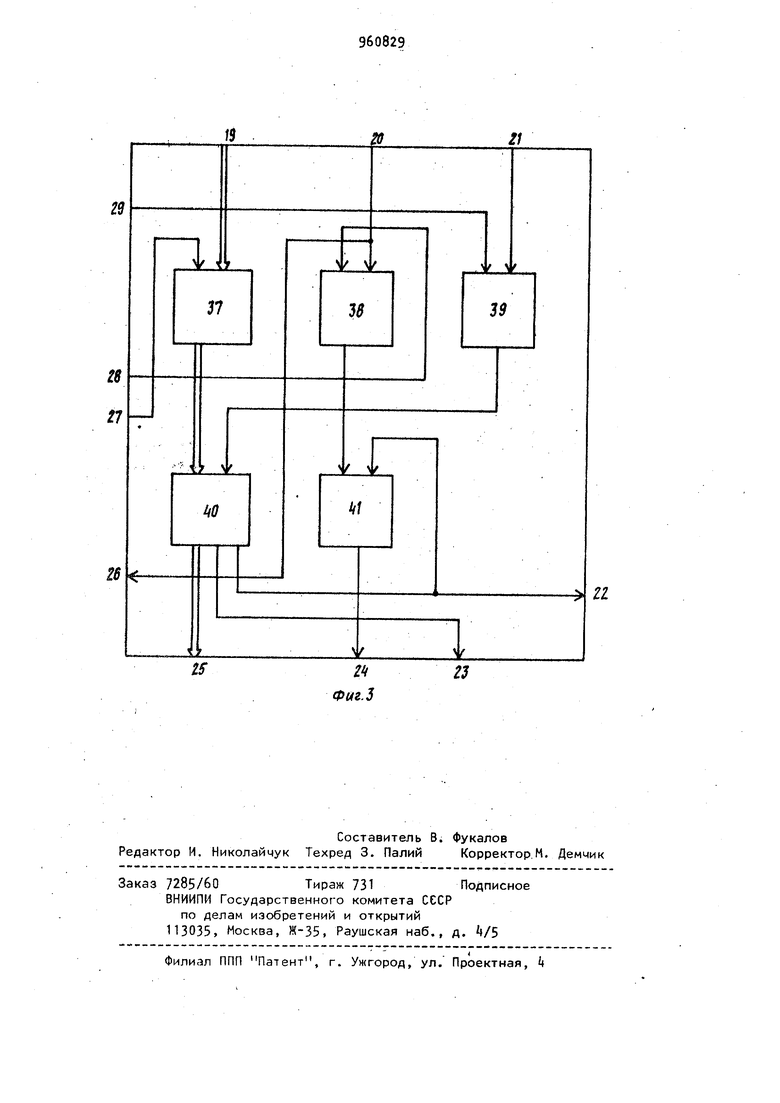

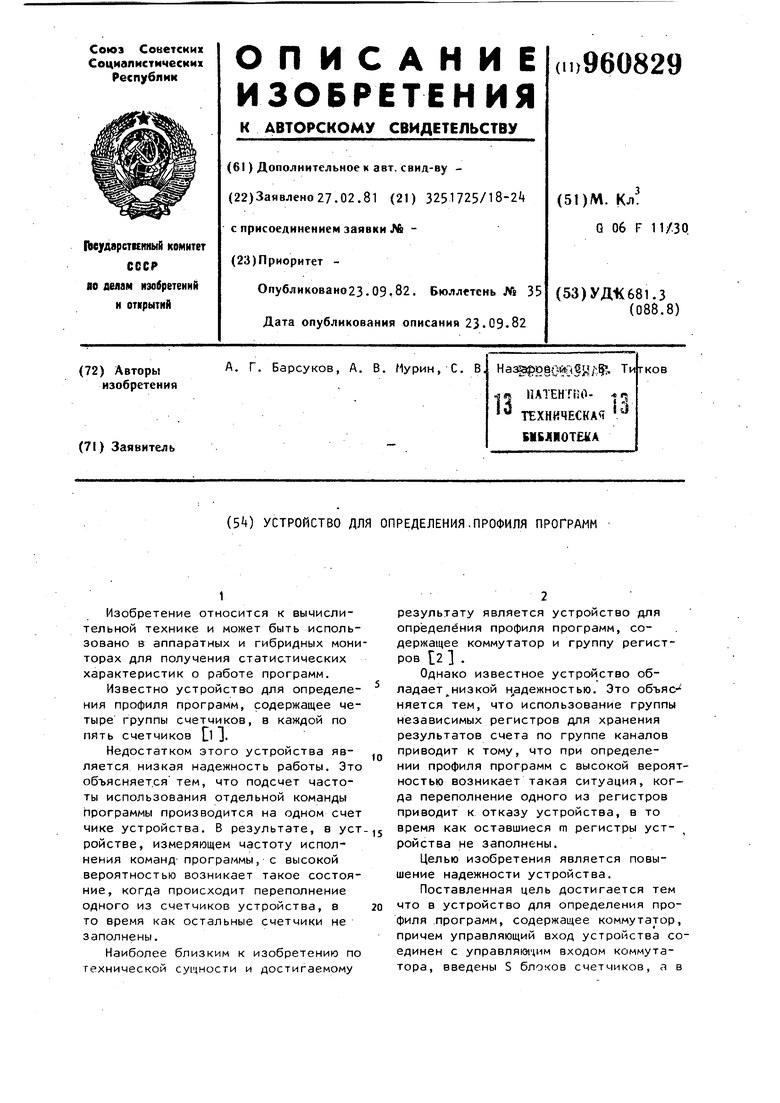

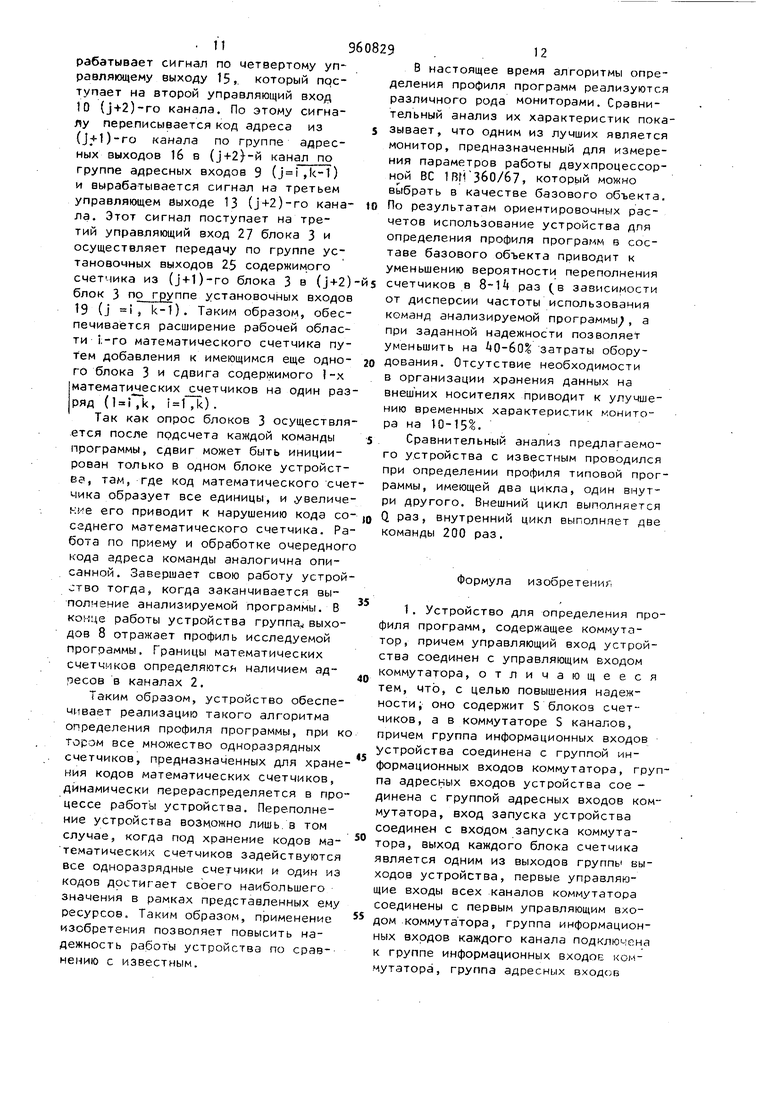

Изобретение относится к вычислительной технике и может быть использовано в аппаратных и гибридных мони торах для получения статистических характеристик о работе программ. Известно устройство для определения профиля программ, содержащее четыре группы счетчиков, в каждой по пять счетчиков fl 3. Недостатком этого устройства является низкая надежность работы. Это объясняется тем, что подсчет частоты использования отдельной команды программы производится на одном счет чике устройства. В результате, в ycT ройстве, измеряющем частоту исполнения команд- программы, с высокой вероятностью возникает такое состояние, когда происходит переполнение одного из счетчиков устройства, в то время как остальные счетчики не заполнены. Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для определения профиля программ, содержащее коммутатор и группу регистров 2 1 . Однако известное устройство обладает низкой н адежностью. Это объясняется тем, что использование группы независимых регистров для хранения результатов счета по группе каналов приводит к тому, что при определении профиля программ с высокой вероятностью возникает такая ситуация, когда переполнение одного из регистров приводит к отказу устройства, в то время как оставшиеся m регистры устройства не заполнены. Целью изобретения является повышение надежности устройства. Поставленная цель достигается тем что в устройство для определения профиля .программ, содержащее коммутатор, причем управляющий вход устройства соединен с управляю1|им входом коммутатора, введены S блоков счетчиков, а в коммутаторе S каналов, причем группа информационных входов устройства соединена с группой информационных входов коммутатора, группа адресных входов устройства соединена с группой адресных входов коммутатора, вход запуска устройства соединен с входом запуска коммутатора, выход каждого блока счетчика является одним из выходов группы выходов устройства, первые упг. равляющие входы всех каналов коммутатора соединены с первым управляющим входом коммутатора, группа информационных входов каждого канала подключена к группе информационных входов коммутатора, группа адресных входов ,вого канала соединена с группой адресных входов коммутатора, вход запуска коммутаУора соединен с вторым управляющим входом первого канала, группа адресных выходов (i-l)-ro канала коммутатора соединена с группой адресных входов, i-ro канала (i«2,S), первые управляющие выходы всех каналов подключены соответствен- 25 но к первым управляющим выходам комм татора, второй управляющий выход К-г канала (,S-t) соединен с соответствующим вторым управляющем выходом коммутатора, третий управляющий выход L-ro канала (,S) подключен к соответствующему третьему управляющему выходу коммутатора, четвертый управляющий выход (М-1)-го канала соединен с вторым управляющим входом Мто канала (,S), третий управляющий вход N-no канала (, S-1) под ключен к соответствующему третьему управляющему входу коммутатора, первые, вторые и третьи управляющие выходы коммутатора соединены соответственно с первыми, вторыми и третьими управляющими входами соответствующих блоков счетчиков, третьи упра ляющие входы коммутатора подключены к первым управляющим выходам соответст вующих блоков счетчиков, группа установочных выходов (L-l)-ro блока счетчика соединена с группой установочных входов L-ro блока счетчика, вторые и третьи управляющие выходы (L-l)-ro блока счетчика соединены с четвертыми и пятыми управляющими входами L-ro блока счет чика, а каждый канал коммутатора состоит из группы элементов И, регистра, схеМы сравнения, двух элементов ИЛИ и двух элементов И, причем группа входов группы элементов И соединена с группой адресных входов канала, группа адресных выходов группы элe eнтoв И через регистр соединена с группой адресных входов схемы сравнения, первого элемента ИЛИ и с группой адресных выходов канала, группа информационных входов канала подключена к группе информационных входов схемы сравнения, выход первого элемента ИЛИ соединен с первыми входами первого, и второго элементов И, выход схемы сравнения соединен с первым управляющим выходом канала, второй вход второго элемента И подключен к .первому управляющему входу канала, а его выход - к второму управляющему выходу канала, второй вход первого элемента И подключен к третьему управляющему входу канала,а его выход - к первому входу второго элемента ИЛИ,второй вход второго элемента ИЛИ соединен с входом группы элементов И,вторым управляющим входом канала и с третьим управляющим выходом канавыход второго элемента ИЛИ подключей к четвертому управляющему выходу канала. Кроме того, блок счетчика содержит группу элементов И, два элемента ИЛИ, одноразрядный счетчик, элемент И, причем группа установочных входов блока соединена соответственно с группой входов группы элементов И, управляющий вход которой подключен к третьему управляющему входу блока, группа выходов группы элементов И подключена к группе входов одноразрядного счетчика, группа выходов которого соединена с группой установочных выходов блока, первый выход одноразрядного счетчика подключен к второму управляющему выходу блока, второй выход одноразрядного счетчика соединен с информационным выходом счетчика и с первым входом элемента И, выход которого соединен с третьим управляющим выходом блока, второй вход элемента И подключен к выходу первого элемента ИЛИ, первый вход которого соединен с вторым управляющим входом блока, а второй вход - с управляющим входом блока и с первым управляющим выходом блока, первый вход второго элемента ИЛИ соединен с четвертым управляющим входом блока, а второй его вход подключен к первому управляющему входу блока, выход второго элемента ИЛИ соединен с входом одноразрядного счет ика. 5 Введение новых элементов в устройство для определения профиля прог рамм приводит к реализации такого ал горитма счета частоты использования команд исследуемой программы, при котором вся совокупность блоков счет чиков рассматривается как некоторая физическая среда, в которой реализованы так называемые математические счетчики. Все блоки одноразрядных счетчиков динамически перераспределяются в процессе работы устройства. Каждый математический счетчик в конкретный момент времени имеет лишь не обходимый минимум физической среды. Таким образом, динамическое перераспределение множества блоков счетчико в процессе работы устройства приводи к повышению надежности его работы, так как переполнение любого из математических счетчиков возможно лишь при отсутствии свободной физической среды в устройстве. На фиг. 1 приведена структурная схема устройства для определения про филя программ, на фиг. 2 - функциональная схема устройства; на фиг. 3 то же, блока счетчиков. Устройство содержит коммутатор 1, состоящий из 5 каналов 2, 5 блоков сче чиков 3, группу адресных.входов , вход 5 запуска, управляющий вход о, группы информационных входов 7 и выходов 8, группу адресных входов 9 второй управляющий вход 10, первый второй и третий управляющие выходы 11-13, третий управляющий вход It, четвертый управляющий выход 15, груп пу адресных выходов 16, группу инфор мационных входов 17, первый управляющий вход 18. Блок 3 счетчиков содержит группу установочных входов 19, пятый и четвертый управляющие входы 20 и 21, информационный выход 22, второй и третий управляющие выходы, 23 и 2, группу установочных выходов 25, первый управляющий выход 26, третий, агорой и первый управляющие входы соответственно 27-29Каждый канал 2 коммутатора содержит группу элементов И 30, регистр 31, схему 32 сравнения, первый элемент ИЛИ 33, первый 3+ и второй 35 элементы И, второй элемент ИЛИ 36. Блок 3 счетчиков включает группу элементов И 37, первый и второй элементы ИЛИ ЗЗ и 39, одноразрядный счетчик 40, элемент И 1. 9 Группа входов группы элементов И 30 соединена с группой адресных входов 9 канала коммутатора, группа адресных выходов группы элементов И 30-через регистр 31 с группой адресных входов схемы 32 сравнения, первого элемента ИЛИ 33 (кроме S-ro блока и с группой адресных выходов 16 канала (кроме 5-го блока). Группа информационных входов 17 соединена с группой информационных входов схемы 32 сравнения. Выход первого элемента ИЛИ 33 соединен с первыми входами первого (кроме 1-го и S-ro каналов), и второго элементов И (кроме S-ro канала) соответственно З и 35, выход схемы сравнения - с первым управляющим выходом 11, второй вход второго элемента И - с первым управляющим входом 18 канала (кроме S-ro канала , а его выход - с вторым управляющим выходом 12 (кроме S-ro канала) . Второй вход первого элемента И соединен с третьим управляющим входом И (кроме 1-го и S-ro канала), а его выход - с первым входом второго элемента ИЛИ 36 (кроме 1-го и S-ro каналов). Второй вход второго элемента ИЛИ 36 соединен с входом группы элементов И 30 (кроме S-ro канала); с вторым управляющим входом 10 и с третьим управляющим выходом 13(кроме 1-го канала). Выход второго элемента ИЛИ Зб подключен к четвертому выходу 15 (кроме S-ro канала). Группа установочных входов 19 блока счетчика соединена с группой входов группы элементов И 37 (кроме 1-го блока), вход которой подключен к третьему управляющему входу 27 блока (кроме 1-го блока). Группа выходов группы элементов И 37 подключена к группе входов одноразрядного счетчика tO (кроме 1-го блока), группа выходов которого соединена с труппой установочных выходов 25 блока (кроме S-ro блока). Первый выход одноразрядного счетчика 0 подключен к второму управляющему выходу 23 блока (кроме S-ro блока), второй выход к информационному выходу 22 блока и к первому входу элемента И 41 (кроме $-го блока), выход которого соединен с третьим управляющим выходом блока (кроме З-го блока) . Второй вход элемента И 1 подключен к выходу первого элемента ИЛИ 38, первый вход которого соединен с вторым управляющим входом-28 блока (кроме §-го блока}, а второй вход - с пятым управляющим входом 20 блока ( кроме 1-го и S-ro блоков) и с первым управляющим выходом 2б блока (кроме 1-го и . 5-го блоков .Первый вход второго элемента ИЛИ 39 соединен с четвертым управляющим входом 21 блока (кроме 1-го блока), а второй его вхо подключен к первому управляющему вхо ду 29 блока. Выход второго элемента ИЛИ 39 соединен с входом одноразрядного счетчика lO. Группа информационных входов 7 устройства для определения профиля программ соединена с группой информационных входов коммутатора 1, груп па адресных входов Ц устройства - с группой адресных входов коммутатора Вход 5 устройства соединен с входом запуска коммутатора 1. Выход каждого блока 3 счетчиков является одним из выходов группы выходов 8 устройства. Управляющие входы всех блоков 2 упра ления соединены с управляющим входом коммутатора 1. Группа информационных входов 17 каждого канала 2 соединена с группой информационных входов коммутатора 1, группа адресных входов 9 первого канала 2-е группой адресных входов коммутатора 1, вход 5 коммутатора 1 с вторым управляющим входом 10 перво канала 2. Группа адресных выходов 1б (i-1)-го. канала 2 соединена с группой адресных.ВХОДОВ 9 i-ro канала2 ( Первые управляющие выходы 11 всех ка налов соединены с первыми управляющим выходами коммутатора 1, вторые управляющие выходы 12 всех каналов, кроме последнего, соединены с вторыми управляющими выходами коммутатора 1 , третьи управляющие выходы 13 всех каналов (кроме первого) - с третьими управляющими выходами коммутатора 1. Четвертый управляющий выход 15, (М-1)-го канала соединен с вторым уп равляющим входом 1.0 М -го канала (,S). Третьи управляющие входы 1 всех каналов (кроме первого ,и последнего) соединены с соответствующими третьими управляющими входами коммутатора 1. Первые, вторые и третьи управляющие выходы коммутатора 1 соединены соответственно с первыми 29, вторыми 28 и третьими 27 управляющими входами соответствующих блоков 3 счетчиков. Третьи управляющие входы коммутатора 1 соединены с первыми управляющими выходами 2б соответствующих блоков 3 счетчиков. Группа установочных выходов 25 (И-1)-го блока 3 счетчиков 3 соединена с группой установочных входов 19 М-го блока 3 счетчиков. Вторые и третьи управляющие выходы соответственно 23 и 2Ц (М-1)-го блока 3 счетчика соединены с четвертыми 21 и пятыми 20 управляющими входами М-го блока счетчика. Канал 2 коммутатора работает следующим образом. На подготовительном этапе по группе адресных входов 9 поступают адреса команд анализируемой программы. Управляющий вход 10 обеспечивает прохождение кода адреса через группу элементов И 30 и фиксацию его в регистре 31- На рабочем этапе схема 32 сравнения осуществляет сравнение кода адреса, хранимого в регистре 31, с кодом адреса, прступающим по группе информационных входов 17- При. совпадении кодов адресов схема 32 сравнения вырабатывает сигнал который поступает на первый управляющий выход 11 канала. Сигналы с первого 18 и с третьего И управляющих входов проходят соответственно на второй управляющий выход 12 и через элемент ИЛИ 36 на четвертый управляющий выход 15 в том случае, если регистр 31 хранит какой-либо код адреса (кроме нулевого, т.е. определяет зход математического счетчика. Блок 3 счетчиков работает следующим образом. В исходном состоянии одноразрядный счетчик АО обнулен. На рабочем этапе на счетный вход счетчика через элемент ИЛИ 39 -по четвертому управляющему входу 21, либо по первому управляющему входу 29 поступают сигналы, которые устанавливают его поочередно При переключении счетчика из состояния 1 в состояние О с первого выхода счетчика 40 вырабатывается сигнал, который поступает на второй управляющий выход 23 блока. Второй выход счетчика kO является единичным выходом счетчика и соединен с инфорт1ационным выходом 22 блока, а также с первым входом схемы И 41. Сигнал на третьем управляющем выходе блока появляется лишь в том случае, если счетчик АО находится в состоянии на втором 28, либо на пятом 20 управляющих входах блока появля996082910

ется сигнал. Через группу устано- щимся в канале на первом управляющем вочных входов 19 по сигналу, посту- выходе 11 канала, вырабатывается си(-

пающему с третьего управляющего входа 27 блока,имеется возможность принять состояние счетчика предыдущего блока 3 в счетчик 0. По группе установочных выходов 25 состояние счетчика 0 передается в последующий блок 3. Устройство для определения профи- 10 ляющему ля программ работает следующим об; разом. Перед началом работы устройство приводится в исходное состояние, которое характеризуется нулевым состоянием регистров 31 и одноразрядных счетчиков . (Цепи установки устройства в исходное состояние не показаны), На подготовительном этапе код адреса команды с группы адресных входов k устройства поступает на группу адресных входов 9 и под воздействием сигнала, поступающего по второму управляющему входу 5 устройства, а затем по второму управляющему входу 10 блока управления, фиксируется в первом канале. Код адреса следующей команды аналогичным образом поступае В канал 2. При этом по сигналу, поступающему с четвертого управляющего аыхода 15 на второй управляющий вход 10, код, ранее присутствовавший в первом канале, поступает с группы ад ресных выходов 16 на группе адресных входов 9 следующего канала 2 и фиксируется в нем. В общем случае по описанной схеме кодами адресов команд заполняется столько К) каналов сколько команд в исследуемой npoi- рамме. Ограничений на порядок еле- дования команд в программе устройств не накладывае1т. Можно отметить, что К « S . Таким образом, результатом подгот вительного этапа является выделение ;.ля каждого математического счетчика по одному блоку одноразрядного счетчика 3. Очевидно, что наличие кода адреса в i-м канале 2 определяет вхо i-ro математического счетчика и коне ( математического счетчика (,K). На рабочем этапе пс группе информационных входов 7 устройства через .группы информационных входов 17 поступает код адреса команды одновременно на все каналы. При совпадении поступившего кода с кодом, хранянал, который поступает на первый управляющий вход 29 блока 3 счетчиков. 5 Допустим, что совпадение произошло в J-M канале. Если предыдущее состояние одноразрядного счетчика в блоке 3 счетчика единичное, возникает сигнал переполнения по второму управвыходу 23 блока 3. который поступает на четвертый управляющий вход 21 (j+l)-ro блока 3-. Затем по первому управляющему входу 6 устройства на первые управляющие входы 18 всех каналов 2 поступает сигнал опроса состояния блоков 3 счетчиков. При наличии кода адреса в канале 2 этот сигнал проходит на второй управляющий выход 12 и поступает на второй управляющий вход 28 блока 3. Блок 3 вырабатывает на третьем управляющему выходе 2 сигнал в том случае, если его счетчик находится в единичном состоянии. Допустим, что j-и блок 3 содержит такой счетчик. Тогда сигнал с третьего управляющего выхода 2 j-ro блока 3 поступает на пятый управляющий вход 20 (j+l)-ro блока 3. Из (j+l)-ro блока 3 всегда вырабатывается в этом случае сигнал по первому управляющему выходу 26 и продолжается анализ счетчика (j+1)-ro блока на хранение единицы.Наличие единицы в счетчике (j+l)-ro блока- также приводит к появлению сигна- ; ла на третьем управляющем выходе 2 (j+1)-ro блока. Процесс опроса состоя ния счетчиков прекращается в том случае, если встретится в каком-либо блоке 3 счетчик в нулевом состоянии. Наиболее интересно с точки зрения логики работы устройства проследить прохождение сигнала с первого управляющего выхода 26 блойа 3 и поступающего на третий управляющий вход k канала. Этот сигнал проходит канал 2 при условии, что он содержит код адреса, т.е. (3+1)-й канал является началом нового математического счетчика. В этом случае получается, что сигнал опросил все блоки 3 предыдущего математического счетчика, которые оказались в состоянии Ч ( иначе не было бы сигнала на входе И (j+l)-ro блока 3) и обнаружил начало следующего математического счетчика. Только в этом случае в ответ на поступивший сигнал ()-й канал 2 вы. n рабатывает сигнал по четвертому управляющему выходу 15,. который nqcтупает на второй управляющий вход 10 (j+2)-ro канала. По этому сигналу переписывается код адреса из {j4-1)-ro канала по группе адресных выходов 16 в (j+2Hrt канал по группе адресных входов 9 (j i,) и вырабатывается сигнал на третьем управляющем выходе 13 (j+2)-ro кана ла. Этот сигнал поступает на третий управляющий вход 27 блока 3 и осуществляет передачу по группе установочных выходов 25 содержимого счетчика из (j+l)-ro блока 3 в (+2 блок 3 по группе установочных входов 19 (j 9 k-1). Таким образом, обеспечива ется расширение рабочей области 1:-го математического счетчика путем добавления к имеющимся еще одного блока 3 и сдвига содержимого 1-х математических счетчиков на один разряд (1 1 ,k, i 1 Л) . Так как опрос блоков 3 осуществляется после подсчета каждой команды программы, сдвиг может быть инициирован только в одном блоке устройстве, там, где код математического счет чика образует все единицы, и увеличекие его приводит к нарушению кода со сзднего математического счетчика. Ра бота по приему и обработке очередног кода адреса команды аналогична описанной. Завершает свою работу устрой ство тогда, когда заканчивается выполнение анализируемой программы. В конце работы устройства группа выходов 8 отражает профиль исследуемой программы. Границы математических счетчиков определяются наличием адресов в каналах 2. Таким образом, устройство обеспечивает реализацию такого алгоритма определения профиля программы, при к тором все множество одноразрядных счетчиков, предназначенных для хране ния кодов математических счетчиков, динамически перераспределяется в про цессе работы устройства. Переполнение устройства возможно лишь, в том случае, когда под хранение кодов математических счетчиков задействуются все одноразрядные счетчики и один из кодов достигает своего наибольшего значения в рамках представленных ему ресурсов. Таким образом, применение изобретения позволяет повысить надежность работы устройства по сравнению с известным. 8 настоящее время алгоритмы определения профиля программ реализуются различного рода мониторами. Сравнительный анализ их характеристик показывает, что одним из лучших является монитор, предназначенный для измерения параметров работы двухпроцессорной ВС IRfi ЗбО/б7, который можно выбрать в качестве базового объекта, По результатам ориентировочных расчетов использование устройства для определения профиля программ в составе базового объекта приводит к уменьшению вероятности переполнения счетчиков в 8-1 раз (в зависимости от дисперсии частоты использования команд анализируемой программы, а при заданной надежности позволяет уменьшить на А0-60 затраты оборудования. Отсутствие необходимости в организации хранения данных на внешних носителях приводит к улучшению временных характеристик монитора на 10-15%. ; Сравнительный анализ предлагаемого устройства с известным проводился при определении профиля типовой программы, имеющей два цикла, один внутри другого. Внешний цикл выполняется Q раз, внутренний цикл выполняет две команды 200 раз. Формула изобретения 1. Устройство для определения профиля программ, содержащее коммутатор, причем управляющий вход устройства соединен с управляющим входом коммутатора, отличающееся тем, что, с целью повышения надежности; оно содержит S блокоз счетчиков, а в коммутаторе 5 каналов, причем группа информационных входов устройства соединена с группой информационных входов коммутатора, группа адресных входов устройства сое динена с группой адресных входов коммутатора, вход запуска устройства соединен с входом запуска коммутатора, выход каждого блока счетчика является одним из выходов группы выходов устройства, первые управляющие входы всех каналов коммутатора соединены с первым управляющим входом коммутатора , группа информационных входов каждого канала подключена к группе информационных входов коммутатора, группа адресных входов первого канала соединена с группой адресных входов коммутатора, вход запуска коммутатора соединен с.вторым управляющим входом первого канала, группа адресных выходов(i-l)-r канала- коммутатора соединена с группой адресных входов i-ro канала (2,S), первые управляющие выходы всех каналов подключены соответствен но к первым управляющим выходам коммутатора, второй управляющий выход К-го канала (, S-1) соединен с соответствующим вторым управляющим .выходом коммутатора, третий управляю щий выход L-ro канала (,S) подключен к соответствующему третьему управляющему выходу коммутатора, чет . вертый управляющий выход (М-1)-го ка нала соединен с вторым управляющим входом М-го канала , S), третий управляющий вход N-ro канала (N« 2, S-1) подключен к соответствующему третьему управляющему входу коммутатора, первые, вторые и третьи управляющие выходы коммутатора соедине ны соответственно с первыми, вторыми итретьими управляющими входами соответствующих блоков счетчиков, третьи управляющие входы коммутатора подключены к первым управляющим выходам соответствующих блоков счетчиков, группа установочных выходов (L-l)-ro блока счетчика соединена с группой ycтaнoвoчнь x входов L-ro блока счетчика, вторые и третьи управляющие выходы (L-1)-ro блока счет

чика соединены с четвертыми и пятыми управляющими входами 1-го блока счетчика , а каждый канал коммутатора состоит из группы элементов И, регистра, схемы сравнения, двух элементов ИЛИ, двух элементов И, причем группа входов группы элементов И соединена с группой адресных входов канала, группа адресных выходов группы элементов И через регистр соединена с группой адресных входов схемы сравнения, первого элемента ИЛИ и с группой адресных выходов канала, группа информационных входов канала подключена к группе информационных входов схемы сравнения, выход первого элемента ИЛИ соединен с первыми входами первого и второго элементов И, выход схемы сравнения соединен с первым управляющим выходом канала, втопервого элемента ИЛИ, первый вход которого соединен с вторым управляю-, щим входом блока, а второй вход - с пятым управляющим входом блока и с

первым управляющим выходом блока, первый вход второго элемента ИЛИ соединен с четвертым управляющим входом блока, а второй его вход подключен к первому управляющему входу блока,

выход второго элемента ИЛИ соединен с входом одноразрядного счетчика.

Источники информации, принятые во внимание при экспертизе

1.Драммонд М., Методы оценки и измерений дискретных вычислительных систем. М., Мир, 1977, с. 308. 2.Авторское свидетельство СССР « . кл. Н 03 К 23/02,

G 06 М 3/08, 197.(прототип). рой вход второго элемента И подключен к первому управляющему входу канала, а era выход - к второму управляющему выходу канала, второй вход первого элемента И подключен к третьему управляющему входу канала, а его выход к первому входу второго элемента ИЛИ, второй вход второго элемента ИЛИ соединен с входом группы элементов И, вторым управляющим входом канала и с третьим управляющим выходом канала, выход второго элемента ИЛИ подключен к четвертому управляющему выходу канала. 2. Устройство по п.1, о т л и чающееся тем, что блок.счетчика содержит группу элементов И, два элемента ИЛИ, одноразрядный счетчик, элемент И, причем группа установочных входов блока соединена соответственно с группой входов группы элементов И, управляющий вход которой подключен к третьему управляющему входу блока, группа выходов группы элементов И подключена к группе входов одноразряд ного счетчика, группа выходов которого соединена с группой установочных выходов блока, первый выход одноразрядного счетчика подключен к второму управляющему выходу блока, второй выход одноразрядного счетчика соединен с информационным выходом счетчика и с первым входом элемента И, выход которого соединен с третьим управляющим выходом блока, второй вход элемента И подключен к выходу

16

IS

Фнг.2

te П

| название | год | авторы | номер документа |

|---|---|---|---|

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Система для выполнения команд десятичной арифметики табличным способом | 1981 |

|

SU1027731A1 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1999 |

|

RU2152685C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

| Запоминающее устройство | 1980 |

|

SU928408A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для реализации быстрого преобразования Фурье при многоканальной обработке информации | 1983 |

|

SU1124324A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

16

г$

Фаг. 5

11

гч

Авторы

Даты

1982-09-23—Публикация

1981-02-27—Подача