1

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных и управляющих системах для контроля выполнения программ.

Цель изобретения - сокращение аппаратурных затрат.

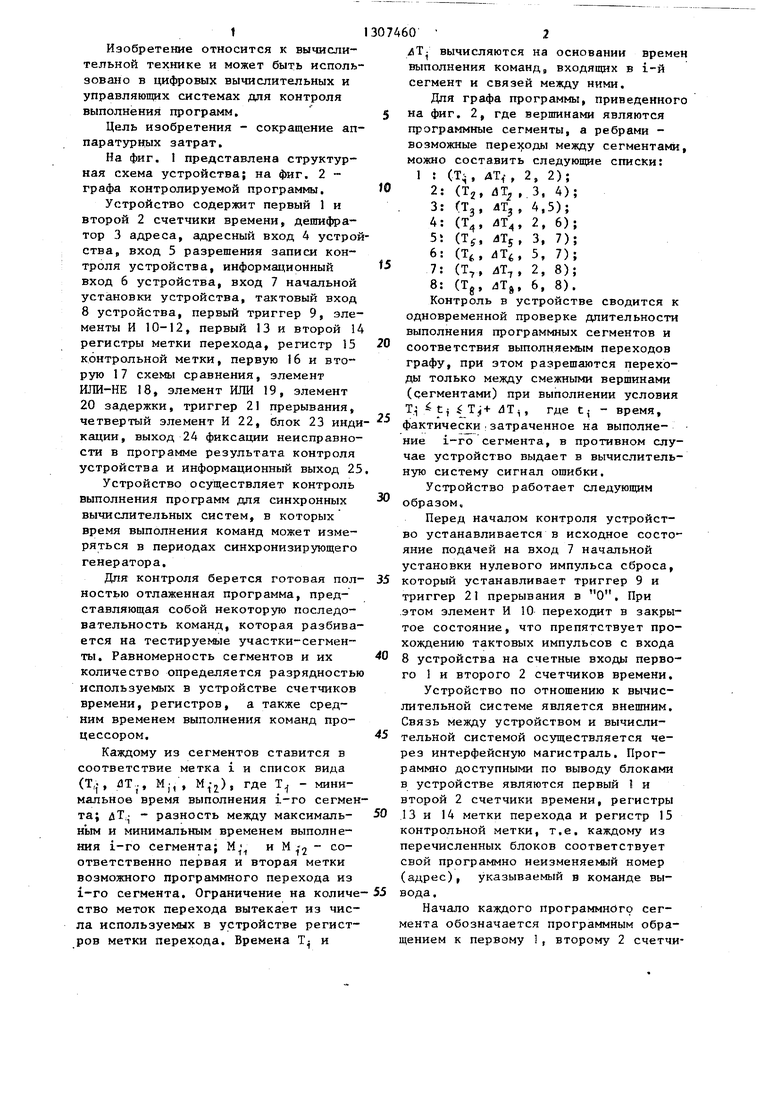

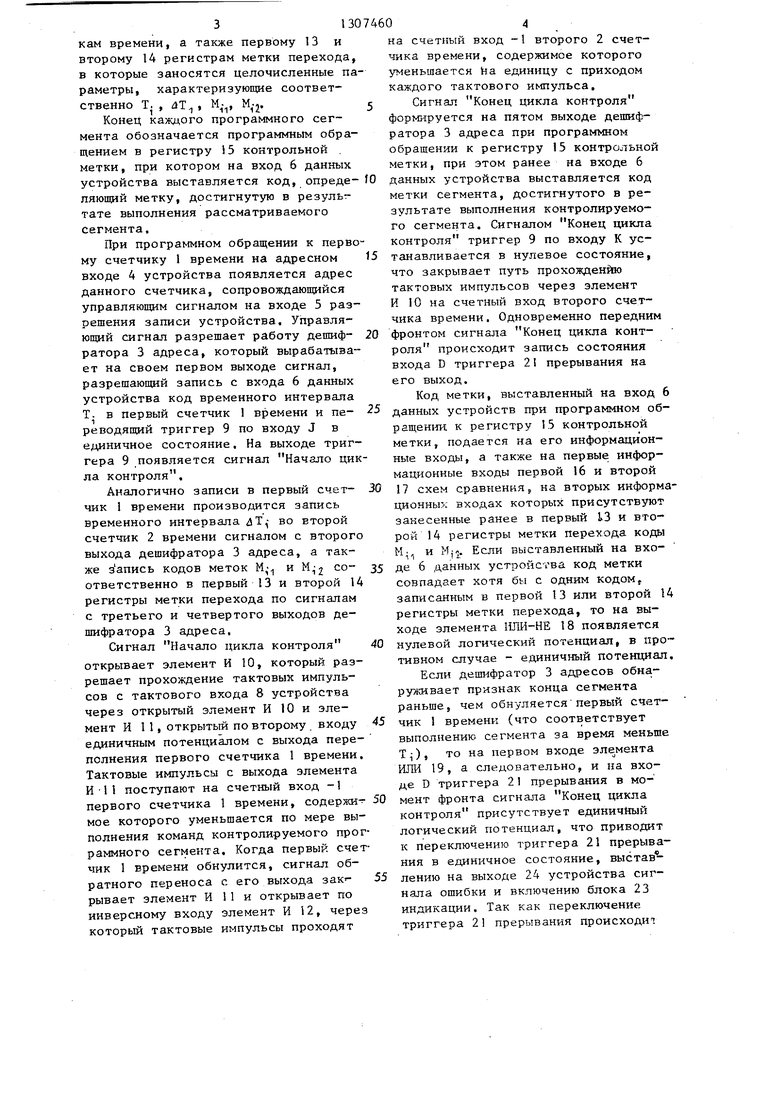

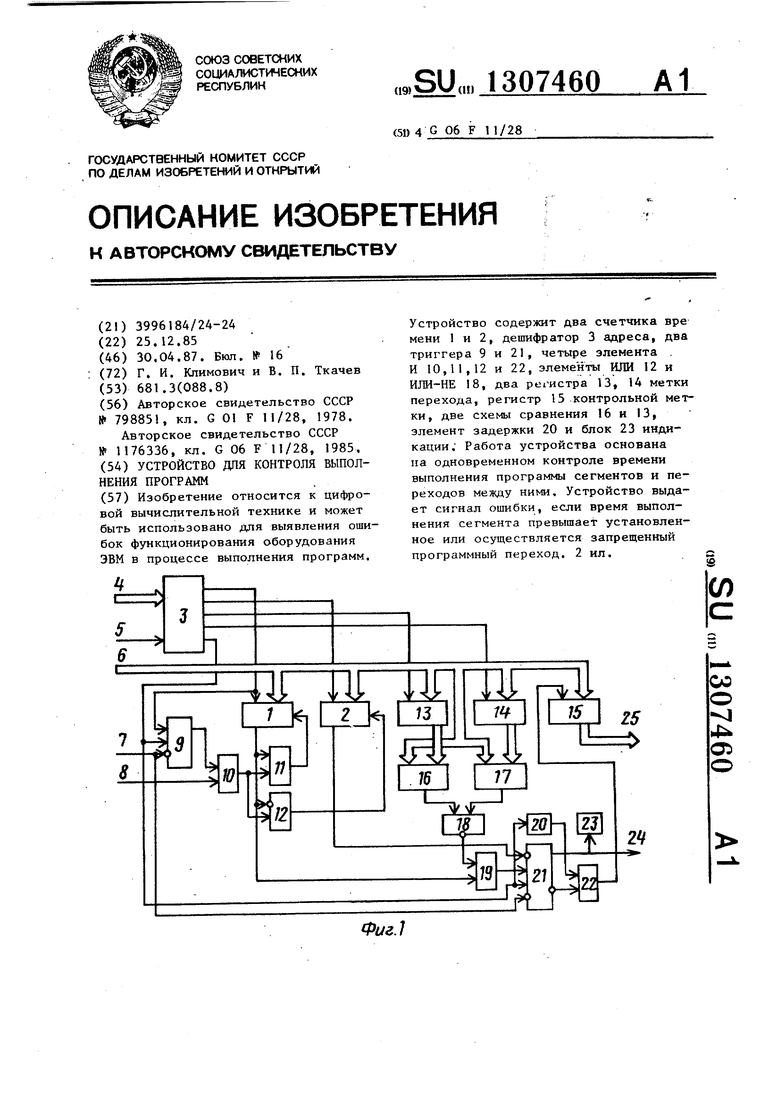

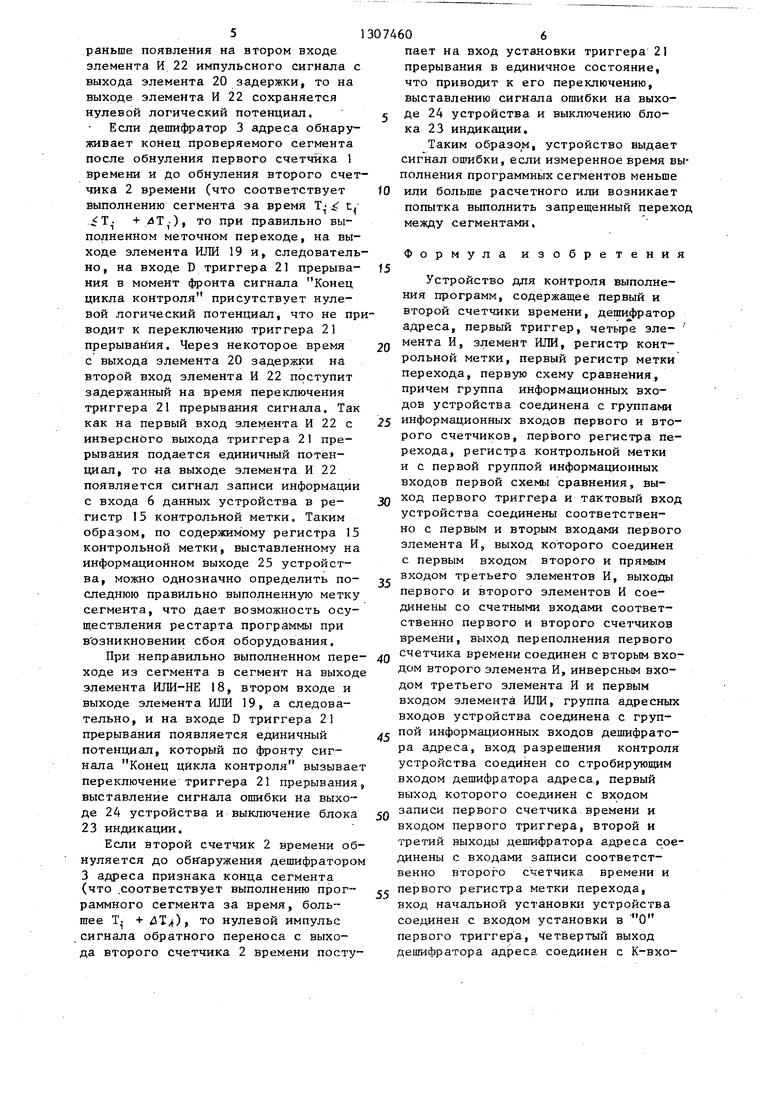

На фиг. 1 представлена структурная схема устройства; на фиг. 2 графа контролируемой программы.

Устройство содержит первый 1 и второй 2 счетчики времени, дешифратор 3 адреса, адресный вход 4 устройства, вход 5 разрешения записи контроля устройства, информационный вход 6 устройства, вход 7 начальной установки устройства, тактовый вход 8 устройства, первый триггер 9, элементы И 10-12, первый 13 и второй 14 регистры метки перехода, регистр 15 контрольной метки, первую 16 и вторую 17 схемы сравнения, элемент ИЛИ-НЕ 18, элемент ИЛИ 19, элемент 20 задержки, триггер 21 прерывания, четвертый элемент И 22, блок 23 индикации, выход 24 фиксации неисправности в программе результата контроля устройства и информационный выход 25

Устройство осуществляет контроль выполнения программ для синхронных вычислительных систем, в которых время выполнения команд может измеряться в периодах синхронизирующего генератора.

Для контроля берется готовая полностью отлаженная программа, представляющая собой некоторую последовательность команд, которая разбивается на тестируе1Ф1е участки-сегмен ты. Равномерность сегментов и их количество определяется разрядностью используемых в устройстве счетчиков времени, регистров, а также средним временем выполнения команд процессором.

Каждому из сегментов ставится в соответствие метка i и список вида (T,j, йТ., Mj,, ,,), где Т - минимальное время выполнения i-ro сегмента; dT,.j - разность между максималь- н ым и минимальным временем выполнения i-ro сегмента; и М -j ° ответственно первая и вторая метки возможного программного перехода из i-ro сегмента. Ограничение на количество меток перехода вытекает из числа используемых в устройстве регистров метки перехода. Времена Т и

07460 2

Т- вычисляются на основании времен выполнения команд, входящих в i-й сегмент и связей между ними.

Для графа программы, приведенного 5 на фиг. 2, где вершинами являются программные сегменты, а ребрами - возможные переходы между сегментами, можно составить следующие списки:

1 : (Тц, ДТ,-, 2, 2); О 2: (Тг, йТ . 3. 4); 3: (Тд, ЛТ, 4,5); 4: (Т, /JT4, 2, 6); 51 (Т,-, alf, 3, 7); 6: (Т, аТ, 5, 7); 5 7: (Т,, 4Т,, 2, В); 8: (Tg, Tj, 6, 8). Контроль в устройстве сводится к одновременной проверке длительности выполнения программных сегментов и 0 соответствия выполняемым переходов графу, при этом разрешаются переходы только между смежными вершинами (сегментами) при выполнении условия Т tj T,j-«- 4Т, где t - время, фактически . затраченное на выполнение i-ro сегмента, в противном случае устройство выдает в вычислительную систему сигнал ошибки.

Устройство работает следующим образом.

Перед началом контроля устройство устанавливается в исходное состояние подачей на вход 7 начальной установки нулевого импульса сброса, 35 который устанавливает триггер 9 и триггер 21 прерывания в О. При .этом элемент И 10 переходит в закрытое состояние, что препятствует прохождению тактовых импульсов с входа 8 устройства на счетные входы первого 1 и второго 2 счетчиков времени. Устройство по отношению к вычислительной системе является внешним. Связь между устройством и вычисли- тельной системой осуществляется через интерфейсную магистраль. Прог- paMNfflo доступными по выводу блоками в устройстве являются первый 1 и второй 2 счетчики времени, регистры 0 13 и 14 метки перехода и регистр 15 контрольной метки, т.е. кaждo ry из перечисленных блоков соответствует свой программно неизменяе в 1й номер (адрес), указываемый в команде вы- 5 вода.

Начало каждого программного сегмента обозначается программным обращением к первому 1, второму 2 счетчикам времени, а также первому 13 и второму 14 регистрам метки перехода, в которые заносятся целочисленные параметры, характеризующие соответM.V

M.J.

ственно Т., дт

Конец каждого программного сегмента обозначается программным обращением в регистру 5 контрольной метки, при котором на вход 6 данных

устройства выставляется код, опреде- JO данных устройства выставляется код

ляющии метку, достигнутую в результате выполнения рассматриваемого сегмента.

При программном обращении к первому счетчику 1 времени на адресном входе 4 устройства появляется адрес данного счетчика, сопровождающийся управляющим сигналом на входе 5 разрешения записи устройства. Управляющий сигнал разрешает работу дешиф- ратора 3 адреса, который вырабатывает на своем первом выходе сигнал, разрешающий запись с входа 6 данных устройства код временного интервала Т. в Первый счетчик 1 времени и пе- реводящий триггер 9 по входу J в единичное состояние, На выходе триггера 9 появляется сигнал Начало цикла контроля.

Аналогично записи в первый счетчик 1 времени производится запись временного интервала Т,- во второй счетчик 2 времени сигналом с второго

40

выхода дешифратора 3 адреса, а также з апись кодов меток М,- и со- 35 ответственно в первый 13 и второй 14 регистры метки перехода по сигналам с третьего и четвертого выходов дешифратора 3 адреса.

Сигнал Начало цикла контроля открывает элемент И 10, который разрешает прохождение тактовых импульсов с тактового входа 8 устройства через открытый элемент И 10 и элемент И 11, открытый по второму входу единичным потенциалом с выхода переполнения первого счетчика 1 времени. Тактовые импульсы с выхода элемента И 11 поступают на счетный вход -1

Код метки, выставленный на вхо данных устройств при программном ращешто. к регистру 15 контрольной метки, подается на его информацио ные входы, а также на первые инфо мационные входы первой 16 и второ 17 схем сравнения, на вторых инфо ционных входах которых присутству занесенные ранее в первый 13 и вт рой 14 регистры метки перехода ко М и Mil. Если выставленный на вх де 6 данных устройства код метки совпадает хотя бы с одним кодомf записанным в первой 13 или второй регистры метки перехода, то на вы ходе элемента ЯПИ-НЕ 18 появляетс нулевой логический потенциал, в п тивном случае - единичный потенци

Если дешифратор 3 адресов обна руживает признак конца сегмента раньше, чем обнуляется первый сче 45 чик 1 времени (что соответствует выполнению сегмента за время мень Т), то на первом входе элемента ИЛИ 19, а следовательно, и на вхо де D триггера 2 прерывания в мопервого счетчика 1 времени, содержи- 50 мент фронта сигнала Конец цикла

мое которого уменьшается по мере выполнения команд контролируемого программного сегмента. Когда первый счетчик 1 времени обнулится, сигнал обратного переноса с его выхода 55 рывает элемент И 11 и открывает по инверсному входу элемент И 12, через который тактовые импульсы проходят

на счетный вход -1 второго 2 счетчика времени, содержимое которого уменьшается ha единицу с прихадом каждого тактового импульса.

Сигнал Конец цикла контроля формируется на пятом выходе дешифратора 3 адреса при програмг шом обращении к регистру 15 контрольной метки, при этом ранее на входе 6

5 0 5

0

5

метки сегмента, достигнутого в результате выполнения контролируемого сегмента. Сигналом Конец цикла контроля триггер 9 по входу К устанавливается в нулевое состояние, что закрывает путь прохождению тактовых импульсов через элемент И 10 на счетный вход второго счетчика времени. Одновременно передним фронтом сигнала Конец цикла контроля происходит запись состояния входа D триггера 2 прерывания на его выход.

Код метки, выставленный на вход 6 данных устройств при программном об- ращешто. к регистру 15 контрольной метки, подается на его информационные входы, а также на первые информационные входы первой 16 и второй 17 схем сравнения, на вторых информационных входах которых присутствуют занесенные ранее в первый 13 и второй 14 регистры метки перехода коды М и Mil. Если выставленный на входе 6 данных устройства код метки совпадает хотя бы с одним кодомf записанным в первой 13 или второй 14 регистры метки перехода, то на выходе элемента ЯПИ-НЕ 18 появляется нулевой логический потенциал, в противном случае - единичный потенциал,

Если дешифратор 3 адресов обнаруживает признак конца сегмента раньше, чем обнуляется первый счет- 5 чик 1 времени (что соответствует выполнению сегмента за время меньше Т), то на первом входе элемента ИЛИ 19, а следовательно, и на входе D триггера 2 прерывания в мо0

мент фронта сигнала Конец цикла

контроля присутствует единичный логический потенциал, что приводит к переключению триггера 21 прерывания в единичное состояние, выстав лению на выходе 24 устройства сигнала ошибки и включению блока 23 индикации. Так как переключение триггера 21 прерывания происходит

раньше появления на втором входе элемента И 22 импульсного сигнала с выхода элемента 20 задержки, то на выходе элемента И 22 сохраняется нулевой логический потенциал.

Если дешифратор 3 адреса обнаруживает конец проверяемого сегмента после обнуления первого счетчика 1 времени и до обнуления второго счетчика 2 времени (что соответствует выполнению сегмента за время . + 4Т.), то при правильно выполненном меточном переходе, на выходе элемента ИЛИ 19 и, следовательно, на входе D триггера 21 прерывания в момент фронта сигнала Конец цикла контроля присутствует нулевой логический потенциал, что не приводит к переключению триггера 21 прерывания. Через некоторое время с выхода элемента 20 задержки на второй вход элемента И 22 поступит задержанный на время переключения триггера 21 прерывания сигнала. Так как на первый вход элемента И 22 с инверсного выхода триггера 21 прерывания подается единичный потенциал, то на выходе элемента И 22 появляется сигнал записи информации с входа 6 данных устройства в регистр 15 контрольной метки. Таким образом, по содержимому регистра 15 контрольной метки, выставленному на информационном выходе 25 устройства, можно однозначно определить последнюю правильно выполненную метку сегмента, что дает возможность осуществления рестарта программы при возникновении сбоя оборудования.

При неправильно выполненном переходе из сегмента в сегмент на выходе элемента ИЛИ-НЕ 18, втором входе и выходе элемента ИЛИ 19, а следовательно, и на входе D триггера 21 прерывания появляется единичный потенциал, который по фронту сигнала Конец цикла контроля вызывает переключение триггера 21 прерывания выставление сигнала ошибки на выходе 24 устройства и выключение блока 23 индикации.

Если второй счетчик 2 времени обнуляется до обнаружения дешифратором 3 адреса признака конца сегмента (что .соответствует выполнению программного сегмента за время, большее + I,f) то нулевой импульс сигнала обратного переноса с выхода второго счетчика 2 времени поступает на вход установки триггера 21 прерывания в единичное состояние, что приводит к его переключению, выставлению сигнала ошибки на выхо- де 24 устройства и выключению блока 23 индикгщии,

Таким образом, устройство выдает сигнал ошибки, если измеренное время выполнения программных сегментов меньше или больше расчетного или возникает попытка выполнить запрещенный переход между сегментами.

Формула изобретения

Устройство для контроля выполнения программ, содержащее первый и второй счетчики времени, дешифратор адреса, первый триггер, четьфе эле-

мента И, элемент ИЛИ, регистр контрольной метки, первый регистр метки перехода, первую схему сравнения, причем группа информационных входов устройства соединена с группами

информационных входов первого и второго счетчиков, первого регистра перехода, регистра контрольной метки и с первой группой информационных входов первой схемы сравнения, выход первого триггера и тактовый вход устройства соединены соответственно с первым и вторым входами первого элемента И, выход которого соединен с первым входом второго и прямым входом третьего элементов И, выходы первого и второго элементов И соединены со счетными входами соответственно первого и второго счетчиков времени, выход переполнения первого

счетчика времени соединен с вторым входом второго элемента И, инверсным входом третьего элемента И и первым входом элемента ИЛИ, группа адресных входов устройства соединена с группой информационных входов дешифратора адреса, вход разрешения контроля устройства соединен со стробирующим входом дешифратора адреса., первый выход которого соединен с входом записи первого счетчика времени и входом первого триггера, второй и третий выходы дешифратора адреса соединены с входами записи соответственно второго счетчика времени и

первого регистра метки перехода, вход начальной установки устройства соединен с входом установки в первого триггера, четвертый выход дешифратора адреса соединен с К-входом первого триггера, выход четвертого элемента И соединен с входом записи регистра контрольной метки, группа информационных выходов которого является группой выходов результата контроля устройства, группа информационных выходов первого регистра метки перехода соединена с второй группой информационных входов первой схемы сравнения, отличающееся тем, что, с целью сокращения амплитудных затрат, в него введены второй регистр метки перехода, вторая схема сравнения, элемент ИЛИ-НЕ, элемент задержки и второй триггер, причем вход начальной установки устройства и выход переполнения второго счетчика соединены соответственно с нулевым и единичным входами второго триггера, группа информационных входов устройства соединена с первой группой входов второй схемы сравнения и группо

информационных входов второго регистра метки перехода, пять1й выход дешифратора адреса соединен с входом записи второго регистра метки перехода, группа выходов которого соедине на с второй группой второй схемы сравнения, выходы равенства первой и второй схем сравнения соединены с первым и вторым входами элемента

ИЛИ-НЕ, выход которого соединен с

вторым входом элемента ИЛИ, выход которого соединен с информационным входом второго триггера, первый выход деши чратора адреса соединен с

та;ктовым входом второго триггера и через элемент задержки - с первым входом четвертого элемента И, инверсный выход второго триггера соединен с вторым входом четвертого элемента

И, прямой выход второго триггера является выходом фиксации неисправности в программе устройства.

Составитель И. Сигалов Редактор Л. Пчолинская Техред Л.Олейник Корректор А Ильин

Заказ 1634749Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1988 |

|

SU1529226A1 |

| Устройство для контроля времени выполнения программ | 1984 |

|

SU1176336A1 |

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1619280A1 |

| Устройство для контроля времени выполнения программ | 1989 |

|

SU1693609A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Устройство для программного управления | 1990 |

|

SU1716482A1 |

| Устройство для отладки микроЭВМ | 1989 |

|

SU1677708A1 |

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1587514A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для выявления ошибок функционирования оборудования ЭВМ в процессе выполнения программ. Устройство содержит два счетчика вре мени 1 и 2, дешифратор 3 адреса, два триггера 9 и 21, четыре элемента , И 10,11,12 и 22, элементы ИЛИ 12 и ИЛИ-НЕ 18, два регистра 13, 14 метки перехода, регистр 15 контрольной метки, две схемы сравнения 16 и 13, элемент задержки 20 и блок 23 индикации; Работа устройства основана па одновременном контроле времени выполнения программы сегментов и переходов между ними. Устройство выдает сигнал ошибки, если время выполнения сегмента превышает установленное или осуществляется запрещенный программный переход. 2 ил. (Л ОО о --J о:) о Фиг.1

| Устройство для контроля времениВыпОлНЕНия пРОгРАММ | 1978 |

|

SU798851A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля времени выполнения программ | 1984 |

|

SU1176336A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-30—Публикация

1985-12-25—Подача